Fターム[4M104DD35]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | ビームによるもの (209)

Fターム[4M104DD35]の下位に属するFターム

イオンプレーティング、イオンビーム蒸着 (97)

Fターム[4M104DD35]に分類される特許

21 - 40 / 112

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

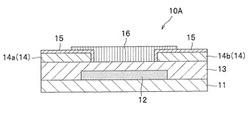

p型有機薄膜トランジスタ、p型有機薄膜トランジスタの製造方法、および、塗布溶液

【課題】電荷注入効率の高いp型有機薄膜トランジスタ、および、金属酸化物を電荷注入層として用いても、金属酸化物が溶解することで電極剥離を起こすことのないp型有機薄膜トランジスタの製造方法、ならびに、この製造方法に用いる塗布溶液を提供する。

【解決手段】p型有機薄膜トランジスタ10Aは、絶縁基板11上に設けられたゲート電極12と、ゲート電極12を被覆して設けられたゲート絶縁層13と、ゲート絶縁層13上に設けられたソース電極14aおよびドレイン電極14bと、ソース電極14aおよびドレイン電極14bの表面に設けられた金属酸化物層15と、ゲート絶縁層13上、かつ金属酸化物層15が形成されたソース電極14aとドレイン電極14bとの間に設けられたp型有機半導体層16と、を備えたことを特徴とする。

(もっと読む)

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

窒化物半導体素子および窒化物半導体素子のパッド電極の製造方法

【課題】p型窒化物半導体層上の透光性電極とn型窒化物半導体層との両方に好適に接続可能な構造のパッド電極を備える窒化物半導体素子を提供する。

【解決手段】窒化物半導体素子10は、基板1上に、n型窒化物半導体層2、活性層3、p型窒化物半導体層4を積層してなり、n型、p型窒化物半導体層2,4にそれぞれ電気的に接続するn側パッド電極7n、p側電極5をさらに備える。p側電極5は、p型窒化物半導体層4上に形成された導電性酸化物からなる透光性電極6と、透光性電極6上の一部の領域に形成されたp側パッド電極7pとからなる。そして、n側パッド電極7nおよびp側パッド電極7pは、n型窒化物半導体層2および透光性電極6のそれぞれに接触する側から、Cr層71a、Pt層71b、Ru層72、Au層73を積層してなり、Cr層71aの厚さは1nm以上9nm未満であることを特徴とする。

(もっと読む)

ハースライナーカバー交換機構

【課題】成膜装置の稼働率と被処理物の処理効率を向上させることができるハースライナーカバー交換機構を提供する。

【解決手段】小径孔16Bと大径孔16Aとで構成された鍵穴状の穴16が形成された鍔部10Bを有し成膜装置のハース14の上部に設けられるハースライナーカバー10を交換するハースライナーカバー交換機構であって、垂直方向に移動可能となり、かつ垂直方向に延びる軸30の軸回りに回転可能になるハンド36を有し、ハンド36は穴16に引っ掛けてハースライナーカバー10を保持する保持部38を備え、ハンド36が軸の軸回りに回転するときの回転方向の接線は小径孔16Bから大径孔16Aに延びる穴16の中心線と一致し、保持部38が穴16に挿入された状態でハンド36が軸30の軸回りに回転することにより保持部38と穴16が係合する。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体発光素子およびその製造方法

【課題】 光取出し側の電極部である上側電極部と、この電極部と対になる電極部である中間電極部とを適切な位置関係で配設することにより、大電流印加時の発光効率を維持させた半導体発光素子およびその製造方法を提供する。

【解決手段】 支持基板の上面側に、中間電極部を含む中間層、第2導電型半導体層、活性層、第1導電型半導体層および上側電極部を順次具え、支持基板の下面側に下側電極層を具える半導体発光素子であって、前記中間電極部を互いの中間電極部間の間隔が50μm以上100μm以下の均等に分散した島状または等間隔の縞状、格子状かつ上面から見た中間電極部の第2導電型半導体層に対する面積率が3〜9%となるように配置することにより、大電流での使用時でも発光効率の高い半導体発光素子を提供することができる。

(もっと読む)

半導体装置の製造装置および半導体装置の製造方法

【課題】コンタクト抵抗の増加を抑制した半導体装置の製造装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造装置100aは、エピタキシャル層形成装置110と、電極形成装置150と、接続部120とを備えている。エピタキシャル層形成装置110は、基板上にエピタキシャル層を形成する。電極形成装置150は、エピタキシャル層に電極を形成する。接続部120は、エピタキシャル層形成装置110と電極形成装置150とを接続し、かつ大気を遮断した雰囲気である。

(もっと読む)

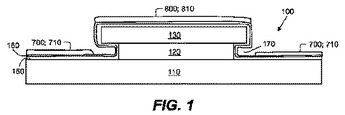

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

蒸着用治具及び蒸着装置

【課題】簡便に蒸着を行うことができる蒸着用治具及び蒸着装置を提供することを目的とする。

【解決手段】本発明にかかる蒸着用治具は、ウエハ4の非蒸着面を覆うハット2を有する。ハット2には、第1凸部2a及び第2凸部2bが設けられる。第1凸部2aは、ウエハ4側におけるハット2の外周部に設けられ、ウエハ4を保持する。第2凸部2bは、ウエハ4とは反対側におけるハット2の外周部に設けられる。このように、ハット2の両面に凸部を設けることにより、簡便に蒸着を行うことができる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタを用いた表示装置及び薄膜トランジスタの製造方法

【課題】工程数の増大を引き起こさずに、遮光層で囲まれた薄膜トランジスタと同等以上の遮光能力を有する薄膜トランジスタおよびそれを用いた表示装置を提供する。

【解決手段】第1のゲート電極2と、第1のゲート電極2を覆う第1のゲート絶縁層3と、第1のゲート絶縁層3の上の半導体層6と、半導体層6の上の第2のゲート絶縁層7と、第2のゲート絶縁層7の上の第2のゲート電極8と、半導体層6に電気的に接続されたドレイン電極5及びソース電極4を有する薄膜トランジスタにおいて、半導体層6がZn、Ga、In、Snのうち少なくとも1種以上を含む非晶質酸化物半導体であり、第1のゲート電極2が下方から半導体層6への光の入射を遮り、第2のゲート電極8が上方から半導体層6への光の入射を遮り、第2のゲート電極8は第1のゲート絶縁層3及び第2のゲート絶縁層7を貫通して第1のゲート電極2と電気的に接続され、少なくとも一方の側方から半導体層6に入射する光を遮る。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応答特性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1および第2の絶縁層13、14と電極層とFP電極17とを備える。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成される。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成される。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成される。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成される。第1の絶縁層13は、第2の絶縁層14を構成する材料の誘電率よりも小さい誘電率を有する材料を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1の絶縁層13と第2の絶縁層14と電極層とFP電極17とを備えている。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成されている。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成されている。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成されている。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成されている。第1の絶縁層13の厚みH13は、第2の絶縁層14の厚みH14よりも大きい。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

発光素子の製造方法

【課題】 ワイヤーボンダビリティが良好な電極を形成することのできる発光素子の製造方法を提供することを目的とする。

【解決手段】 少なくとも、n型半導体結晶と、発光層と、GaまたはInを含みキャリア濃度が1×1017/cm3以上1×1019/cm3以下であるp型半導体結晶とが、この順で形成された半導体結晶の前記p型半導体結晶の表面に、オーミック電極材料として、少なくとも、AuBeを含む層、Ti層、Au層を形成し、その後熱処理を行ってオーミック電極を形成し、その後前記半導体結晶をダイシングする発光素子の製造方法であって、少なくとも、前記形成されたオーミック電極の表面を、ヨウ素ヨウ化カリウム溶液を用いて洗浄する工程を含むことを特徴とする発光素子の製造方法。

(もっと読む)

電界効果型トランジスタ

【課題】チャネル領域を構成する有機半導体材料層と良好なオーミック・コンタクトを形成することができるソース/ドレイン電極を備えた電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12と、ゲート絶縁層13と、ソース/ドレイン電極21と、チャネル領域15を構成する有機半導体材料層14とを備え、ソース/ドレイン電極21は、金属から成る導体部22、及び、導体部22を少なくとも部分的に被覆し、不純物がドーピングされた有機導電材料層23から成り、有機導電材料層23を介して、チャネル領域15と導体部22との間の電気的接続が形成される。

(もっと読む)

ITO電極の形成方法、半導体素子のITO電極及びITO電極を備えた半導体素子

【課題】ITO電極の抵抗をさらに低くすることのできるITO電極の形成方法、及びこれにより形成された半導体素子のITO電極、並びにこのITO電極を備えた半導体素子を提供する。

【解決手段】半導体素子1における酸化インジウムスズ(ITO)の電極50の形成方法において、電極50を、成膜レートにつき1Å/sec以上5Å/sec以下とし、酸素圧力につき0.005Pa以上0.02Pa以下として、電子線蒸着法により形成した後、所定温度で焼成し、良質なITO電極50を得た。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

基板生産物の製造方法、基板生産物、及び半導体デバイス

【課題】異種基板と貼り合わせた窒化物系化合物半導体基板の一部を異種基板から除去することにより窒化物系化合物半導体層を異種基板上に製造する方法において、窒化物系化合物半導体層におけるリーク電流を低減する。

【解決手段】シリコン基板等の支持基板20上に窒化ガリウム層30を有する基板生産物1を製造する方法であって、窒化ガリウム基板10の表面10aにイオン注入を行う工程と、表面10aを洗浄する工程と、表面10aと支持基板20の表面20aとを互いに接合させる工程と、窒化ガリウム基板10のうち表面10aを含む部分を層状に残して他の部分を除去することにより、窒化ガリウム層30を支持基板20上に形成する工程とを含む。表面10aを洗浄する工程の際、洗浄後の表面10aにおけるFe,Cr,Ni,及びSiの密度を合計で1×1018[cm−3]以下とする。

(もっと読む)

酸化亜鉛系半導体素子及びその製造方法

【目的】

p型ZnO系化合物半導体の電極の剥離が生じず高い接着性を有するとともに良好なオーミック接触を有するコンタクト電極の形成方法、当該電極が形成されたZnO系化合物半導体素子及びその製造方法を提供する。

【解決手段】

p型ZnO系半導体層上に、Ni及びCuの少なくとも1つを含むコンタクト金属層を形成する工程と、無酸素雰囲気下で上記コンタクト金属層及びp型ZnO系半導体層の熱処理を行い、コンタクト金属層の表面に金属相の層を残存させるとともに、p型ZnO系半導体層及びコンタクト金属層間の界面にp型ZnO系半導体層の元素及びコンタクト金属層の元素からなる混合層を形成する熱処理工程と、を有する。

(もっと読む)

21 - 40 / 112

[ Back to top ]