Fターム[4M104DD35]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | ビームによるもの (209)

Fターム[4M104DD35]の下位に属するFターム

イオンプレーティング、イオンビーム蒸着 (97)

Fターム[4M104DD35]に分類される特許

41 - 60 / 112

成膜装置

【課題】本発明の目的は、装置の大幅な改造を必要とせずに、所望の物理量を高精度かつ均一に有する薄膜の製造を可能にする薄膜の膜厚制御装置を提供することである。

【解決手段】成膜装置において、成膜中の薄膜の物理量を測定する物理量測定素子と、前記薄膜の物理量と所望の物理量とを比較する比較部と、前記比較部の比較結果に基づいて成膜条件及び/または成膜時間を制御する制御部とを備えることを特徴とする。これにより、所望の物理量を有する薄膜の製造において、所望の物理量を膜内に均一に有する薄膜の製造を可能とすることができる。

(もっと読む)

紫外光発光ダイオード装置及びその製造方法

本発明は、UVLED装置及びその製造方法を提供する。この装置は、基板(1)上に下から上への順で設けられたAlN核層(2、3)、真性AlGaNエピタキシャル層(4)、n−型AlGaNバリア層(5)、活性領域(6)、第1のp−型AlGaNバリア層(7)、第2のp−型AlGaNバリア層(8)、及びp−型GaNキャップ層(9)を含備える。p−型GaNキャップ層には、発生した光を発するためのウインド領域(10、W、A)をエッチングしている。 (もっと読む)

酸化亜鉛系半導体素子の製造方法

【目的】

p型ZnO系化合物半導体の電極の剥離や金属の凝集が生じず高い接着性を有するとともに良好なオーミック接触を有するコンタクト電極の形成方法及び当該電極が形成されたZnO系化合物半導体素子の製造方法を提供する。

【解決手段】

基板上にn型ZnO系半導体層及びp型ZnO系半導体層を含む積層体をp型ZnO系半導体層が表面に形成されるように形成する工程と、p型ZnO系半導体層をその表面温度が250℃ないし500℃の範囲内で熱処理する工程と、550℃未満の温度で、p型ZnO系半導体層上にp側電極金属を上記熱処理の後に形成する工程と、n型n型ZnO系半導体層上にn側電極金属を形成してZnO系半導体素子を形成する工程と、からなる。

(もっと読む)

パワーデバイスおよびその製造方法

【課題】低価格でオン抵抗が低いパワーデバイスおよびその製造方法を提供する。

【解決手段】本パワーデバイスは、金属製支持基板10と、金属製支持基板10の一方の主面10m側に順次形成されているIII族窒化物導電層20、III族窒化物能動層30および電極40と、を含む。また、本パワーデバイスの製造方法は、金属製支持基板10にIII族窒化物導電層20が接合された導電層接合金属製支持基板12を準備する工程と、III族窒化物導電層20上にIII族窒化物能動層30を形成する工程と、III族窒化物能動層30上に電極40を形成する工程と、を備える。

(もっと読む)

オーミック電極、半導体装置、オーミック電極の製造方法および半導体装置の製造方法

【課題】AlGaN層の裏面(N原子面)上に低抵抗なオーミック電極を形成することが可能なオーミック電極、半導体装置、オーミック電極の製造方法および半導体装置の製造方法を提供する。

【解決手段】オーミック電極16は、表面13aと、この表面13aと反対側の裏面12bとを有し、表面13aが(0001)面で、導電型がn型であるAlGaN層11の裏面12bに形成されたオーミック電極16において、オーミック電極16において裏面12bに接触している領域はWを含むことを特徴としている。オーミック電極16の製造方法は、裏面12bに接触する領域にWおよびMoの少なくとも一方を含むオーミック電極16を形成することを特徴としている。

(もっと読む)

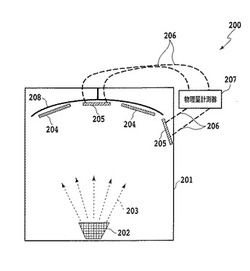

荷電粒子ビームPVD装置、シールド装置、基板をコーティングするためのコーティングチャンバ、およびコーティング方法

ケーシング(261)内部にあるコーティング材料のターゲット(262)と、ケーシング内に設けられた蒸気開口(263)と、蒸気開口に隣接して設けられ、浮遊電位にあるシールド装置(266、268;2680)と、を備える荷電粒子ビームPVD装置が提供される。  (もっと読む)

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

真空成膜装置

【課題】真空成膜装置において、成膜後の清掃作業を短時間で行うことができ、清掃作業員が成膜材料カスまみれになることが無い真空成膜装置を提供する。

【解決手段】真空成膜装置は、真空容器1内で成膜材料を被処理物表面上に成膜する真空成膜装置において、前記真空容器1の内壁面に配置される防着板30と、磁石と前記磁石の一方を被覆しかつ磁性を有する金属カバーとからなり、かつ、前記防着板30を前記真空容器1の内壁面に固定する防着板固定治具40と、を備えることを特徴とする。

(もっと読む)

導電接続部付き半導体素子用電極膜およびその製造方法、ならびに、この半導体素子用電極膜を具える発光素子

【課題】 金属ワイヤとの密着性が高く、かつ透明導電膜との界面における接触抵抗を低減させた、導電接続部としての金属複合膜を有する電極膜およびその製造方法、ならびに、この半導体素子用電極膜を具える発光素子を提供する。

【解決手段】 被成膜体上にチタンドープ酸化インジウムからなる透明導電膜を形成する工程と、該透明導電膜上に、外部との導電接続部としてNi含有膜およびAu含有膜を有する金属複合膜を形成する工程とを具えることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、半導体基体との界面における組成の均一性に優れ、ショットキー接合層との十分に高い密着性が得られるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第一半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第二半導体領域6bと、第一半導体領域1aにオーミック接触するオーミック接合層7と、第二半導体領域6bにショットキー接触するショットキー接合層8とを備え、オーミック接合層7の二乗平均粗さが、20nm以下である半導体装置とする。

(もっと読む)

薄膜形成装置および薄膜形成方法

【課題】 厚み変動を小さく、かつ収率を高くすることができる、薄膜形成装置を提供する。

【解決手段】 本発明の薄膜形成装置10は、真空引き雰囲気の蒸着チャンバー内で、蒸着源から物質を蒸発させて基材1に蒸着膜を形成する装置であり、この装置では、基材1を蒸着源に面するように保持する基材ホルダー3を備え、基材ホルダー3は、基材1が蒸着源7を囲い込む筒状体をなす面に沿って配置することを特徴とする。

(もっと読む)

有機薄膜トランジスタ

【課題】低閾値電圧、高電界効果移動度及び高オン/オフ電流比を有するボトムコンタクト型有機薄膜トランジスタを提供する。

【解決手段】基板上に、少なくともゲート電極、絶縁体層、ソース電極、ドレイン電極及び有機半導体層を含むボトムコンタクト型有機薄膜トランジスタであって、前記ソース電極及び前記ドレイン電極の少なくとも一方が、酸化物層及び金属層が積層してなる積層構造を有し、前記金属層が有機薄膜層で表面修飾されてなる有機薄膜トランジスタ。

(もっと読む)

窒化物半導体発光ダイオード素子およびその製造方法

【課題】高い電流密度の電流を注入して連続駆動させた場合でも高い信頼性を有する窒化物半導体発光ダイオード素子およびその窒化物半導体発光ダイオード素子の製造方法を提供する。

【解決手段】n型窒化物半導体層と、p型窒化物半導体層と、n型窒化物半導体層とp型窒化物半導体層との間に設置された窒化物半導体活性層とを含み、窒化物半導体活性層に対してp型窒化物半導体層側に、酸化インジウム錫を含有する第1の透明電極層と、酸化錫を含有する第2の透明電極層とを有する窒化物半導体発光ダイオード素子とその窒化物半導体発光ダイオード素子の製造方法である。

(もっと読む)

薄膜製作方法

形成されたフィルム形態をナノ粒子塊のものから粒子およびドロップレットの無い平滑な薄膜に連続的に調整することが可能なパルスレーザー蒸着(PLD)の方法。発明の様々な実施形態を使って合成されることができる材料は、金属、合金、酸化金属および半導体を含むが、それらに限定はされない。様々な実施形態において、超短パルスレーザーアブレーションおよび蒸着の「バースト」モードが提供される。フィルム形態の調整は、各バースト内のパルス数およびパルス間の時間間隔、バースト繰り返しレート、およびレーザーフルエンスのようなバーストモードパラメータを制御することによって達成される。システムは、超短パルスレーザーと、適切なエネルギー密度でターゲット表面上にフォーカスされたレーザーを配送するための光学システムと、その中にターゲットおよび基板が設置され背景ガスとそれらの圧力が適切に調節された真空チェンバーと、を含む。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】表面荒れの小さいオーミック電極を有する半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体層(1)と、この半導体層上に形成されたオーミック電極(2)と、このオーミック電極の上面と側面を覆うように形成されたカバー電極(3)とを備え、オーミック電極はAlを含有する合金層を含み、カバー電極はW、Ta、Nb、Mo、WNx、およびWSixから選択された少なくとも1種の金属層を含みかつ100nm以上の膜厚を有することを特徴としている。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

高出力ダイヤモンド半導体素子の最適作動温度制御方法

【課題】各温度領域における最適なドーピング濃度を提供し、高温動作ダイヤモンド半導体での動作時の抵抗を最低限にし、省エネルギー動作を可能にする高出力ダイヤモンド半導体素子の最適作動温度制御方法を提供する。

【解決手段】ショットキー電極をカソードとし、オーミック電極をアノードとし、ショットキー電極、ダイヤモンドp−ドリフト層、ダイヤモンドp+オーミック層、オーミック電極からなる構造の高出力ダイヤモンド半導体素子において、不純物ドーピング濃度をコントロールすることにより、高出力ダイヤモンド半導体素子の最適作動温度を設定することを特徴とする高出力ダイヤモンド半導体素子の最適作動温度制御方法。

(もっと読む)

半導体発光素子及びその製造方法

【課題】発光素子の製造プロセスにおいて、あるいは又、発光素子の動作時、安定した挙動を示す第2電極を有する発光素子を提供する。

【解決手段】発光素子は、n型の導電型を有する第1化合物半導体層11、第1化合物半導体層11上に形成され化合物半導体から成る活性層12、活性層12の上に形成された、p型の導電型を有する第2化合物半導体層13、第1化合物半導体層11に電気的に接続された第1電極15、及び、第2化合物半導体層13上に形成された第2電極14を備えており、第2電極14は、チタン酸化物から成り、4×1021/cm3以上の電子濃度を有し、活性層で発光した光を反射する。

(もっと読む)

ダイオードの製造方法

【課題】 2種類の金属電極を有するダイオードを製造する容易な製造方法を提供する。

【解決手段】 n型半導体領域20の表面にp型半導体領域30を結晶成長させる工程と、p型半導体領域30の表面31にオーミック接合Jrするオーミック電極40(第1金属膜)を形成する工程と、オーミック電極40の表面41に開口を有するマスクを形成する第3工程と、マスクの開口からオーミック電極40とp型半導体領域30をエッチングしてn型半導体領域20を露出させる工程と、露出したn型半導体領域20の表面の少なくとも一部にショットキー接合Jsするショットキー電極50(第2金属膜)を形成する工程を備えている。

(もっと読む)

ダイオードとその製造方法

【課題】 半導体層の表層部にp型半導体領域とn型半導体領域の両者を有するダイオードにおいて、ダイオードの順方向電圧降下を低減化する技術を提供する。

【解決手段】 表面6aに複数本の溝2が形成されている半導体層3は、p型半導体領域40と、そのp型半導体領域を取り囲む領域に形成されているn型半導体領域30と、n+型カソード領域20を有している。p型半導体領域40は、溝2の底面6cにおいて露出している。オーミック電極51は、溝2の底面6cの範囲内に形成されてp型半導体領域40にオーミック接合J1している。ショットキー電極53は、溝2の側面6を含む表面側の露出範囲に形成されてn型半導体領域30にショットキー接合J2している。カソード電極10は、カソード領域20の裏面側の露出範囲に形成されてカソード領域20にオーミック接合J1している。

(もっと読む)

41 - 60 / 112

[ Back to top ]