Fターム[4M104DD61]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427)

Fターム[4M104DD61]の下位に属するFターム

露光 (189)

エッチング (3,048)

パターニング用マスク (645)

部分的変質によるもの (33)

物理的除去によるもの (432)

Fターム[4M104DD61]に分類される特許

41 - 60 / 80

膜パターン及びその製造方法

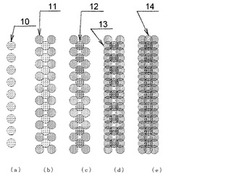

【課題】膜パターンの機能(導電膜の場合は導電性)を阻害させることなく、基体に対する密着力が高い膜パターンを、液滴吐出法により提供する。

【解決手段】基板上にインクジェットから液滴を吐出し、乾燥固化し、密着性機能を持つドットアレイ10を形成する。このときドット直径以上のピッチで形成する。密着性機能を持つドットアレイの周りに導電性機能を持つドットアレイ11をドット直径以上のピッチで液滴吐出し、乾燥固化する。この後、導電性機能を持つドットの間にドットが一部重ねて連結するように導電性機能を持つドットアレイ12,13,14を同様の方法で形成する。密着性機能を持つドットアレイは機能性ドットアレイは基体表面に選択的に形成できるので、表面に電極等が形成されている基板にも適用できる。

(もっと読む)

膜パターン形成用基板ならびに膜パターン形成基板、薄膜トランジスタ形成基板、液晶表示素子とその製造方法

【課題】 液状の導電性材料を充填・硬化することで膜パターンを上記基板上に形成するためのバンクが形成されている膜パターン形成用基板やそれを用いた基板の製造コストを抑える。

【解決手段】 本発明の膜パターン形成用基板は、少なくとも一つの膜部材がバンクを成している。例えば、a−Si膜13とn+型a−Si膜15とがバンクを成している。そこへ液状の導電性材料を充填・硬化することで膜パターンを上記基板上に形成する。したがってバンク形成専用のプロセスや部材が不要になる。

(もっと読む)

電子デバイスのレーザアブレーション

本発明は、レーザアブレーションを使った電子デバイスの製造方法と、それによって製造されたデバイスに関する。方法の実施形態は特にステップ−アンド−リピートモードでレーザアブレーションを使って薄膜トランジスタ(TFT)構造内に電極を規定するのに適している。電子デバイスを製造する方法であって、該デバイスは基板上の複数のレイヤからなり、該レイヤは上部導電レイヤと該導電レイヤと該基板の間の少なくとも1つのパターニングされた下部レイヤを含み、前記方法は、前記下部レイヤをパターニングし、前記上部導電レイヤを、連続的に印加されたレーザパターンによって前記上部導電レイヤの連続したエリアを剥離するステップ状プロセスを使ってレーザアブレーションによりパターニングすることからなり、前記連続的に印加されたレーザパターンは重複領域で互いに重複し、前記方法は更に、前記重複領域において前記パターニングされた下部レイヤが前記ステップ状レーザアブレーションによって実質的に損傷を受けないように、前記レーザパターンと前記パターニングされた下部レイヤを互いに構成することからなる電子デバイスを製造する方法。  (もっと読む)

(もっと読む)

高性能の有機デバイス製造用レーザアブレーション法

レーザアブレーション法を利用して有機トランジスタのチャンネル長を画定する。基板を金属堆積あるいは導電性ポリマー堆積でコーティングして、レーザアブレーションにより達成可能な分解能を向上させるべく薄膜に適用する。レーザアブレーション法はロール毎のプロセスに利用でき、プリント電子技術を生成するのに適当な速度、量、価格、分解能を達成する。 (もっと読む)

薄膜トランジスタ

【課題】レジスト等のマスクは一般的にパターニングが終了すると、除去され、マスク除去のための工程が必要となり工程数が増えてしまう。そこで、マスクを除去することなく使用した薄膜トランジスタを提供する。

【解決手段】所望の形状にパターニングするためのマスクを除去せずに薄膜トランジスタの一部を構成させる。例えば、ソース・ドレイン電極をパターニングするためのマスクを除去せず、薄膜トランジスタが有する構成とする。ソース・ドレイン電極は、インクジェット法によって作製されるため、薄膜トランジスタの半導体膜は、ソース・ドレイン電極の側面に接する構成となる。

(もっと読む)

薄膜トランジスタの形成方法

【課題】 レーザプロセスを利用した薄膜トランジスタの形成方法を提供すること。

【解決手段】 薄膜トランジスタの形成方法が、素子側基板にソース電極およびドレイン電極を設ける第1の工程と、前記ソース電極およびドレイン電極に接する半導体層を設ける第2の工程と、前記半導体層に重なるゲート絶縁層を設ける第3の工程と、前記ゲート絶縁層に重なるゲート電極を設ける第4の工程と、を包含している。そして、前記第1の工程は、レーザプロセスによって前記ソース電極およびドレイン電極を設ける工程を含んでいる。

(もっと読む)

薄膜トランジスタの形成方法

【課題】 レーザプロセスを利用した薄膜トランジスタの形成方法を提供すること。

【解決手段】 薄膜トランジスタの形成方法が、素子側基板にソース電極およびドレイン電極を設ける第1の工程と、前記ソース電極およびドレイン電極を覆う半導体層を設ける第2の工程と、前記半導体層に重なるゲート絶縁層を設ける第3の工程と、前記半導体層に重なるゲート絶縁層を設ける第4の工程と、を包含している。そして、前記第2の工程は、(a)第1のベース基板と、前記第1のベース基板上の第1のアブレーション層と、前記第1のアブレーション層上のドナー側半導体層と、を備えた第1のドナー基板を、前記素子側基板に重ねる工程と、(b)前記第1のドナー基板から前記素子側基板へ、前記ドナー側半導体層の少なくとも一部が転写されて前記半導体層が得られるように、第1のレーザビームを前記第1のアブレーション層に照射する工程と、を包含している。

(もっと読む)

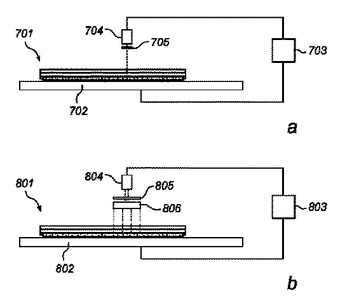

有機機能装置に電極層パターンを形成する方法

第1の透明電極層(103;203)と、第2の電極層(104;204)と、前記第1および第2の電極層(103、104;203、204)の間に挟まれた有機機能層(102;202)と、を有する有機機能装置(101;201)に、電極層パターンを形成する方法である。当該方法は、レーザ(704;804)を、前記第1の透明電極層(103;203)を介して、前記有機機能装置(701;801)に照射されるように配置するステップ(601)と、前記レーザ(704;804)により、前記第2の電極層(104;204)の導電性を局部的に変化させることが可能となるように、レーザパラメータの組を選定するステップと、前記レーザパラメータの組に従って、前記レーザ(704;804)により、前記第2の電極層(104;204)の導電性を局部的に変化させ、これにより前記電極層パターンが形成されるステップと、を有する。  (もっと読む)

(もっと読む)

層選択レーザーアブレーションパターニング

本発明は、選択的パターニングにレーザーアブレーションを使用して薄膜トランジスター(TFT)構造などの電子デバイスを製作する方法に関する。本発明は有機電子デバイスを製作する方法であって、製作される有機電子デバイスは、上部導電層と、この上部導電層のすぐ下にある下位層と、少なくとも1つの溶解処理可能な半導電性層とを有する構造を備え、上部導電層は10nmと200nmの間の厚さを有していることが好ましい。本発明の方法は、上部導電層をパターニングするステップを含み、このパターニングのために上部導電層の領域を下位層から除去するように、パルスレーザーを使用して上部導電層にレーザーアブレーションを行い、このレーザーアブレーションは、レーザーの単一のパルスを使用して上部導電層を実質的に完全に除去し、下にある下位層を露出させるものである。 (もっと読む)

有機薄膜トランジスタ及びその製造方法、これを備えた有機電界発光表示装置

【課題】有機薄膜トランジスタ及びその製造方法、これを備えた平板表示装置を提供する。

【解決手段】基板上に絶縁膜を形成する段階と、バッファ膜をフォトエッチングして互いに一定間隔で離隔された凹部を形成する段階と、バッファ膜上にソース及びドレインのための電極層を形成する段階と、電極層をフォトエッチングして凹部にソース及びドレイン電極を形成する段階と、ソース及びドレイン電極と上記バッファ膜上に半導体層を形成する段階と、半導体層上にゲート絶縁膜を形成する段階と、ゲート絶縁膜上にゲートを形成する段階と、を含む有機薄膜トランジスタの製造方法である。これにより、半導体層のパターン不良を防止してチャネル領域での短絡現象を防止できる。

(もっと読む)

導電パターンの形成方法、薄膜トランジスタの製造方法、電気光学装置、及び電子機器

【課題】 特に液滴吐出法によって形成する配線等の導電パターンを、その成分元素の拡散を起こさせることなく良好に形成することができるようにした導電パターンの形成方法等を提供する。

【解決手段】 導電性材料を含有してなる機能液を基板P上に配置して導電パターン82を形成する方法である。基板P上に導電パターン82の形成領域に対応したバンクB1を形成する工程と、バンクB1によって区画された領域に機能液を液滴吐出法で配置する工程と、配置した機能液上にポリシラザン液を液滴吐出法で配置する工程と、バンクB1によって区画された領域に積層した機能液とポリシラザン液とに対して所定の処理を施すことにより、ポリシロキサンを骨格とする無機質層81で導電性材料からなる導電膜80を覆った導電パターン82を形成する工程と、を備えている。

(もっと読む)

機能性膜パターン成膜方法、機能性膜パターン、および電子機器

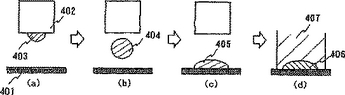

【課題】 電磁波の照射エネルギー量の低減を図り、基板に与える熱のダメージを抑制することができ、必要な光源の設備の小型化を図った機能性膜パターン成膜方法、機能性膜パターン、および電子機器を提供する。

【解決手段】 薄い膜パターン40を一層だけ基板21上に形成し、この膜パターン40にレーザ光50を照射し凹凸41a,41bのある熱伝導防止膜41を形成する。この後、熱伝導防止膜41上にメインの膜パターン43を形成し、この膜パターンにレーザ光を照射して配線パターン19を形成する。熱伝導防止膜41の表面には凹凸41a,41bがあり(図1(A)の拡大部62参照)、熱伝導防止膜41と基板21の接触面積が減少するので、膜パターン43にレーザ光50を照射して配線パターン19を形成する際に、膜パターン43と基板21との間の見かけ上の熱伝導率を下げることができる。

(もっと読む)

薄膜トランジスタの形成方法

【課題】印刷方法による流動性や粘着性による不具合のない、チャネル長が短い薄膜トランジスタの形成方法を提供する。

【解決手段】凹部が少なくともソース・ドレイン電極のパターンを有する凹版転写型11の凹部に導電材21を充填し硬化させた後、薄膜トランジスタ用基材を接着剤を介在させた状態で前記凹版転写型に重ね合わせてから、前記薄膜トランジスタ用基材を前記接着剤とともに凹版転写型から分離して、導電材を接着剤を介して薄膜トランジスタ用基材に転写させてソース・ドレイン電極を形成する工程を含むことを特徴とする。

(もっと読む)

レーザ成膜方法、レーザ成膜装置、および電子機器

【課題】 レーザ光の投入エネルギー量の低減と、必要なレーザ設備の小型化とを図ったレーザ成膜方法、レーザ成膜装置、および電子機器を提供する。

【解決手段】 レーザ成膜方法は、機能性液状材料を含む膜パターン40を基板21上に形成し、膜パターン40にレーザ光を照射し、レーザ光の吸収による光熱変換で発生する熱で配線パターンを形成する。配線パターンが形成される焼成初期から焼成後期までの過程において、各過程で変化する膜パターン40の吸収スペクトルに応じて、吸収効率の良い最適な2波長のレーザ光50,53を、膜パターン40に時間差を持たせて照射する。レーザ光50の照射による光熱変換で発生する熱で膜パターン40の焼成を進めて配線パターンを形成する焼成終期で、単位出力のコストが低いレーザ(レーザ本体54)を使ってレーザ光53を膜パターン40に照射する。

(もっと読む)

レーザパターニングされた金属ゲートを備えるMOSトランジスタ及びそれを形成するための方法

【課題】 レーザパターニングされた金属ゲートを有するMOSトランジスタ、及びその製造方法。

【解決手段】 本方法は概して、誘電体薄膜上に金属含有材料の層を形成することであって、その誘電体薄膜は無機半導体を含む電気的機能性基板上にある、形成すること;金属含有材料層から金属ゲートをレーザパターニングすること;及び、金属ゲートに隣接する場所にある無機半導体内にソース端子及びドレイン端子を形成することを含む。そのトランジスタは概して、電気的機能性基板と;電気的機能性基板の少なくとも一部の上にある誘電体薄膜と;誘電体薄膜上にあるレーザパターニングされた金属ゲートと;金属ゲートに隣接する、ドープされた無機半導体層を含むソース端子及びドレイン端子とを備える。本発明は、1つ又は複数の従来のフォトリソグラフィ工程をなくすことにより、信頼性がある電気的特性を有するMOS薄膜トランジスタを迅速に、効率的に、及び/又は低コストで提供する点で好都合である。

(もっと読む)

金属、半導体、絶縁体パターンの線幅及びサイズを縮める方法

【課題】既存の方法で先ず線幅やサイズの大きい(例えば、50nm以上)パターン202などを製作した後、物理的、化学的、機械的蝕刻を利用してパターンのサイズを更に縮める。

【解決手段】従来の方法で線幅が20nm以上の所定サイズの線幅を有するパターン202を作るステップS302、及び前記パターン202を物理的、機械的加工で削ってサイズを縮めるステップ、前記パターン202を化学的方法で蝕刻することによって前記パターン202のサイズを縮めるステップ、並びに前記パターン202を材料の最外から分解して前記パターン202のサイズを縮めるステップなどの中から選択された一つのステップS306を含むことにより金属、半導体、絶縁体パターンの線幅及びサイズを縮める。

(もっと読む)

半導体装置の製造方法、電気光学装置及び電子機器

【課題】 所望の高さの隔壁を容易に形成することができる隔壁形成技術等を提供する。

【解決手段】 第1層間絶縁膜140の上に形成されるパターニング用のレジスト膜150を厚く形成することにより、パターニング用のマスクとして利用するだけでなく、隔壁としても利用する。まず、有機材料からなるレジスト材をインクジェット装置などを用いて第1層間絶縁膜140の上に全面塗布する。次に、レジスト膜150(レジストマスク)を利用して第1層間絶縁膜140をエッチングする。この第1層間絶縁膜140をパターニング用のマスクとして利用するだけでなく、インクジェット法を用いてゲート電極160を形成するための隔壁として利用する。

(もっと読む)

液滴吐出装置、パターンの形成方法、および半導体装置の製造方法

本発明では液滴吐出装置から吐出された液滴が基板に着弾した後の位置制御を改善することが可能なパターンの作製方法を提供する。また着弾後の液滴位置精度を改善することが可能な液滴吐出装置を提供する。更には、本発明の液滴吐出装置を用いた半導体装置の製造方法を提供する。

本発明は、吐出部から吐出された液滴、又は液滴を着弾する基板にレーザ光を照射して、液滴の着弾位置を制御することを特徴とする。本発明によりフォトリソグラフィー工程を用いることなくパターンを形成することが可能である。  (もっと読む)

(もっと読む)

荷電ビームを用いた液滴吐出装置及び該装置を用いてのパターンの作製方法

液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。本発明は、主に絶縁表面を有する基板上において、液滴吐出法によってレジスト材料或いは配線材料等を直接パターニングを行うに際し、液滴着弾精度を飛躍的に向上させることが可能になる。具体的には、液滴吐出法による液適の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させることを特徴とする。  (もっと読む)

(もっと読む)

高解像度および低解像度にパターニングされた膜特徴部分をもつ大面積電子装置

【課題】大面積の電子装置の製造に利用できるパターニングされたIC用薄膜層の形成方法として、安価に大面積のパターンを形成できるパターニング技術と、小さな特徴パターンを形成できる微細パターニング技術と、を同時に実現する方法を提供する。

【解決手段】本発明は、装置の基板上にパターニングされた薄膜層を形成する方法であって、第1の処理ツールを用いて、前記装置基板上に比較的高解像度の第1構造を形成するステップ(ブロック110)と、第2の処理ツールを用いて、前記装置基板上に、前記第1構造と接続されるように、比較的低解像度の第2構造を形成するステップ(ブロック120)と、を含む方法であることを特徴とする。

(もっと読む)

41 - 60 / 80

[ Back to top ]