Fターム[4M104DD80]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 熱処理(低温処理を含む) (3,402) | ランプ照射(RTA) (528)

Fターム[4M104DD80]に分類される特許

1 - 20 / 528

炭化珪素半導体装置の製造方法

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

電極構造体、それを備える窒化ガリウム系の半導体素子及びそれらの製造方法

【課題】電極構造体、それを備える窒化ガリウム系の半導体素子及びそれらの製造方法を提供する。

【解決手段】GaN系の半導体層GL10と、GaN系の半導体層上に備えられた電極構造体500A,500Bと、を備え、電極構造体500A,500Bは、導電物質を含む電極要素50A、50Bと、電極要素50A,50BとGaN系の半導体層200との間に備えられた拡散層5A、5Bと、を備え、拡散層5A,5Bは、n型ドーパントを含み、n型ドーパントは、4族元素を含み、拡散層と接触したGaN系の半導体層200の領域は、n型ドーパント(例えば、4族元素)でドーピングされる窒化ガリウム系の半導体素子である。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

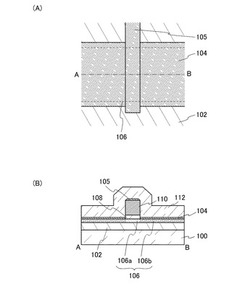

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】ショットキー電極形成前に酸洗浄を行ってもp型オーミック電極がその酸に曝されることなく、p型オーミック電極とショットキー電極との電気的接続が良好な炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に形成された複数のp型不純物領域3と、p型不純物領域3上の一部に形成されたp型オーミック電極4と、p型不純物領域3上の一部に、p型オーミック電極4を覆うように形成された耐酸性のバリアメタル層5と、バリアメタル層5、p型不純物領域3、及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板1のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

熱処理方法

【課題】シリサイドの横方向への異常成長を防止しつつ、シリサイド形成を行うことができる熱処理方法を提供する。

【解決手段】半導体ウェハーWのソース・ドレイン領域にシリコンなどのイオンを注入し、そのイオン注入領域150を非晶質化する。非晶質化されたイオン注入領域150にニッケル膜158を成膜する。ニッケル膜158が成膜された半導体ウェハーWにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで1ミリ秒以上20ミリ秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーWの表面温度を目標温度T2から±25℃以内の範囲内に1ミリ秒以上100ミリ秒以下維持する。これにより、ニッケルシリサイドが縦方向に優先的に成長する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

半導体発光装置及びその製造方法

【課題】高いオーミック性と反射率を併せ有する電極構造を備える、低駆動電圧で駆動し、良好な光取り出し効率を有する半導体発光装置及びその製造方法を提供すること。

【解決手段】n型半導体層と、p型半導体層と、前記n型半導体層と前記p型半導体層との間に設けられた活性層と、前記n型半導体層に接して設けられたn電極と、前記p型半導体層に接して設けられたp電極とを具備する半導体発光素子。前記p電極が前記p型半導体層上に少なくとも一部が網目状に形成されたNiO層と、このNiO層に接して形成されたAg層とを含む。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の十分な低減を可能とする半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法は、少なくとも一方の主面を含む領域が単結晶炭化珪素からなる基板を準備する工程と、一方の主面上に活性層23を形成する工程と、基板の前記一方の主面とは反対側の他方の主面を含む領域を研削する工程と、他方の主面を含む領域を研削する工程において形成されたダメージ層22Cを除去する工程と、ダメージ層22Cが除去されることにより露出した主面に接触するように裏面電極を形成する工程とを備え、一方の主面は{0001}面に対するオフ角が50°以上65°以下となっている。

(もっと読む)

素子及び太陽電池

【課題】太陽電池としたときに発電性能に優れる素子、及び該素子を搭載した太陽電池を提供する。

【解決手段】シリコン基板と、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含み錫の含有率が1質量%以上である電極用ペースト組成物Aの焼成物である電極層Aと、リン含有銅合金粒子、ガラス粒子、溶剤及び樹脂を含み錫の含有率が0.1質量%以下である電極用ペースト組成物Bの焼成物である電極層Bと、がこの順に積層された素子である。

(もっと読む)

アルミニウム体を備えた基体の製造方法

【課題】基体上に成膜特性(反射率、及び密着性)に優れた膜状のアルミニウム体を形成することができるアルミニウム体を備えた基体の製造方法を提供する。

【解決手段】基体をプラズマ処理するプラズマ処理工程と、プラズマ処理された基体上に、アミン化合物と水素化アルミニウムとの錯体及び有機溶媒を含有するアルミニウム体形成用組成物を塗布して、上記基体上に上記組成物からなる塗布層を形成させる塗布工程と、上記塗布層に加熱および光照射の少なくともいずれか一方を行うことにより、膜状のアルミニウム体を形成させるアルミニウム膜形成工程と、を含むアルミニウム体を備えた基体の製造方法。

(もっと読む)

印刷用溶剤又は溶剤組成物

【課題】印刷法により電子素子パターンを形成するためのインク等に含有する溶剤又は溶剤組成物であって、前記インク等に印刷時の優れた版離れ性、高温乾燥時の優れたパターン保持性、及び速乾性を付与する溶剤又は溶剤組成物を提供する。

【解決手段】本発明の電子素子パターン印刷用溶剤又は溶剤組成物は、印刷法により電子素子パターンを形成する際に使用する溶剤又は溶剤組成物であって、少なくとも1,2,5,6−テトラヒドロベンジルアルコールを溶剤又は溶剤組成物全量(100重量%)の10重量%以上含むことを特徴とする。前記印刷法としては、インクジェット法、スクリーン印刷法、凸版印刷法、オフセット印刷法、グラビア印刷法、マイクロコンタクト印刷法、及びナノインプリント法からなる群より選択される少なくとも1種の方法が好ましい。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

1 - 20 / 528

[ Back to top ]