Fターム[4M104DD82]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 高エネルギービーム照射 (427) | 界面層、電極層へのITM (52)

Fターム[4M104DD82]に分類される特許

1 - 20 / 52

半導体装置の製造方法

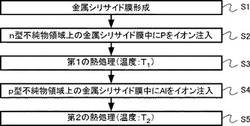

【課題】SiC基板上に形成されたデバイスに対して、低温の熱工程にて良好なオーミック特性を備える電極を実現する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、炭化珪素(SiC)で形成されるn型不純物領域上およびp型不純物領域上に金属シリサイド膜を形成し、n型不純物領域上の金属シリサイド膜中にリン(P)をイオン注入し、第1の熱処理を行い、p型不純物領域上の金属シリサイド膜中にアルミニウム(Al)をイオン注入し、第1の熱処理よりも低温の第2の熱処理を行う

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】イオン注入で所定の元素をゲート電極に導入して、異なる仕事関数を有するゲート電極のMOSトランジスタを形成する際に、製造工程の増加を抑制して低コストの半導体装置を提供する。

【解決手段】半導体装置の製造方法では、導電膜上5a,5bにおいて、第1の領域1aから第2の領域1bまでを覆う第1のマスク6b、第2の領域の上方にスペース部7b、及び第2の領域1bから第3の領域1cまでを覆う第2のマスク6cを有するマスクパターンを設ける。スペース部内、並びに第1及び第2のマスクの第1の側面にサイドウォール膜7aを設ける。第1の側面に接するサイドウォール膜の下に位置する導電膜の領域内に不純物を注入する。サイドウォール膜をマスクに用いて異方性エッチングを行うことによりゲート絶縁膜及びゲート電極を形成してMOSトランジスタ。

(もっと読む)

半導体装置

【目的】ラッチアップ耐量が高く、低抵抗な縦型半導体装置を提供する。

【解決手段】n型ソース領域4の上面にp型第1ベース領域2aおよびp型第2ベース領域2bが形成され、該n型ソース領域4の下面にソース電極5が設けられ、p型第2ベース領域2bの上面に絶縁膜を介してドレイン電極9が形成されている。該p型第2ベース領域2bの上面にはゲート電極用トレンチと、該第1ベース領域2aと第2ベース領域2bおよびn型ソース領域4を短絡する短絡用トレンチが並設されている。該ゲート電極用トレンチの側壁にはn型ドリフト領域6とn型ドレイン領域8がRESURF状に形成され、短絡用トレンチには短絡用導電体12が形成されて該導電体12は該ドレイン電極9と絶縁されている。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率材料を含むゲート絶縁膜と、高融点金属等を含むゲート電極とを備え、消費電力の低減と高速動作化とが図られた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、高誘電率膜を含む絶縁膜101aを形成する工程(a)と、上面に酸化膜が形成され、高融点金属または高融点金属の化合物の少なくとも一方を含む第1の導電膜102aを形成する工程(b)と、酸化膜103aを間に挟んで第1の導電膜102a上に、シリコンを含む第2の導電膜104aを形成する工程(c)と、第1の導電膜102aおよび第2の導電膜104aに対してイオン注入を行い、酸化膜103aの構成材料を前記第2の導電膜104a中のシリコンと混合させてミキシング層103bを形成する工程(d)と、熱処理を行ってミキシング層103bを導電層103cにする工程(e)とを備える。

(もっと読む)

半導体装置及び配線

【課題】低抵抗の電極や配線を有する半導体装置を実現する。

【解決手段】本実施形態による配線は、p型不純物が導入されたp型不純物層部分と、n型不純物が導入されたn型不純物層部分と、p型及びn型不純物が導入された(p+n)型不純物層部分と、を含む半導体層と、少なくとも(p+n)型不純物層部分上に形成されたシリサイド層と、を備え、(p+n)型不純物層部分に含まれるp型不純物とn型不純物の総濃度は、5E20cm−3未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

電界効果半導体装置及びその製造方法

【課題】ノーマリオフのHEMTを得ることが困難であった。

【解決手段】本発明に従うヘテロ接合型電界効果半導体装置は、電子走行層31と、第1及び第2の電子供給層32,33と、キャップ層34と、ソース電極8と、ドレイン電極9と、ゲート電極10と、シリコン酸化物から成る絶縁膜11と、p型金属酸化物半導体膜12とを有している。第2の電子供給層33に凹部7が形成され、この凹部7に絶縁膜11とp型金属酸化物半導体膜12とゲート電極10との積層体が配置されている。正孔濃度の高いp型金属酸化物半導体膜12はノーマリオフ特性に寄与し且つゲートリーク電流の低減に寄与する。絶縁膜11はゲートリーク電流の低減に寄与する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

デュアル仕事関数の金属ゲートを統合する際のイオン注入を用いた有効仕事関数の変化

【課題】 デュアル仕事関数の金属ゲートを統合する際にイオン注入を用いて有効仕事関数を変化させる方法を提供する。

【解決手段】 デュアル有効仕事関数をもつ金属ゲートを集積化するために有効仕事関数を変化させるためのイオン注入が提示される。1つの方法は、第1の型の電界効果トランジスタ(FET)領域及び第2の型のFET領域の上に、高誘電率(高k)層を形成することと、第1の型のFET領域及び第2の型のFET領域の上に、第1の型のFETに適合する第1の有効仕事関数をもつ金属層を形成することと、第2の型のFET領域の上の金属層内に種を注入することによって、第2の型のFET領域の上の第1の有効仕事関数を第2の異なる有効仕事関数に変化させることとを含むことができる。

(もっと読む)

半導体装置の製造方法

【課題】イオン注入工程を用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bに研磨処理を行って裏面1bに微細な凹凸を形成する。そして、凹凸が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、イオン注入工程を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜上にポリシリコン膜3を形成する工程と、前記ポリシリコン膜の下層側に重元素の不純物イオン4をイオン注入する工程と、前記ポリシリコン膜の上層側に、前記重元素より質量の小さい軽元素の不純物イオン6をイオン注入する工程と、前記ポリシリコン膜を加工することにより、前記ゲート絶縁膜上にゲート電極3aを形成する工程と、前記半導体基板に不純物イオンをイオン注入し、熱処理を施すことによりソース・ドレイン領域の拡散層9を形成する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】側面方位とキャリア極性に応じて歪み方向が最適化されたFinFETおよびナノワイヤトランジスタと、これを実現するSMTを導入した製造方法を提供する。

【解決手段】半導体基板14と、半導体基板14の上部に形成され、半導体基板14主面に平行な上面と、半導体基板14主面に垂直な(100)面の側面を有する直方体状半導体層40と、直方体状半導体層40内に形成されるチャネル領域18と、チャネル領域18の少なくとも側面上に形成されるゲート絶縁膜20と、ゲート絶縁膜20上のゲート電極30と、直方体状半導体層40内に、チャネル領域18を挟み込むよう形成されるソース/ドレイン領域とを備え、チャネル領域18に、半導体基板14主面に対して垂直方向の圧縮歪みが印加されているpMISFETを有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置

【課題】低閾値動作に可及的に適した実効仕事関数を有するMISトランジスタを備えた半導体装置を提供することを可能にする。

【解決手段】Hf(或いはZr)酸化物に高価数金属を添加することでギャップ内準位を作りだし、窒素あるいはフッ素などによりギャップ内準位の位置を変化させることで、最適な実効仕事関数を有する電極を備え、低閾値動作が可能なCMISデバイスを実現した。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗をさらに低減する疑似SOI構造の半導体装置の提供。

【解決手段】第1および第2のゲート側壁絶縁膜23WA〜23WDをマスクに、前記側壁絶縁膜のそれぞれ外側に、第1および第2の凹部21TA〜21TDを形成する工程と、前記側壁絶縁膜のそれぞれ外側に、第1および第2のダミー側壁膜を形成する工程と、前記ダミー側壁膜23DA〜23DDをマスクに、前記シリコン基板のうち、前記凹部における露出部分を酸化し、それぞれ第1および第2のシリコン酸化膜を形成する工程と、前記凹部に第1および第2のシリコン膜を充填する工程と、前記シリコン膜上に金属膜を堆積し、熱処理することにより、シリサイド領域が側壁絶縁膜の外端を超えて、前記ゲート電極23A,23B直下の領域近傍にまで到達するようにシリサイド領域を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】

深さ方向の圧縮応力を印加して、NMOSトランジスタの性能を向上した半導体装置を提供する。

【解決手段】

CMOS型半導体装置用シリコン基板のNMOSトランジスタ領域、PMOSトランジスタ領域上方に多結晶シリコンのゲート電極を形成し、ゲート電極側壁上に第1サイドウォールスペーサを形成し、NMOSトランジスタ領域、PMOSトランジスタ領域に選択的にイオン注入を行ない、第1サイドウォールスペーサに整合した低抵抗ソース/ドレイン領域を形成する際、NMOSトランジスタ領域においてはゲート電極の上部をアモルファス化し、少なくともNMOSトランジスタ領域において第1サイドウォールスペーサを実質的に除去し、ゲート電極を覆ってキャップ膜を形成し、低抵抗ソース/ドレイン領域の活性化を行うと共にアモルファス化されたゲート電極の再結晶化を行う熱処理を行ない、キャップ膜を異方性エッチングして第2サイドウォールスペーサに加工する。

(もっと読む)

1 - 20 / 52

[ Back to top ]