Fターム[4M104EE01]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412)

Fターム[4M104EE01]の下位に属するFターム

Fターム[4M104EE01]に分類される特許

101 - 120 / 123

電界効果トランジスタ及びその製造方法

【課題】ゲートリーク電流の発生を低減し、ゲート耐圧などの素子特性を向上させることが可能な電界効果トランジスタ及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板上に形成され、キャリアを供給する活性層を含むメサ型構造の化合物半導体層2と、前記化合物半導体層2上に形成されるソース電極層3及びドレイン電極層4と、前記化合物半導体層2の段差面を横断し、前記ソース電極層3と前記ドレイン電極層4の間に形成されるゲート電極5と、前記段差面と前記ゲート電極間に設けられる絶縁領域6を備える。

(もっと読む)

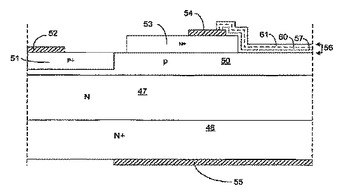

高電圧炭化ケイ素半導体デバイスのための環境的に堅固なパッシベーション構造

炭化ケイ素における高電界半導体デバイスのための改良された終端構造を開示する。該終端構造は、高電界動作のための炭化ケイ素ベースのデバイスと、該デバイスにおける活性領域と、該活性領域のためのエッジ終端パッシベーションとを含み、該エッジ終端パッシベーションは、表面状態を満足させ、界面密度を低下させるための該デバイスの炭化ケイ素部分の少なくとも一部分上の酸化物層と、水素の取り込みを回避するため、および寄生容量を減少させ、捕捉を最小化するための該酸化物層上の窒化ケイ素の非化学量論的層と、該非化学量論的層および該酸化物層を封入するための該非化学量論的層上の窒化ケイ素の化学量論的層と、を含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】電極間の耐圧を向上できる半導体装置を提供する。

【解決手段】この半導体装置は、ショットキー電極であるゲート電極1はオーミック電極であるドレイン電極2側の第1の角3の内角θ1が90°を超えている。これにより、ゲート電極1とドレイン電極2との間の電界がゲート電極1の第1の角3に集中することを抑制できる。また、ゲート電極1の断面の多角形S1の第2の角5は内角θ2が鋭角であるが、内角θ2の2等分線の外向きの延長線L2がドレイン電極2および半導体層100と交差しないので、この第2の角5にはゲート電極1とドレイン電極2との間の電界が集中し難い。

(もっと読む)

電界効果トランジスタ

【課題】ゲートの遷移電流や漏れ電流が小さく、ピンチオフ電圧が安定な電界効果トランジスタを提供すること。

【解決手段】半導体層3上でこの半導体層3の表面に沿って互いに離間した位置に、それぞれ金属電極を有するソース5、第1ゲート6、第2ゲート7、ドレイン8をこの順に備える。第1ゲート6はノーマリオフ、第2ゲート7はノーマリオンになっている。第1ゲート6はショットキ型であり、第2ゲート7はMIS型である。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】シリコン窒化膜が半導体基板に近接しないようにした半導体集積回路装置と、コンタクトホールの加工を容易にする半導体集積回路装置の製造方法を提供する。

【解決手段】素子分離領域4に囲まれたシリコン基板21上に、シリコン窒化膜をエッチングストッパーとして用いた自己整合コンタクトプロセスによって形成されたコンタクトホールに埋め込まれ、拡散層2,3に電気的に接続されたコンタクトプラグ33を有する半導体集積回路装置であって、前記拡散層2、3の露出面に選択エピタキシャル成長により形成された、各ゲート絶縁膜22の前記拡散層側端部と接するシリコン層28を形成し、各ゲート電極22と前記シリコン層28との間にシリコン酸窒化膜またはシリコン酸化膜からなる絶縁膜27’が前記ゲート絶縁膜22に接して埋め込まれており、シリコン窒化膜26,29’,32が絶縁膜27’によりシリコン基板21と隔離されている。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】短チャネル効果を抑制しつつ、一層の高速動作が可能な絶縁ゲート電界効果トランジスタ及びその製造方法の提供を目的とする。

【解決手段】チャネルが形成される半導体基板の領域と、当該領域にそれぞれ接し互いに離れて前記半導体基板上に形成されている一対のエクステンション部4と、前記一対のエクステンション部4の対向端から互いに離反する向きにさらに離れて前記エクステンション部4上に形成されている一対のソース・ドレイン領域5,6と、前記ソース・ドレイン領域5,6の間のチャネルが形成される半導体基板上において前記エクステンション部4の端部にかかる位置まで形成されているゲート絶縁膜5と前記ゲート絶縁膜5上に形成されたゲート電極Gと、少なくとも前記ゲート電極Gから前記一対のエクステンション部4にかかる領域までを被覆するように形成された応力調整層8と、を有する絶縁ゲート電解効果トランジスタ1。

(もっと読む)

半導体装置及びその製造方法

【課題】 nMOSFET及びpMOSFETのチャネル部分にひずみを与えることで、キャリア移動度を向上させた半導体装置及びその製造方法を提供する。

【解決手段】 基板上にゲート絶縁膜を介して形成されたゲート電極、ゲート電極の両側に形成されたゲート側壁、及び基板に形成されたソース・ドレイン領域をそれぞれ有した第1及び第2のMOSFETと、第1及び第2のMOSFETの隣接するゲート側壁の間に埋入された絶縁膜と、第1及び第2のMOSFETのゲート電極及びゲート側壁、及び絶縁膜を被覆してソース・ドレイン領域間に形成されるチャネルにひずみを与える被覆層を有するものとする。

(もっと読む)

半導体装置

【課題】メモリセルと周辺回路を備えた半導体装置において、周辺回路領域にキャパシタを、マスク工程を増加させることなく形成する。

【解決手段】

メモリセルと周辺回路を備えた半導体装置において、前記周辺回路領域に形成されるキャパシタは、前記メモリセル領域のゲート電極と同時に形成される下部電極と、前記メモリセル領域において前記コンタクトホール内壁面を覆う絶縁膜と同時に形成される容量絶縁膜と、前記コンタクトホールに形成されるコンタクトプラグと同時に形成される上部電極とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程を複雑にすることなく、金属シリサイドよりなるゲート電極及びこのゲート電極を覆うストレッサ膜を形成しうる半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板10内にチャネル領域を挟んで形成されたソース/ドレイン領域38と、チャネル領域上にゲート絶縁膜12を介して形成された金属シリサイドよりなるゲート電極44とを有するN型MISFETと、ゲート電極44を内包するようにゲート電極44の側壁部から上面部に渡って形成され、1GPa〜2GPaの引張り応力を有し、チャネル領域に引っ張り応力を印加する絶縁膜46とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 T字型又はΓ型のゲート電極を用いる場合に、耐湿性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】 半導体基板と、半導体基板上に離間して形成されたソース電極及びドレイン電極と、ソース電極とドレイン電極との間に配置され、半導体基板とショットキ接合されたT字型又はΓ型のゲート電極と、ゲート電極の下部の柱状部分を覆う酸化膜とを有し、酸化膜とソース電極及びドレイン電極とは離間している。

(もっと読む)

保護ゲート電界効果トランジスタであると形成するための構造と方法

電界効果トランジスタは以下の通り形成される。溝部は半導体領域で形成される。前記溝部の側面及び底部を覆う誘電層が形成される。溝部は導電体によって充填される。導電体は溝部に埋め込まれる。その結果、溝部の底部分において保護電極が形成される。導電体の埋め込み工程は、導電体の等方性エッチング処理を含む。電極間誘電体(IED)が埋め込まれた保護電極上に形成される。  (もっと読む)

(もっと読む)

パターンの形成方法及び液滴吐出ヘッド

【課題】 パターン形成において、低コスト化及び形成時間の短縮化を図るとともに、微細パターンの形成を可能としたパターンの形成方法を提供する。

【解決手段】 本発明のパターン形成方法は、基板18上に第1金属膜28を形成する第1金属膜形成工程と、第1金属膜28上に、パターンを形成しない基板18上の位置に対応する第1金属膜28が露出するようにマスクパターン38を形成するマスクパターン形成工程と、マスクパターン38をマスクとして第1金属膜28上に絶縁膜40を形成する絶縁膜形成工程と、マスクパターン38を除去し、メッキ法により、マスクパターン38を除去した第1金属膜28上に絶縁膜40をマスクとして少なくとも第2金属膜42を形成する第2金属膜形成工程と、を有する。

(もっと読む)

導電パターンの形成方法、薄膜トランジスタの製造方法、電気光学装置、及び電子機器

【課題】 特に液滴吐出法によって形成する配線等の導電パターンを、その成分元素の拡散を起こさせることなく良好に形成することができるようにした導電パターンの形成方法等を提供する。

【解決手段】 導電性材料を含有してなる機能液を基板P上に配置して導電パターン82を形成する方法である。基板P上に導電パターン82の形成領域に対応したバンクB1を形成する工程と、バンクB1によって区画された領域に機能液を液滴吐出法で配置する工程と、配置した機能液上にポリシラザン液を液滴吐出法で配置する工程と、バンクB1によって区画された領域に積層した機能液とポリシラザン液とに対して所定の処理を施すことにより、ポリシロキサンを骨格とする無機質層81で導電性材料からなる導電膜80を覆った導電パターン82を形成する工程と、を備えている。

(もっと読む)

半導体装置

【課題】ショットキー電極の耐湿性を向上し得る半導体装置を得る。

【解決手段】ショットキー電極であるゲート電極8は、TaNx層6とAu層7とを有している。TaNx層6は、Au層7と基板100との間で原子が拡散することを防止するための、バリアメタルとして機能する。TaNxはSiを含まないため、Siを含むWSiNよりも耐湿性が高い。そのためゲート電極8は、WSiN層を有する従来のゲート電極に比べて耐湿性が高い。また、窒素含有率xを0.8未満に設定することにより、従来のゲート電極に比べてショットキー特性が大幅に低下することを回避できる。あるいは、窒素含有率xが0.5以下の範囲内では、従来のゲート電極よりもショットキー特性を向上することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を大幅に増加させることなく、P型MOSFETとN型MOSFETとで異なる仕事関数を有する金属ゲート電極を形成する。

【解決手段】N型MOSトランジスタとP型MOSトランジスタとが形成された半導体装置であって、N型MOSトランジスタのゲート電極107nは、ゲート絶縁膜104に接するタングステン膜105nを具備し、P型MOSトランジスタのゲート電極107pは、ゲート絶縁膜104に接するタングステン膜105pを具備し、タングステン膜105nに含有される炭素の濃度が、タングステン膜105pに含有される炭素の濃度よりも低いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 周辺回路領域の電気的構成要素を形成する際に、設計マージンの減少を極力抑制できるようにする。

【解決手段】 周辺回路領域Pにおいて、シリコン窒化膜18が孔部19の内側壁面で且つ接続配線層17の外側壁面に形成されているため、隣接するコンタクト形成領域CPおよびCP間の平面的な最短距離が従来に比較して短くなったとしても形成位置およびその形成領域を極力調整することができ、周辺回路領域Pにおける設計マージンの減少を極力抑制できるようになる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 NiSiが用いられたシリサイド上ライナー窒化膜のエッチング特性を改善し、コンタクトホール底での過度のエッチングを防止する。

【解決手段】 半導体基板301の素子活性領域にシリサイド層308を形成する工程と、半導体基板上にライナーになるシリコン窒化膜309を形成する工程と、シリコン窒化膜上に層間絶縁膜を形成する工程と、層間絶縁膜にコンタクトホールを形成する工程とを含み、シリコン窒化膜は、原子層蒸着法によりジクロロシランとアンモニアを用いて曝露するサイクルを繰り返すことにより成膜され、成膜段階におけるアンモニアガスの曝露時間は、表面反応が平衡状態になる緩和時間の2〜10倍である。これにより、窒化膜中の塩素濃度を低減でき、Si−N結合が増やすことができるため、ウェットエッチング耐性を向上できる。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層によりエクステンション層およびソース・ドレイン層が形成された半導体装置において、合金層と半導体基板間に生じる接合リークを防止して、信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1には、活性領域を区画する素子分離絶縁膜2が形成されており、活性領域における半導体基板1上にゲート絶縁膜4を介してゲート電極5が形成されている。ゲート電極5の両側における半導体基板1上には、エピタキシャル成長層により形成された2つのエクステンション層6と、2つのソース・ドレイン層8が積層されている。ソース・ドレイン層8における素子分離絶縁膜2側の端部には、当該端部における合金層の形成を防止する保護層9が形成されている。保護層9から露出したソース・ドレイン層8には、合金層10が形成されている。

(もっと読む)

MOS型半導体装置及びその製造方法

【課題】

本発明は、LSI(大規模集積回路)の高集積化に好適なMOS型半導体装置の提供、すなわち、待機時のソースとドレイン間のリーク電流の削減、及び、動作時から待機時へ移行する時の、ソースとドレイン間の電流のカットオフ特性を改善したMOS型半導体装置の提供を課題とする。

【解決手段】

上記の課題を解決するため、絶縁性支持基板上の半導体領域の表面に形成されたゲート絶縁膜と、ゲート絶縁膜を介して前記半導体領域に接するように配置されたゲート電極と、ソース電極と、ドレイン電極を有するMOS型半導体装置を提供する。そして、上記のゲート電極は、主ゲート電極と前記主ゲート電極が有する側面の内の一の側面に接するように配置された副ゲート電極とを備えることを特徴とする。

(もっと読む)

MOS型半導体装置及びその製造方法

【課題】 CMOS構造の両方の極性の素子に対してコンタクト抵抗の低減を図り、Fin−MOSFET構造による移動度の増大を享受しつつ、製造コストの増大を回避する。

【解決手段】 MOS型半導体装置において、絶縁膜101上に薄壁状に形成された単結晶半導体層102と、半導体層102の両側壁面上にそれぞれゲート絶縁膜104を介して形成されたゲート電極105と、ゲート電極105に対応して半導体層102に形成されたソース・ドレイン領域と、半導体層102の一方の側壁面に形成され、ソース・ドレイン領域とショットキー接合を成す第1の金属−半導体化合物層112と、第1の金属−半導体化合物層112とは組成が異なり、半導体層102の他方の側壁面に形成され、ソース・ドレイン領域とショットキー接合を成す第2の金属−半導体化合物層122とを備えた。

(もっと読む)

101 - 120 / 123

[ Back to top ]