Fターム[4M104EE01]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412)

Fターム[4M104EE01]の下位に属するFターム

Fターム[4M104EE01]に分類される特許

21 - 40 / 123

炭化ケイ素半導体デバイスのためのエッジ終端構造及びその製造方法

【課題】炭化ケイ素デバイスのためのエッジ終端構造において、酸化膜などの絶縁層の境界面電荷の悪影響を中和し、多重フローティングガードリング終端では、この酸化膜電荷の変化に対する影響を少なくし、又は影響をなくす。

【解決手段】炭化ケイ素ベースの半導体接合に近接し、この半導体接合から間隔をおいて配置された、炭化ケイ素層中の複数の同心円のフローティングガードリングを有する。酸化膜などの絶縁層が、これらのフローティングガードリング上に設けられ、炭化ケイ素表面電荷補償領域が、これらのフローティングガードリング間に設けられ、この絶縁層に隣接している。かかるエッジ終端構造の製造方法もまた提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

少数キャリアの注入が抑制される炭化シリコン接合障壁ショットキーダイオード

【課題】接合障壁ショットキー(JBS)構造内のビルトインPiNダイオードの電流伝導を阻止する。

【解決手段】接合障壁ショットキー(JBS)一体構造が提供される。ダイオードのドリフト領域内に配置された炭化シリコン接合障壁領域を含む炭化シリコンショットキーダイオード、およびこの炭化シリコンショットキーダイオードを製造する方法も提供される。この接合障壁領域は、ダイオードのドリフト領域内にあって第1のドーピング濃度を有する第1の炭化シリコン領域と、ドリフト領域内にあって、第1の炭化シリコン領域とショットキーダイオードのショットキーコンタクトとの間に配置された第2の炭化シリコン領域とを含む。第2の領域は、第1の炭化シリコン領域およびショットキーコンタクトと接触する。第2の炭化シリコン領域は、第1のドーピング濃度よりも低い第2のドーピング濃度を有する。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

トレンチゲート型トランジスタの製造方法

【課題】トレンチゲート型トランジスタの製造方法において、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12の表面にトレンチ14を形成し、該表面とトレンチ14内に、熱酸化によりシリコン酸化膜15Aを形成し、これを覆うホトレジスト補強膜16、及びホトレジスト補強膜16を覆うホトレジスト層R2を形成する。そしてホトレジスト層R2及びホトレジスト補強膜16をエッチバックしてトレンチ14内にのみに残す。このホトレジスト層R2及びホトレジスト補強膜16をマスクとして、トレンチ14の側壁の上方のシリコン酸化膜15Aをエッチングして除去する。上記マスクを除去した後、熱酸化により、トレンチ14の側壁の上方にシリコン酸化膜15Aより薄いシリコン酸化膜15Bを形成する。その後、シリコン酸化膜15A,15B上にゲート電極18を形成する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】電流コラプスを抑制し、高出力動作可能な窒化物半導体装置を提供する。

【解決手段】ショットキ接触する電極(ゲート電極16)16とオーミック接触する電極(ソース電極17a、ドレイン電極17b)との間のIII−V族窒化物半導体層14表面に、ECRスパッタリング法により珪素膜15を形成する。ショットキ接触する電極16とIII−V族窒化物半導体層14との間に、珪素膜15を形成してもよい。

(もっと読む)

半導体装置の製造方法

【課題】基板に形成される第1の膜と第2の膜との重なり量を精度良く算出する。

【解決手段】半導体装置の製造方法は、基板の第1の領域及び第2の領域に第1の膜を形成する工程と、第2の領域の第1の膜の幅を測定する工程と、基板の第2の領域及び第3の領域に第2の膜を形成する工程と、第2の領域の第2の膜の幅及び第2の領域の第1の膜と第2の膜との距離を測定する工程と、第2の領域における第1の膜の幅の測定値、第2の膜の幅の測定値、第1の膜と第2の膜との距離の測定値及び第1の膜と第2の膜とに関する設計値に基づいて、第1の領域における第1の膜と第3の領域における第2の膜との重なり量を算出する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置、ショットキーバリアダイオードの特性を向上させる。

【解決手段】禁制帯幅の異なる第1膜と第2膜とが積層されたヘテロ接合部を少なくとも一つ有する積層体Hと、積層体Hと同層の積層物よりなるダミー積層体Dと、積層体Hとダミー積層体Dとの間に設けられた溝Gと、溝内部を含み積層体Hの上部からダミー積層体Dの上部まで延在するように配置され、積層体Hの第1の側壁に接するように配置され、積層体Hとの間にショットキー接続される第1電極SEと、積層体Hの第1の側壁と対向する第2の側壁に接するように配置された第2電極OHEと、で半導体装置を構成する。このように、ダミー積層体Dを残存させ、積層体Hとの間に溝Gを設け、溝内部に充填された第1電極SEによって、側壁コンタクトを実現したので、積層体Hをエッチングする際の欠陥が溝底部に発生する確率を低減でき、逆リーク電流を低減することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

半導体装置

【課題】高温・高電圧で動作させた場合でも故障の発生を抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、GaNキャップ層38上のソースフィンガー12と、ソースフィンガーと交互に配置されたドレインフィンガー14と、ソースフィンガーとドレインフィンガーとの間のゲートフィンガー16と、ゲートフィンガーの上面と側面を覆う第1絶縁膜44と、ゲートフィンガーとドレインフィンガーとの間の第1絶縁膜上に設けられたフィールドプレート26と、活性領域18の外側で第1絶縁膜上にフィンガー方向と交差方向に設けられソースフィンガーとその両側のフィールドプレートとを接続するフィールドプレート配線28と、を備え、フィールドプレートと第1絶縁膜の第1段差部46とは100nm以上離れ、フィールドプレート配線と第1絶縁膜の第2段差部48とは100nm以上離れている半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】歩留りの低下を抑制する。

【解決手段】開口部121.1の形成により、第1の半導体層110の上面のうち、上方に第2の半導体層120が形成されていない部分の少なくとも一部には、絶縁体130.1が形成される。開口部121.1には、絶縁体130.1を覆うようにソース電極S10が形成される。ソース電極S10は、第1の半導体層110と前記第2の半導体層120との界面と接するように形成される。

(もっと読む)

導電部形成方法、導電部及び発光装置

【課題】導電部の欠損を防止すること。

【解決手段】Al含有膜2からなるゲートラインLgやコンタクト部42などの導電部を形成する際に、下層保護導電膜/Al含有膜/上層保護導電膜の導体膜を成膜した後、その導体膜に改質処理として酸化処理を施して、上層保護導電膜3で覆われずにピンホールPから露出してしまったAl含有膜2部分に酸化保護領域4を形成することによって、Al含有膜2がレジストの剥離液などに晒されて消失してしまうことを防ぎ、導電部の欠損を防止した。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体チップの割れや欠けを防止し、デバイス特性を向上することができる半導体装置および半導体装置の製造方法を提供すること。

【解決手段】半導体チップ10の素子端部の側面には、分離層3が設けられている。また、半導体チップ10の素子端部には、凹部4によってひさし部5が形成されている。コレクタ層6は、半導体チップ10の裏面に設けられ、凹部4の側壁22および底面23に延在し、分離層3に接続されている。コレクタ層6の表面全体には、コレクタ電極7が設けられている。凹部4の側壁22上のコレクタ電極7は、最表面の電極膜の厚さが0.05μm以下となっている。半導体チップ10の裏面に設けられたコレクタ電極7は、はんだ層11を介して、絶縁基板12上に接合されている。はんだ層11は、半導体チップ10の裏面の平坦部21に設けられたコレクタ電極7を覆うように設けられている。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の形成工程におけるフォトレジスト層を露光した際に、露光不良によりレジスト残渣が発生しないようにすること。

【解決手段】本発明の電界効果トランジスタ100は、半導体基板1上にゲート電極を備えた電界効果トランジスタで、半導体基板1上に設けられた誘電体膜2と、この誘電体膜2の開口部に設けられたフット部8と、このフット部8上及び誘電体膜2上に設けられたヘッド部9とを備え、誘電体膜の膜厚t1が、0.9k×λ/2|n1−n2|<t1<1.1k×λ/2|n1−n2|(ただしkは自然数であり、屈折率n1は所定の波長λを有する露光光に対する誘電体膜の屈折率n1(>2.1)、屈折率n2はフォトレジスト層の屈折率)である。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

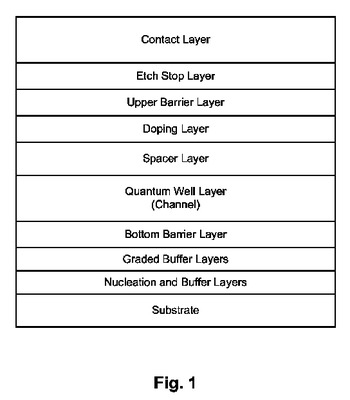

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

21 - 40 / 123

[ Back to top ]