Fターム[4M104EE01]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412)

Fターム[4M104EE01]の下位に属するFターム

Fターム[4M104EE01]に分類される特許

61 - 80 / 123

半導体装置の製造方法

【課題】 縦型の半導体装置100を製造する方法において、半導体ウェハ2の端部側面2cを研磨した場合でも、半導体ウェハ2の端部側面2cにめっき14が成長することを抑制することができる製造方法を提供すること。

【解決手段】 本方法は、半導体ウェハ2の表面2aに表面電極4を形成する表面電極形成工程と、その後に、半導体ウェハ2の端部側面2cを研磨する側面研磨工程と、その後に、半導体ウェハ2の裏面2bを研磨する裏面研磨工程と、その後に、半導体ウェハ2の裏面2bに裏面電極10を形成する裏面電極形成工程と、その後に、半導体ウェハ2の端部側面2cに酸化膜12を形成する保護膜形成工程と、その後に、表面電極4をめっき処理するめっき処理工程を備えている。酸化膜12によって、めっき処理工程において半導体ウェハ2の端部側面2cにめっき14が成長することが抑制される。

(もっと読む)

JBSの製造方法

【課題】N型ショットキー接合界面にPtまたはAuが到達してしまうおそれを低減する。

【解決手段】N+型半導体基板1上のN−型エピタキシャル層2に複数のトレンチ2aを形成し、トレンチ2aの側面2a1および底面2a2を介してP型不純物を導入して拡散させることにより、ガードリング部4とP型層5とを形成し、トレンチ2aの側面2a1上および底面2a2上に酸化膜3を形成し、酸化膜3のうち、トレンチ2aの底面2a2に隣接する部分に開口2bを形成し、半導体チップの表面全体にPtまたはAu7を蒸着し、蒸着されたPtまたはAu7の上からポリシリコン8を堆積させてトレンチ2aの内部にポリシリコン8を充填し、トレンチ2aの底面2a2の開口3bを介してPtまたはAu7をトレンチ2aの底面2a2の下方に拡散させる。

(もっと読む)

ショットキーバリアダイオードの製造方法およびショットキーバリアダイオード

【課題】逆方向電圧印加時の漏れ電流を低減することができるショットキーバリアダイオードの製造方法およびショットキーバリアダイオードを提供する。

【解決手段】炭化珪素からなる半導体層1上に、炭化珪素、酸素、および窒素を含むNO酸化膜3を形成した後、NO酸化膜3を貫通する孔を形成する。この工程によって露出した半導体層1の表面のN原子4を除去する。この工程によって表面のN原子4が除去された半導体層1上に、半導体層1とショットキー接合を形成する電極7を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置

【課題】電極パッド上に所望の形状でめっき層を形成できる構成を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、グラウンドに接続された電極パッド3aと、電極パッド3aの上に形成されためっき層6aと、半導体基板1のうち、電極パッド3aの下方に位置する領域を区画する絶縁膜7とを備えている。ウェハ裏面の一部または全部が電極パッド3aと電気的に分離される。

(もっと読む)

半導体装置とその製造方法

【課題】 半導体装置の小型化を実現するとともに、高い耐圧特性を持つ半導体装置を提供する。

【解決手段】 ダイオード100は、SiC基板2の表面にn型のドリフト層6と、p型のガードリング領域8と、アノード電極10と、カソード電極12を備えている。ダイオード100では、アノード電極10の端部10aを覆う位置からSiC基板2の側面まで連続して絶縁膜であるSOG4が形成されている。ダイオード100に逆方向の高電圧が印加されたときに、SOG4が接地電位となるアノード電極10の端部10aに接する位置から高電位となるSiC基板の側面2aに接する位置までの距離を確保することができる。アノード電極10と終端領域の距離を離さなくても、SOG4の距離を確保することによって、沿面放電の発生を抑制することができる。

(もっと読む)

銅への改善された接着性および銅エレクトロマイグレーション耐性

【課題】本発明は、パターン形成された導電性金属層、およびパターン形成された障壁誘電体層との間に改善された接着性を与えるものである。

【解決手段】本発明は、パターン形成された導電性金属層、通常は銅層、およびパターン形成された障壁誘電体層との間の改善された接着に関する。

改善された接着性を有するこの構造は、パターン形成された障壁誘電体層とパターン形成された導電性金属層との間に接着層を含んでいる。この接着層は、銅のバルク電気抵抗率を増加することなしに、金属層と障壁層との間の接着力を、向上させる。改善された接着性を有する構造を作る方法は、パターン形成された導電性金属層を有機金属前駆体に熱的に暴露させ、少なくとも、パターン形成された導電性金属層の表面上に、接着層を堆積させる工程を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

(もっと読む)

ダイオード

【課題】 n型半導体領域の表面の一部にp型半導体領域が設けられたダイオードにおいて、内在するpn接合ダイオードを活用して順方向抵抗を低減化する技術を提供する。

【解決手段】 n型半導体領域22と、n型半導体領域22の表面の一部に設けられているp型半導体領域14と、n型半導体領域22の表面とp型半導体領域14の表面に接しており、少なくともn型半導体領域22の表面にショットキー接合Jbしているアノード電極2(表面電極)と、n型半導体領域22に接する右側面30b(第1側面)及び左側面30a(第2側面)を有する絶縁領域30を備えている。右側面30bは、ショットキー接合Jbの下方に位置する第2n型半導体領域22bに対向しており、左側面30aは、n型半導体領域22とp型半導体領域14とのpn接合13の下方に位置する第1n型半導体領域22aに対向している。

(もっと読む)

半導体装置

【課題】GaAsなどの閃亜鉛鉱構造と負のピエゾ電気定数e14を有する化合物半導体材料よりなる半導体基板や半導体層の良好な結晶性を維持した状態で、電極とのコンタクト抵抗を下げる。

【解決手段】半絶縁性のGaAsから構成され、主表面が(100)面とされた基板101の上に、圧縮性の内部応力を伴う絶縁体から構成されて[0−11]方向に延在するストライプ状の絶縁パターン111と、絶縁パターン111のとなりの、導電性領域102が形成されている領域の基板101の上に形成されたオーミック電極103とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】工程数の削減を図りつつ、かつセンサ素子などが形成される非シリサイド領域の実質的な開口を狭めることなく、シリサイド領域のみにシリサイド層を形成することが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】シリコン基板1の表面側をセンサ領域1sとしての非シリサイド領域とシリサイド領域とに分離する。センサ領域1sを露出させる状態でシリコン基板1上にマスクパターン19を形成する。マスクパターン19から露出したセンサ領域1sにおけるシリコン基板1の表面に、選択的にシリサイドブロック膜21を成膜する。マスクパターン19を除去してシリサイドブロック膜21が形成されたシリコン基板1上に金属膜25を成膜した後、熱処理を行うことによりセンサ領域1s以外のシリサイド領域におけるシリコン基板の表面層に選択的にシリサイド層を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】

裏面電極を有するフェイスダウン型の半導体装置の製造方法では、各工程において裏面電極を薬液等から保護するため、何度も保護テープを仮貼りする必要があった。

【解決手段】

本発明では、ソース電極7及びドレイン電極9上に下地電極11を無電解めっき法により形成する工程を経た後に、半導体ウエハを裏面側から研削する工程と、半導体ウエハの裏面上に裏面電極12を形成する工程を行い、その後に裏面電極12上にエポキシ樹脂テープ13を永久貼り付けする工程と、下地電極11上にバンプ電極14を形成する工程と、を行う。

(もっと読む)

鉛フリーの伝導性組成物、および半導体デバイスの製造における使用方法:フラックス材料

本発明の実施形態は、シリコン半導体デバイス、および太陽電池デバイスの前面に使用するための伝導性銀ペーストに関する。  (もっと読む)

(もっと読む)

ショットキーバリアダイオード

【課題】逆方向リーク電流を低減させながらも順方向電圧降下を抑制可能なショットキーバリアダイオードを提供する。

【解決手段】表面に第1導電型の半導体層を有する半導体基板と、前記第1導電型の半導体層内に表面から所定の深さに面方向に配列された埋め込みバリアと、前記第1導電型の半導体層の表面で前記埋め込みバリアを囲むように環状に形成された第2導電型の半導体層からなるガードリングと、前記第1導電型の半導体層に接するように配設された金属層とを具備したショットキーバリアダイオードであって、前記埋め込みバリアは、電気的に浮遊状態であることを特徴とする。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】空気の層に基づくパッシベーションの膜の不整合性による不連続性の問題を解決し、高耐圧特性に優れたトランジスタの提供を課題とする。

【解決手段】III−V族窒化物からなる半導体層と、その上に、ソース/ドレイン電極と、両サイドを前記ソース/ドレイン電極に挟まれ、かつゲート電極を備えるIII−V族窒化物からなる半導体よりも高い誘電率を有する誘電体膜とが形成されており、前記ゲート電極が、前記誘電体膜の一部を窒化したものであり、さらにセカンドメタルで被覆されていることを特徴とするヘテロ接合電界効果型トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】キャリア移動度を一層向上できる半導体装置を提供する。

【解決手段】この半導体装置は、ゲート3の側面とソース/ドレイン6のエクステンション領域6aとを被覆する様に側面視断面L字状に形成されたサイドウォール5bと、ゲート3上およびソース/ドレイン6のコンタクト領域6b上に形成されたシリサイド層7と、サイドウォール5bおよびシリサイド層7を被覆する様に形成されたストレスライナー膜8とを備え、ソース/ドレイン6のコンタクト領域6bが半導体基板1の半導体素材(Si)よりも格子間隔の大きい半導体素材(SiGe)により形成され且つストレスライナー膜8が圧縮型であり、または、ソース/ドレイン6のコンタクト領域6bが半導体基板1の半導体素材(Si)よりも格子間隔の小さい半導体素材(SiC)により形成され且つストレスライナー膜8が引張型であるものである。

(もっと読む)

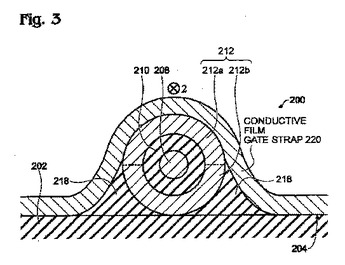

コア−シェル−シェル・ナノワイヤトランジスタ、およびその製造方法

コア−シェル−シェル(CSS)ナノワイヤトランジスタ(NWT)であって、表面を持つ基板と、半導体コアと、該半導体コアを囲む絶縁性シェルと、該絶縁性シェルを囲む導電性シェルとを含む円柱形のCSSナノ構造体であって、上記表面上にある下側半円柱を有するCSSナノ構造体と、上記CSSナノ構造体の中央部にある上記導電性シェルから形成されているゲート電極と、上記基板の表面と、上記CSSナノ構造体の中央部にある上記下側半円柱との間に配置された絶縁性凹形ストリンガと、上記CSSナノ構造体の中央部にある、ゲート電極および上記絶縁性凹形ストリンガの上に形成されている導電膜ゲートストラップと、上記CSSナノ構造体の両端部にある、上記半導体コアの複数の露出領域に形成されているソース/ドレイン(S/D)領域と、を含むコア−シェル−シェル(CSS)ナノワイヤトランジスタ(NWT)。  (もっと読む)

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】 半導体素子の表面に金属電極を形成する場合、バリア膜を形成することで、半導体素子の表面にめっき法を用いて厚い金属電極を形成することができる。しかし、バリア膜は導電性があるため、金属電極間に存在するバリア膜は絶縁する必要がある。

【解決方法】 層間絶縁膜12が形成された半導体素子14の表面に導電性のあるバリア膜10を形成する。バリア膜10の表面に金属電極5を形成した後に、半導体素子14を熱酸化する。金属電極4が形成されていない領域のバリア膜10cは酸化され絶縁性を示す。これにより金属電極同士は絶縁される。また金属電極5が形成されている領域のバリア膜10a,10bは金属電極5がマスクの役割を果し、酸化されず導電性を保つ。これにより金属電極5と半導体素子14との導通は確保される。

その後、金属電極5表面の酸化膜22を除去することで、金属電極5の導通も確保される。

(もっと読む)

化合物半導体装置とその製造方法

【課題】ゲート電極の近傍での耐圧が高められた化合物半導体装置とその製造方法を提供すること。

【解決手段】SiC基板20と、SiC基板20の上に形成された電子走行層21と、電子走行層21の上に形成された電子供給層23と、電子供給層23の上に互いに間隔をおいて形成されたソース電極27a及びドレイン電極27bと、ソース電極27aとドレイン電極27bの間の電子供給層23上に形成され、SiC基板20に向かって狭径となる開口29bを備えた保護絶縁膜30と、開口29b内の電子供給層23上に形成されたゲート電極32とを有する化合物半導体装置による。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】大電流容量を有する半導体装置を提供する。

【解決手段】半導体装置は、エピウエハ110と、絶縁膜と、第1の電極と、導電層と、第2の電極160とを備えている。エピウエハ110は、高欠陥領域111と、高欠陥領域111よりも欠陥密度の低い低欠陥領域112とを含み、主表面113と、主表面113と反対側の裏面114とを有する。絶縁膜は、エピウエハ110の主表面113における高欠陥領域111を覆うように形成される。第1の電極は、低欠陥領域の上に形成され、絶縁膜を介して隣り合う。導電層は、絶縁膜を介して隣り合う第1の電極を電気的に接続する。第2の電極160は、エピウエハ110の裏面114上に形成されている。

(もっと読む)

61 - 80 / 123

[ Back to top ]