Fターム[4M104EE01]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412)

Fターム[4M104EE01]の下位に属するFターム

Fターム[4M104EE01]に分類される特許

41 - 60 / 123

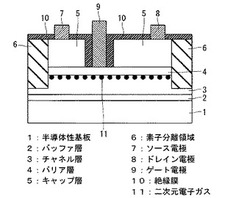

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】表示品質と開口率を向上することができる液晶表示装置及びその製造方法を得る。

【解決手段】基板上に位置し、相互に交差して画素領域を定義するゲート配線204及びデータ配線と、ゲート配線に接続されるゲート電極202と、ゲート電極上に位置するゲート絶縁膜と、ゲート絶縁膜上に位置するアクティブ層220と、アクティブ層上に位置し、相互に離間されたソース電極234及びドレイン電極236と、アクティブ層及びソース電極間、並びにアクティブ層及びドレイン電極間に位置するオーミックコンタクト層と、アクティブ層上に位置し、ソース電極及びドレイン電極の内側に向かう二つの側面を有し、二つの側面のうち、少なくとも一つは、ソース電極及びドレイン電極の内側間に位置するシールドパターン222と、画素領域に位置し、ドレイン電極に接続される画素電極とを設けた。

(もっと読む)

半導体素子及びその製造方法

【課題】埋め込みビットラインコンタクトホール内にディフュージョンバリアーを形成して素子の特性を改善する。

【解決手段】半導体基板100をエッチングして複数個のピラーパターンを形成する段階と、前記ピラーパターンの表面に絶縁層を蒸着する段階と、前記ピラーパターンの一側の前記絶縁層の一部を除去して前記ピラーパターンが露出されるコンタクトホールを形成する段階と、前記コンタクトホール内にバリアー膜170aを形成する段階と、前記コンタクトホールと接する前記ピラーパターン内に接合180を形成する段階と、前記ピラーパターンの間の底部に前記コンタクトホールと接続して形成された埋め込みビットラインとを含む。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

ショットキーバリアダイオード及びその製造方法

【課題】窒化物系ショットキーバリアダイオードを高耐圧化し、且つリーク電流が低減する。

【解決手段】ショットキーバリアダイオード80には、厚み方向に貫通するトレンチ7を有するシリコン基板と、シリコン基板上に設けられ、シリコン基板よりもバンドギャップが大きなAlGaN層2と、AlGaN層2上に設けられる絶縁膜3と、AlGaN層2及びトレンチ7上に設けられ、シリコン基板1よりもバンドギャップが大きなn型GaN層4と、絶縁膜3上に設けられ、側面がn型GaN層4と接する埋め込み絶縁膜5と、トレンチ7と相対向するn型GaN層4上に設けられるショットキー電極6と、トレンチ7中に露出されるn型GaN層4の表面上に設けられるオーミック電極8とが設けられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造過程において生じるウエハ外周部分からのパーティクルの発生を防止し、十分な歩留りを実現する。

【解決手段】ウエハにゲート電極となる導電膜4、5を形成する第一工程と、導電膜4、5の中の、ウエハの外周部分に形成された導電膜4、5の上に選択的に保護膜7を形成する第二工程と、導電膜4、5の上に第一レジストパターンを形成し、前記第一レジストパターンをマスクとして導電膜4、5をエッチングすることにより、ゲート電極を形成する第三工程と、前記ゲート電極を覆う層間絶縁膜を形成する第四工程と、前記層間絶縁膜の上に第二レジストパターンを形成し、前記第二レジストパターンをマスクとして前記層間絶縁膜をエッチングすることにより、コンタクトホールを形成する第五工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

ダイオード

【課題】 n型半導体領域の表面の一部にp型半導体領域が設けられたダイオードにおいて、内在するpn接合ダイオードを活用して順方向抵抗を低減化する技術を提供する。

【解決手段】 n型半導体領域22と、n型半導体領域22の表面の一部に設けられているp型半導体領域14と、n型半導体領域22の表面とp型半導体領域14の表面に接しており、少なくともn型半導体領域22の表面にショットキー接合Jbしているアノード電極2(表面電極)と、n型半導体領域22に接する右側面30b(第1側面)及び左側面30a(第2側面)を有する絶縁領域30を備えている。右側面30bは、ショットキー接合Jbの下方に位置する第2n型半導体領域22bに対向しており、左側面30aは、n型半導体領域22とp型半導体領域14とのpn接合13の下方に位置する第1n型半導体領域22aに対向している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

半導体デバイス及びその形成方法

【課題】応力ライナによるコンタクト形成の問題が起きない、相補型金属酸化膜半導体(CMOS)デバイスの製造方法を提供する。

【解決手段】シリコン基板層上の二酸化シリコン層102と、凹んだソース/ドレイン・トレンチを有する相補型金属酸化膜半導体(CMOS)デバイスを準備し、凹んだソース/ドレイン・トレンチ内に窒化物応力ライナ104を堆積し、その上に酸化物層106を堆積する。CMOSデバイスをハンドリング・ウェハ上に置きシリコン基板層を除去し二酸化シリコン層102をエッチングしてソース/ドレイン領域170の一部に当接する開口部を形成しコンタクト180を形成する。

(もっと読む)

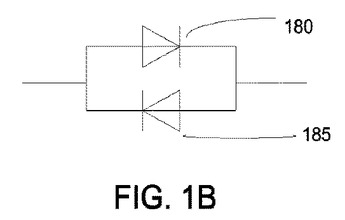

ショットキーダイオードスイッチおよびそれを含むメモリユニット

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】イオン注入された領域であるイオン注入領域が除去されない炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】この発明にかかる炭化珪素半導体装置の製造方法は、炭化珪素層の表層にイオン注入により環状のイオン注入領域を選択的に形成する工程と、前記イオン注入領域が形成された前記炭化珪素層を活性化アニールする工程と、前記炭化珪素層の表面の全面に犠牲酸化膜を形成する工程と、前記イオン注入領域にあたる前記犠牲酸化膜上にフォトレジストを形成する工程と、前記フォトレジストをマスクとして前記犠牲酸化膜を除去する工程と、前記フォトレジストと前記犠牲酸化膜をマスクとして前記犠牲酸化膜と前記活性化アニールの際に前記炭化珪素層の表層に形成される変質層を除去する工程とを備える。

(もっと読む)

逆耐圧を有する縦型窒化ガリウム半導体装置

【課題】逆阻止能力を有し、低オン抵抗で高速スイッチング特性を有する素子を提供すること。

【解決手段】シリコン基板101と、シリコン基板101上に形成されたバッファ層102,103と、バッファ層102、103上に形成された窒化ガリウム半導体層104と、シリコン基板101の裏面からシリコン基板101ならびにバッファ層102、103を貫通して窒化ガリウム半導体層104に達する深さで形成されたトレンチ溝112と、このトレンチ溝112の中に形成された金属膜113と、を備え、金属膜113と窒化ガリウム半導体層104とがショットキー接合を形成する逆耐圧を有する窒化ガリウム半導体装置とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】生産性に優れたフレキシブル半導体装置を提供する。

【解決手段】可撓性を有するフレキシブル半導体装置100であり、樹脂フィルム30と、樹脂フィルム30の上に形成された金属層10とを備え、金属層10は、絶縁壁51によって分断され、且つ、絶縁壁51の一端53は樹脂フィルム30に接しており、絶縁壁51によって金属層10から、ゲート電極10g、ソース電極10sおよびドレイン電極10dが形成されている。ゲート電極10gの上には、絶縁壁51に接するゲート絶縁膜22が形成されており、ゲート絶縁膜22の上には半導体層20が形成されている。

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部に対するウエルコンタクトホールの位置合わせ精度を向上する。

【解決手段】半導体基板にウエル領域2を形成する第1の工程と、前記半導体基板に、第1のアライメントマークと、前記ウエル領域2にアクティブ領域を分離する素子分離部7とを形成する第2の工程と、前記半導体基板の上に、第2のアライメントマークと、MOSトランジスタのゲート電極9とを形成する第3の工程と、前記ゲート電極9とともにソース電極又はドレイン電極となるべき半導体領域を形成する第4の工程と、前記半導体基板及び前記ゲート電極9の上に絶縁膜14を形成する第5の工程と、前記第1のアライメントマークを基準として決められた位置に、ウエルコンタクトホールを形成する第6の工程と、前記第2のアライメントマークを基準として決められた位置に、前記絶縁膜14を貫通するコンタクトホールを形成する第7の工程とを備える。

(もっと読む)

電界効果半導体装置及びその製造方法

【課題】オン抵抗及びゲートリーク電流の小さいノーマリオフ特性を有し、且つ特性のばらつきが少ない電界効果半導体装置を提供する。

【解決手段】第1の半導体層4と、前記第1の半導体層上に配置され且つ前記第1の半導体層よりも格子定数が小さい材料で形成された第2の半導体層5aと、前記第2の半導体層上に配置され且つ前記第1の半導体層よりも格子定数が小さい材料で形成された第3の半導体層5bとを備える主半導体領域と、前記主半導体領域上に配置された第1の主電極6と、前記主半導体領域上に配置された第2の主電極7と、前記主半導体領域上における前記第1の主電極と前記第2の主電極との間に配置され且つ前記第3の半導体層を貫通する凹部と、前記凹部上に配置される金属酸化物半導体膜10と、前記金属酸化物半導体膜上に配置されるゲート電極8と、を備えることを特徴とする電界効果半導体装置。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程によりアモルファス化される半導体基板表面が、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を著しく低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に緩衝膜を設けることで、高濃度不純物のイオン注入を行っても、この領域の半導体基板表面がアモルファス化することを防ぐことができる。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極部のしきい値電圧の変動が抑制される半導体装置と、その製造方法を提供する。

【解決手段】素子形成領域2では、P−HK膜6と、仕事関数制御用の金属膜8が形成されている。素子形成領域3では、N−HK膜7と、仕事関数制御用の金属膜9が形成されている。その金属膜8,9の上にポリシリコン膜10およびニッケルシリサイド膜11が形成されている。境界側壁絶縁膜5は、P−HK膜7とN−HK膜6とに接触する態様でP−HK膜7とN−HK膜6との間に介在するとともに、金属膜8と金属膜9とに接触する態様で金属膜8と金属膜9との間に介在している。

(もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタの電気特性や信頼性はチャネル領域に不純物元素が拡散することで損なわれてしまう。アルミニウム原子が酸化物半導体層へ拡散し難い薄膜トランジスタを提供する。

【解決手段】インジウム、ガリウム、及び亜鉛を含む酸化物半導体層を有した薄膜トランジスタ150がアルミニウムを第1成分とする第1導電層(114a、114b)と高融点金属材料からなる第2導電層(115a、115b)を積層したソース電極層及びドレイン電極層(117a、117b)を有し、酸化物半導体層113が、前記第2導電層(115a、115b)および酸化アルミニウムを第1成分とするバリア層(116a、116b)と接することで、アルミニウム原子の酸化物半導体層113への拡散を抑制する。

(もっと読む)

41 - 60 / 123

[ Back to top ]