Fターム[4M104EE10]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 基板面下 (21)

Fターム[4M104EE10]に分類される特許

1 - 20 / 21

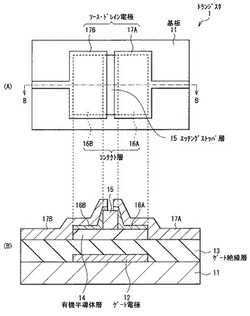

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

半導体装置

【課題】順方向電圧降下の増大が抑制され、且つ順方向サージ耐量の高い、整流機能を有する半導体装置を提供する。

【解決手段】互いに対向する第1の主面110から第2の主面120に向かって延伸し、且つ底部が第2の主面120に達しない複数の溝部15が形成された第1導電型の半導体積層体10と、それぞれの外縁領域の一部が溝部15の側面に露出するように半導体積層体10の第1の主面110に互いに離間して埋め込まれた第2導電型の複数のアノード領域20と、アノード領域20の形成されていない領域において半導体積層体10とショットキー接合を形成し、且つアノード領域20とオーミック接合を形成して、半導体積層体10の第1の主面110に配置されたアノード電極30と、半導体積層体10の第2の主面120に配置されたカソード電極40とを備える。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

半導体素子およびその製造方法

【課題】 サドルフィン形態のチャンネルを形成する際に、ゲートパターンとプラグとの間のブリッジ発生を防止することが可能な半導体素子およびその製造方法を提供する。

【解決手段】 半導体素子は、半導体基板と、半導体基板内に活性領域を限定するように形成された素子分離膜と、活性領域および素子分離膜に形成されたゲート用リセスパターンと、リセスパターン内およびリセスパターン上に形成されたゲートパターンと、ゲートパターンを覆うように形成されたゲートスペーサとを含み、ゲート用リセスパターンは、活性領域では第1深さを有し、素子分離膜では第1深さよりも深い第2深さを有し、ゲートパターンと素子分離膜のゲート用リセスパターン上部側面との間には空間が形成されて、ゲートスペーサが前記空間を埋め立てる。

(もっと読む)

半導体装置及びその製造方法

【課題】高出力を得やすい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体装置は、基板100と、基板100上に形成された化合物半導体層110と、化合物半導体層110を用いて作製されたトランジスタ120と、基板100の裏面から化合物半導体層110の厚さ方向の途中まで除去された除去領域130と、除去領域130に埋め込まれ、前記基板より高い熱伝導度を有する高熱伝導性絶縁体131とを備えるものである。

(もっと読む)

半導体装置とその製造方法

【課題】 ヘテロ接合を有する半導体装置において、素子領域から電流がリークすることを抑制する。

【解決手段】 半導体装置100は、バンドギャップを異にする窒化物半導体層6、10が積層されている半導体積層部11を有しており、半導体積層部11が素子領域100aと素子領域100aの周囲に形成されている素子分離領域100bを備えている。素子領域100aは、素子分離領域100bにより他の領域から絶縁されている。半導体装置100は、素子領域100a内の半導体積層部11の表面に、主電極に接続する一対の電極群24,16を形成する電極群形成工程と、素子分離領域100b内の半導体積層部11の表面に、スパッタ法を用いてスパッタ層12を形成するスパッタ工程を備えている。

(もっと読む)

半導体装置

【課題】 外部電荷の影響を軽減した半導体装置を提供すること。

【解決手段】 半導体装置10は、n型MOSFETが作り込まれている中心領域10Aとその中心領域10Aの周囲に形成されている終端領域10Bを半導体基板21内に有している。終端領域10Bは、中心領域10Aと終端領域10Bを連続して形成されているn−型のドリフト領域26と、p型のガードリング42と、隣接するガードリング42の間であってドリフト領域26の表面の少なくとも一部に形成されている絶縁体領域44を備えている。

(もっと読む)

デュアル配線型集積回路チップ

【課題】 デュアル配線型集積回路チップ及びその製造方法を提供する。

【解決手段】 両面に配線レベルを有する半導体デバイス、及び、両面のデバイス及び配線レベルへのコンタクトを有する半導体構造体を製造する方法を提供する。本方法は、シリコン・オン・インシュレータ基板上のデバイスへの第1コンタクトと、第1コンタクトへの第1側面上の配線レベルとを有するデバイスを製造するステップと、下部シリコン層を除去して埋込み酸化物層を露出させるステップと、埋込み酸化物層を貫通してデバイスへの第2コンタクトを形成するステップと、埋込み酸化物層の上に第2コンタクトへの配線レベルを形成するステップとを含む。

(もっと読む)

トレンチゲート電界効果トランジスタおよびその形成方法

一体的に統合されたトレンチFETおよびショットキーダイオードを含む構造体であって、半導体領域内に伸張するゲートトレンチと、ゲートトレンチの各側面に位置し、実質的に三角形状のソース領域と、隣接するトレンチ間における半導体領域内部に伸長するコンタクト開口と、コンタクト開口を満たし、各ソース領域の傾斜した側壁部の少なくとも一部に沿ってソース領域と電気的に接触し、且つコンタクト開口の底部に沿って半導体領域と電気的に接触し、且つ半導体領域とショットキーコンタクトを形成する導電体層と、を含む。 (もっと読む)

1 - 20 / 21

[ Back to top ]