Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

201 - 220 / 578

半導体装置

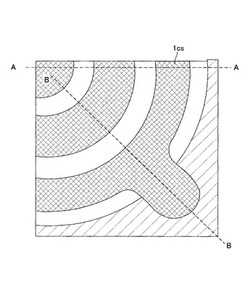

【課題】素子の高耐圧化に伴い反転領域を介して流れるリーク電流を低減する方法の提供。

【解決手段】所望の不純物濃度を有する半導体層を備えた半導体基板と、半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、半導体層表面を覆う絶縁膜と、絶縁膜を貫通し、ソースコンタクト開口部に形成されたソース電極と、半導体層内に形成され、ソース電極に電気的に接続されたボディ領域及びソース領域と、トレンチゲート周縁部でトレンチゲートに接続されたゲート周辺配線と、ソース電極と同一表面上で、ソース電極から離間して形成され、ゲート周辺配線に接続されるゲート電極と、ドレイン電極とを具備し、周縁部のスクライブ領域の拡散領域と、デバイス周縁部の拡散領域との間の半導体基板表面に、チャネルストッパ1csを形成し、反転領域形成を抑制する。

(もっと読む)

半導体装置

【課題】GaN−HEMTにおいて、オーミックコンタクト抵抗を0.1Ω/mm以下に低減する。

【解決手段】GaN層19、及びGaN層に起因して発生した活性領域11aを含む下地13と、活性領域上に形成されているゲート電極15と、活性領域に形成されており、ゲート電極を挟んで互いに離間しかつ対向して形成されている第1及び第2主電極17a及び17bとを具える。そして、第1及び第2主電極と活性領域とが重なる第1及び第2重なり領域29a及び29bの、ゲート幅方向31に沿った幅WC1及び幅WC2は、ゲート電極と活性領域とが重なる第3重なり領域35の、ゲート幅方向に沿った幅WGの10倍以上である。

(もっと読む)

半導体装置

【課題】順方向動作において順方向特性を比較的保持しながら逆方向リーク電流を減少することができる半導体装置を提供する。

【解決手段】半導体装置(横型SBD)1において、二次元キャリアガス層23が生成される第1の窒化物系半導体領域21上にバリア層として機能する第2の窒化物系半導体領域22を有する窒化物系半導体機能層2と、二次元キャリアガス層23の一端に電気的に接続された第1の主電極3と、二次元キャリアガス層23の他端に電気的に接続された第2の主電極4と、第1の主電極3と第2の主電極4との間に配設され、第1の主電極3に電気的に接続されるとともに、二次元キャリアガス層23のキャリア密度を減少する金属酸化物膜6とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】電流が、縦方向、横方向、そして縦方向と連続的に流れる半導体装置において

縦方向並びに横方向の電流経路に係る電気抵抗を低減し、高効率、高性能な半導体装置を実現する。

【解決手段】本発明の半導体装置は、半導体基板の表面側にドレインを共有するMOS構造が2つ形成され、かつ、半導体基板の裏面側のN+型ドレイン層7の内部に、一方のMOS構造のドレイン領域から他方のMOS構造のドレイン領域まで、延在して形成された複数の堀状の開口部4を有する。堀状の開口部4はN+型ドレイン層7の内部の、N+型ドレイン層7とN−型エピ層8の境界近傍まで、深く形成されている。そして、堀状の開口部4の中には裏面電極5と電気的に接続された、N+型ドレイン層7に比べて抵抗の低い、金属電極6が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート絶縁膜破壊が抑制された半導体装置を提供する。

【解決手段】ゲート電極給電用シリコンピラー5の表面を覆うゲート電極8と重なる位置に設けられたコンタクトホール13を備え、コンタクトホール13には、コンタクトホール13の底部から少なくともゲート電極8の上面よりも上方まで充填されたゲートリフトポリシリコン14と、ゲートリフトポリシリコン14上に配置されたゲートコンタクト15とが設けられていることを特徴とする半導体装置を採用する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】応答特性が良く電流コラプスの問題を改善できると同時に、デバイス設計値どおりのゲートリセス部を再現性よく形成しうる窒化物半導体装置を得ること。

【解決手段】基板1上に形成された第1の窒化物半導体からなるチャネル層2と、チャネル層2の上部に形成され、第1の窒化物半導体よりも大きなバンドギャップを有する第2の窒化物半導体からなる第1の電子供給層3aと、第1の電子供給層の上部で離隔した2つの領域として形成され、第1の窒化物半導体と同じか、又はこれよりも大きなバンドギャップを有する第3の窒化物半導体からなる第2の電子供給層3bとを備えている。

第1と第2の電子供給層3a、3bの間には、第2の電子供給層3bよりもドライエッチング速度が小さい材料からなるエッチングストッパ層4が形成されており、この層4の上部で2つの領域に挟まれたゲートリセス部を、ゲート電極5が充填するように形成されている。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、画素スイッチング用TFTの光リーク電流の発生を低減し表示画像の高品質化を図る。

【解決手段】基板上に、走査線11、走査線に交差するデータ線6、画素電極、第1及び第2の方向のうち一方の方向に沿ったチャネル長を有するチャネル領域30a3、第2の方向に沿ったソース長を有するソース領域30a1、第1の方向に沿ったドレイン長を有するドレイン領域30a5、チャネル領域及びソース領域間に形成された第1の接合領域30a2、並びにチャネル領域及びドレイン間に形成された第2の接合領域30a4を有し、ドレイン領域で折れ曲がっている半導体層30a、チャネル領域に対向する本体部30b1、折れ曲がった部分に沿って少なくとも第2の接合領域を包囲する包囲部30b2を有するゲート電極30bと、包囲部から立ち上がり又は立ち下がっており、第2の接合領域を囲む側壁部31とを備える。

(もっと読む)

トランジスタ素子およびその製造方法

【課題】

ベース電極とコレクタ半導体の電荷注入障壁の制御が可能である、高性能な縦型薄膜のトランジスタ素子および製造方法を提供する。

【解決手段】

基板10上に、第一電極20と、コレクタ半導体層30と、ベース電極40と、エミッタ半導体層31と、第二電極21とを順次積層するトランジスタ素子において、コレクタ半導体層とエミッタ半導体層の間にベース電極が存在するようにするとともに、コレクタ半導体層が金属酸化物よりなることを特徴とする。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化と信頼性の向上を図ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】化合物半導体基板に形成されたメサ22と、メサ22の壁面に形成された曲率表面を有する側壁16と、メサ22上に形成されるゲート電極と、ゲート電極と一体化され、側壁16の表面に形成されるゲートメタル18と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 ジャンクションバリアショットキダイオード構造の特性を向上する。

【解決手段】 半導体装置の製造方法は、n型の半導体基板にp型半導体領域をその上面の一部に露出するように形成するp型領域形成工程と、半導体基板の上面に露出するn型半導体領域にショットキ接触するショットキ電極を形成する第1電極形成工程と、半導体基板の上面に露出するp型半導体領域にオーミック接触するオーミック電極を形成する第2電極形成工程を備えている。オーミック電極は、ショットキ電極とは異なる材料によって形成される。そして、第1電極形成工程は、第2電極形成工程よりも先に実施される。

(もっと読む)

半導体装置

【課題】2層の電極構造の絶縁膜の厚み分の段差に基づく固着不良を回避したディスクリート型バイポーラトランジスタを提供する。

【解決手段】1層目のエミッタ電極7の上下に設けられるエミッタコンタクトホールCH2とエミッタスルーホールTH2を非重畳とし、1つのエミッタ電極7についてエミッタコンタクトホールCH2とエミッタスルーホールTH2互いに離間して複数配置する。これにより、2層目のエミッタ電極17表面では、最大でも、膜厚が厚い絶縁膜に設けられたエミッタスルーホールTH2の段差の影響しか及ばず、2層目の電極表面の平坦性が向上する。これにより金属プレートの固着不良を回避できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、半導体基体との界面における組成の均一性に優れ、ショットキー接合層との十分に高い密着性が得られるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第一半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第二半導体領域6bと、第一半導体領域1aにオーミック接触するオーミック接合層7と、第二半導体領域6bにショットキー接触するショットキー接合層8とを備え、オーミック接合層7の二乗平均粗さが、20nm以下である半導体装置とする。

(もっと読む)

半導体装置

【課題】寄生抵抗が大きい場合においても、フィン構造を有する電界効果トランジスタのゲインを向上させる。

【解決手段】複数のフィンf11〜f19、f21〜f29が互いに並行に配置し、フィンf13〜f18、f23〜f28にそれぞれ跨るようにしてゲート電極G11、G12をフィンf13〜f18、f23〜f28の両側面にそれぞれ形成し、フィンf13〜f18、f23〜f28にそれぞれ跨るようにしてゲート電極G11、G12に並列されたゲート電極G13、G14をフィンf13〜f18、f23〜f28の両側面にそれぞれ形成し、フィンf13〜f18、f23〜f28に跨るようにしてゲート電極G13、G14に並列されたゲート電極G15をフィンf13〜f18、f23〜f28の両側面に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】サイズを縮小するとともに、オン抵抗を低くしながらオフ耐圧を高く保つことができる半導体装置と、その製造方法を提供する。

【解決手段】半導体基板1の領域には、ゲート電極4を挟んで一方にソース電極7およびLDD領域5bが形成され、他方にドレイン電極6およびLDD層5aが形成されている。半導体基板1の表面から所定の深さD1にわたり形成されたLDD層5aには、LDD層5aの表面を除いてLDD層5aに取り囲まれるとともに、LDD層5aの表面から深さD3にわたりp型拡散層10が形成されている。LDD層5aには、p型拡散層10の直下の領域においてLDD層5aの底からさらに深い領域に向かって突出するように深さD2にわたり突出部55が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、微細な寸法においてBottomゲートおよびUpperゲートを位置精度良く形成することが可能な半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明の一実施形態による半導体装置の製造方法は、Si5上にパッド酸化膜8とSiN膜9とを順に形成し、SiN膜9の表面からSOI基板のSiO22の所定の位置までエッチングすることによって溝を形成し、少なくとも溝の底面、側面を覆うように保護膜11を形成し、溝の底面上にBottomゲート電極3を形成し、Bottomゲート電極3に覆われない溝の側面に形成された保護膜11を除去し、その際にBottomゲート電極3上にのみダメージを残し、SOI基板のSi5からエピタキシャル成長させたSiを用いてBottomゲート電極3上にBottomゲート酸化膜4を形成することを特徴とする。

(もっと読む)

ヘテロ接合電界効果トランジスタ

【課題】ゲート電極破壊が起こらず、高電圧で安定して動作し、かつリーク電流を低減することができるヘテロ接合電界効果トランジスタを提供すること。

【解決手段】基板1の表面上にチャネル層2および障壁層3がこの順で積層された半導体層Sと、半導体層S上のトランジスタ領域11に形成されたトランジスタ部11Aおよびホール抜き領域12に形成されたホール抜き部12Aと、トランジスタ領域11とホール抜き領域12との間の半導体層Sの一部を選択除去して設けられた絶縁部10とを備え、ホール抜き部12Aにおけるホール抜き電極8と第2ドレイン電極9の間でアバランシェ降伏が生じるように、ホール抜き電極8と第2ドレイン電極9の間の耐圧が、トランジスタ部11Aのゲート電極と第1ドレイン電極との間の耐圧よりも小さく設定されたことを特徴とするヘテロ接合電界効果トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置

【課題】複数のワイヤーでボンディングを行う半導体装置において、ワイヤーボンディング不良を容易かつ確実に検出する。

【解決手段】半導体装置301は、半導体層2と、半導体層2に電気的に接続された複数のパッド17A、17Bと、複数のパッド17A、17Bのそれぞれに少なくとも1つずつ接続されたワイヤー50sとを備え、複数のパッド17A、17Bは、ワイヤー50sを介して、外部と接続される同一の端子40に接続されている。

(もっと読む)

横型IGBTとそれを用いたモータ制御装置

【課題】マルチエミッタ横型IGBTでは、中央部のゲートは外周部に比べてコレクタからの距離が遠く、ホールの到達率が小さく、オン電圧の低減が困難であった。

【解決手段】コレクタとエミッタ間の距離をLCE、少数キャリアの拡散係数をDとするとき、ライフタイムτの条件式を、 τ>LCE2/(5.29×D) とするとともに、コレクタ層の表面濃度を5×1017/cm3以下とした。

【効果】インバータICに必要なターンオフの高速性を損なうことなく、pコレクタから注入されたホールが全てのエミッタn+層からの電流経路に沿ってpチャネル層に到達できるようになり、IGBT内部で電流が均一に流れ、オン電圧を低減できる。

(もっと読む)

201 - 220 / 578

[ Back to top ]