Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

141 - 160 / 578

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法ならびにそれを用いたDC−DCコンバータ

【課題】内蔵ダイオードを有するトレンチMOSFETのしきい値電圧を向上させると共に、ドレインリーク電流の発生を低減させる。

【解決手段】内蔵ダイオードを有するトレンチMOSFETにおいて、コンタクトトレンチ23の下部におけるP−型チャネル領域4の厚さを200nm以下とし、バリアメタル9とP−型チャネル領域4をショットキー接合させてショットキーバリアダイオードを備えることにより、しきい値電圧を向上させ、ドレインリーク電流の発生を低減させることができる。

(もっと読む)

電界効果トランジスタ

【課題】 移動度にバラツキの少ない電界効果トランジスタを提供する。

【解決手段】 塗布プロセスにより形成される半導体層を持つ電界効果トランジスタにおいて、ソース電極及び/又はドレイン電極が、ゲート絶縁膜の凹部に配置されていることを特徴とする電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

電力用半導体装置

【課題】ラッチアップの発生を防止することができる電力用半導体装置を提供する。

【解決手段】半導体層は、第1導電型の第1の層8と、第2導電型の第2の層と、第3の層とを有する。第3の層は、第1導電型の第1の領域と、第2導電型の第2の領域とを有する。第2の電極11は、第1および第2の領域の各々と接触している。半導体層の第1の電極12に面する面と反対の面上にトレンチが形成されている。ゲート電極EVはゲート絶縁膜9を介してトレンチに埋め込まれている。ゲート電極EVは、第1の領域および第2の層を貫通して第1の層8に侵入する第1の部分1と、第2の領域および第2の層を貫通して第1の層8に侵入する第2の部分13とを含む。第1の部分1が第1の層8に侵入する深さに比して、第2の部分13が第1の層8に深く侵入している。

(もっと読む)

半導体素子およびその製造方法

【課題】温度変化による半導体基板および金属層の熱膨張係数の差に起因して半導体基板にクラックが生じることを防止する。

【解決手段】半導体基板11上に、P型拡散層12の外周縁とN型半導体との境界を覆うように絶縁体被膜20をリング状に形成し、絶縁体被膜20の内側の半導体基板11表面に接触金属層15を積層し、接触金属層15および絶縁体被膜20の表面を覆うようにクッション用電極層16および引き出し電極層17を形成する。絶縁体被膜20は二酸化珪素被膜13と二酸化珪素被膜13よりもエッチングレートの小さい窒化被膜14とからなり、二酸化珪素被膜13に、窒化被膜14の内周から内側に張り出すように張り出し部13aが形成されている。引き出し電極層17(例えばNi)はクッション用電極層16(例えばAl)よりも表面処理液に対するエッチングレートが小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

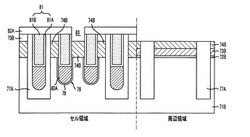

半導体装置の製造方法および半導体装置

【課題】ゲート−ドレイン間寄生容量を低減できる半導体装置の面積を低減し、工程数を削減する。

【解決手段】トランジスタ領域では、ソース配線層とゲート電極がトレンチ内に埋め込まれている。ソース引き出し領域は、トランジスタ領域の隣またはトランジスタ領域内に設けられ、ソース配線層がトレンチの上端よりも上に突出するように形成される。このソース配線層は、トレンチの直上で、トランジスタ領域に形成されたソース電極と接続される。ゲート引き出し領域は、ソース引き出し領域の外側に設けられ、ゲート電極とゲート配線層とが接続される。ゲート電極は、ポリシリコン膜を成膜した後、レジストパターンを形成することなくエッチバックすることにより形成される。このとき、ソース配線層のトレンチの上端よりも上に突出した部分の側壁には、ポリシリコン膜がサイドウォール状に残る。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETを備えた半導体装置の特性を向上させる。

【解決手段】FINFETは、シリコン基板1上にアーチ形状に配置された単結晶シリコンからなるチャネル層3と、チャネル層3の外側の一部において、フロントゲート絶縁膜IG1を介して形成されたフロントゲート電極EG1と、バックゲート絶縁膜IG2を介して、チャネル層の内側を埋め込むようにして形成されたバックゲート電極EG2とを有する。アーチ形状の内部に配置されているバックゲート電極EG2は、フロントゲートEG1をくぐるようにして配置されている。

(もっと読む)

半導体装置

【課題】ソース電極の接続に際し、余分な引き回しが無く、構造が簡単であり、接地インダクタンスを有効に低減化可能なマイクロ波/ミリ波/サブミリ波帯の半導体装置を提供する。

【解決手段】基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域AA上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、それぞれゲート電極24およびドレイン電極22に接続され、ゲート電極24、ソース電極20およびドレイン電極22が延伸する方向の窒化物系化合物半導体層12上に配置されたゲート端子電極GL1、GL2およびドレイン端子電極DL1、DL2と、ゲート電極24,ソース電極20およびドレイン電極22が延伸する他方の方向の基板10の端面に配置され、ソース電極20と接続された端面電極SCとを備える。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】生産性に優れたフレキシブル半導体装置を提供する。

【解決手段】可撓性を有するフレキシブル半導体装置100であり、樹脂フィルム30と、樹脂フィルム30の上に形成された金属層10とを備え、金属層10は、絶縁壁51によって分断され、且つ、絶縁壁51の一端53は樹脂フィルム30に接しており、絶縁壁51によって金属層10から、ゲート電極10g、ソース電極10sおよびドレイン電極10dが形成されている。ゲート電極10gの上には、絶縁壁51に接するゲート絶縁膜22が形成されており、ゲート絶縁膜22の上には半導体層20が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アニール時の酸化剤の拡散によるゲート電極の酸化を抑制する。

【解決手段】半導体基板の活性領域にゲートトレンチを形成する工程と、前記半導体基板の活性領域上及びゲートトレンチ内にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の前記ゲートトレンチの開口縁近傍における窒素濃度が、前記ゲートトレンチの底部近傍における窒素濃度よりも高濃度となるように、プラズマ窒化処理によって前記ゲート絶縁膜に窒素を導入する窒化工程と、前記ゲートトレンチを埋めて前記ゲート絶縁膜を覆うようにゲート電極層を積層してから、前記ゲート電極層をエッチングによりパターニングしてゲート電極を形成するゲート電極形成工程と、前記ゲート電極層のエッチングによって露出した前記活性領域をアニールするアニール工程と、を具備してなることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置

【課題】高アバランシェ耐量且つ低オン抵抗の半導体装置を提供する。

【解決手段】第1導電型の半導体層21、22と、半導体層22の第1の主面側に設けられた第2導電型のベース層23と、ベース層23上に設けられた第1導電型のソース層24と、ソース層24の表面上に設けられた第1の主電極11と、半導体層21の第2の主面に設けられた第2の主電極12と、セル領域で半導体層22に達して設けられたトレンチゲートと、終端領域におけるベース層23中に設けられると共に表面の一部が第1の主電極11と接し、ベース層23よりも第2導電型不純物濃度が高い終端キャリア排出層25bと、セル領域におけるソース層24の下のベース層23中に設けられ、端部が終端領域で終端キャリア排出層25bに接続され、ベース層23よりも第2導電型不純物濃度が高いセルキャリア排出層25aとを備えている。

(もっと読む)

半導体装置

【課題】オン状態にすることが容易な半導体装置を提供する。

【解決手段】半導体チップ10にN型ドリフト層1、P型ベース層2、N型エミッタ層3、N型バッファ層4、P型コレクタ層6、N型コンタクト層7が形成され、半導体チップ10上にP型ベース層2及びN型エミッタ層3に接続されたエミッタ電極11が設けられ、半導体チップ10内にN型エミッタ層3及びP型ベース層2を貫きN型ドリフト層1内に進入したトレンチゲート電極14が埋設され、半導体チップ10とトレンチゲート電極14との間にゲート絶縁膜13が形成され、半導体チップ10の下面上にP型コレクタ層6及びN型コンタクト層7に接続されたコレクタ電極15が設けられたアノードショート型の半導体装置101において、N型バッファ層1とP型コレクタ層6及びN型コンタクト層7との間に、抵抗率がN型バッファ層4の抵抗率よりも高いN型高抵抗層5を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】 特性バラツキを低減させるとともに、半導体装置の歩留まりを向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 主面がオフ角θを有するn+型SiC基板1上に、n-型SiC層2、p+型SiC層3が順次形成され、素子周辺にガードリング6が形成されると共に、p+型SiC層3上に、複数のオーミック電極4aが設けられている。このオーミック電極4aの中から所望のオーミック電極を選択し、PINダイオードの一方の電極とする。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

ショットキーデバイス

本発明に係るデバイスは、半導体ナノワイヤ(1)と金属接触(5)との間の半導体金属接合によって形成されたショットキー障壁を備える。前記金属接触(5)は、その長さに沿って各ナノワイヤ(1)の周辺領域を少なくとも部分的に囲む。前記ナノワイヤ(2)は、前記半導体金属接合の一部である低濃度ドープ領域を備える。この低濃度ドープ領域は、ナノワイヤセグメント、ナノワイヤの全体又は高濃度ドープナノワイヤコア(3)を備えたコアシェル構造によって形成され、前記低濃度ドープ領域は、シェル(4)に含まれる。前記デバイスは、本発明に係る方法を用いて製造され、かかる方法は、2つの異なる成長モードを使用し、第1のステップは、前記半導体金属接合の形成用の適切なテンプレートを与えながら基板(2)から軸方向に成長させることを備え、第2のステップは、前記低濃度ドープ領域においてドーピングレベルを制御可能に放射状に成長させることを備える。 (もっと読む)

141 - 160 / 578

[ Back to top ]