Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

61 - 80 / 578

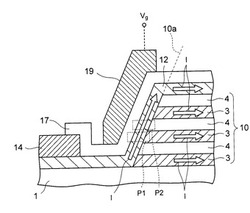

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキーバリアダイオードの逆リーク電流を低減させる。

【解決手段】禁制帯幅の異なるGaN膜3a、3bとバリア膜4a、4bとを交互に積層して形成したヘテロ接合体5a、5bを有する積層体6と、積層体6の一方の側壁にショットキー接続された第1電極8と、もう一方の側壁に接して形成された第2電極10とを有する半導体装置において、第1電極8とバリア膜4a、4bとの間に酸化膜12を設ける。これにより、バリア膜4a、4bの加工に起因してバリア膜4a、4bに残留する欠陥にを介して逆リーク電流が流れることを防ぐ。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】イオン注入を用いることなく2次元正孔ガスの所期の濃度分布を容易且つ確実に得て、電界集中のなだらかな緩和を実現する高信頼性の窒化物半導体装置を得る。

【解決手段】n−GaN基板1のN面上に形成されたn−GaN層2と、n−GaN層上に形成されたAlGaNからなるJTE構造10と、n−GaN層2上に形成されたアノード電極4とを有しており、n−GaN層2のJTE構造10との界面に、アノード電極4から離間するほど正孔濃度が低くなるように、2次元正孔ガスが生成される。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の寄生容量成分を好適に調整する。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】基板の反りとドレイン抵抗を低減させながら、半導体装置側面のバリや半導体装置の損傷を抑制することを目的とする。

【解決手段】半導体基板1裏面の表面電極であるソース電極2、ドレイン電極3の裏面に相当する領域に窪み部6を設け、ダイシング領域以外の窪み部6や窪み部6間に金属層5を形成することにより、基板の反りとドレイン抵抗を低減させながら、半導体装置側面のバリや半導体装置の損傷を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い信頼性を有する、半導体装置およびその製造方法を提供すること。

【解決手段】n型半導体基板の一方の主面に、p型ベース領域とn型エミッタ領域と所要の位置にゲート絶縁膜を介して載置されるゲート電極とからなるMOSゲート構造と該MOSゲート構造を沿面方向に取り巻く耐圧構造部とを有し、他方の主面に1μm以下の浅い逆阻止接合を有するp型コレクタ層を備える半導体装置において、前記コレクタ層の他方の主面上に、バッファ絶縁層を介して被覆されるコレクタ電極が、前記バッファ絶縁層に設けられたコンタクトホールを通して前記コレクタ層と導電接触する半導体装置とする。

(もっと読む)

電力用半導体装置

【課題】オン電圧および損失の低減を可能にする電力用半導体装置を提供する。

【解決手段】pベース層2の表面からn−層1の第1の主面に対して垂直方向で、n−層1内に達する位置まで形成され、その後n−層1の第1の主面に対して水平方向で、片側に所定の長さ延出した底部3dを有したL字形のトレンチゲート21を備え、さらに所定の隣合うL字形のトレンチゲート21の底部21dの延出方向が対向するようにして、それぞれの底部21dの間隔が、n−層1の第1の主面に対して垂直方向に形成されている部分の間隔より狭くなるようにしたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

窒化物半導体装置

【課題】高周波数動作が可能で、ゲートリーク電流や電流コラプスを抑制できる窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極上に絶縁膜9を介してゲート電極7を配置する。さらに、ソース電極とドレイン電極との間の電子供給層表面を珪素膜11で被覆する。

(もっと読む)

61 - 80 / 578

[ Back to top ]