Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

41 - 60 / 578

半導体装置

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置を提供することを目的

の一とする。

【解決手段】13族元素および酸素を含む第1の絶縁膜と、第1の絶縁膜と一部が接する

酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と

、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜とゲート電極の間の、酸化物

半導体膜と一部が接する第2の絶縁膜と、を有する半導体装置である。また、13族元素

および酸素を含む第1の絶縁膜には、化学量論的組成比より酸素が多い領域が含まれる構

成とする。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および順方向電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有し、表面12側に側壁22および底壁20を有する台形トレンチ17が形成されたSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。また、各台形トレンチ17の底壁20のエッジ部24を、曲率半径Rが0.01L<R<10L・・・(1)(式(1)において、Lはトレンチ17の幅方向に沿って対向するエッジ部24間の直線距離を示している。)を満たすように、台形トレンチ17の外方へ向かって湾曲する形状に形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

窒化物半導体発光素子およびその製造方法

【課題】窒化物半導体発光素子の電流拡散効率を向上させるとともに、コンタクト抵抗をも低減でき、大きな駆動電流密度においても発光均一性と高い光出力を得ながら、動作電圧を低減させる得る窒化物半導体発光素子およびその製造方法を提供する。

【解決手段】基板の同一面側にn側およびp側電極パッドが形成された窒化物半導体発光素子であって、p側電極パッド(およびn側電極パッド)から枝状に延伸された延長部を形成し、それによって発光素子中の電流分布を改善する電極構造の窒化物半導体発光素子において、n側およびp側のシート抵抗がいずれも充分に低い場合に、p型窒化物半導体層上に形成された透光性導電膜からなる電流拡散層のシート抵抗を一定条件下において高くすることにより、p型窒化物半導体層と電流拡散層とのコンタクト抵抗を低減し、且つ、シート抵抗の面内分布がより均一になり、光出力も向上する。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置及びその製造方法

【課題】低いオン抵抗を維持したまま、耐圧の向上を図ることができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、制御電極、第1主電極、内部電極、絶縁領域、を備える。制御電極は、トレンチの内側に設けられる。第1主電極は、第3半導体領域と導通し、トレンチの外側に設けられる。内部電極は、トレンチ内に設けられ、第1主電極と導通する。絶縁領域は、トレンチの内壁と第1主電極とのあいだ、及びトレンチの内壁と内部電極とのあいだ、に設けられる。内部電極は、制御電極よりもトレンチの底面側の第1領域に含まれる第1内部電極部と、第1領域と、第1主電極と、のあいだの第2領域に含まれる第2内部電極部と、を有する。第1内部電極部とトレンチの内壁との間隔は、第2内部電極部とトレンチの内壁との間隔よりも広い。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

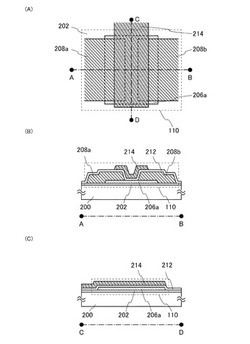

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン抵抗が小さく、またオフ容量が低い、デュアルゲートを備えた電界効果トランジスタを提供する。

【解決手段】第1又は第2のゲート電極8は、ソース電極4側又は前記ドレイン電極5側に延びる第1のひさし部61と、第2又は第1のゲート電極8側に延びる第2のひさし部62とを有し、第2のひさし部62の長さが第1のひさし部61の長さより短い。

(もっと読む)

41 - 60 / 578

[ Back to top ]