Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

561 - 578 / 578

薄膜トランジスタおよび表示装置

【課題】パターンの解像度よりもチャネル長を短くすることが容易で、これにより低コストで取り扱い電流量を増加させることが可能な薄膜トランジスタを提供する。

【解決手段】基板3上に、ゲート電極5、これを覆うゲート絶縁膜7、このゲート絶縁膜7を介してゲート電極5を覆うチャネル層(チャネル部半導体薄膜)11がこの順またはこれと逆の順に積層され、チャネル層11の表面側と裏面側とに、ソース電極9とドレイン電極15とが分け置かれていることを特徴としている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 小型化及び低コスト化できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】 N型半導体基板12下面に形成され、該N型半導体基板12よりも高抵抗なN型エピタキシャル層14下面の一部分にP型拡散層22,22を設け、該P型拡散層22,22及びその周辺のN型エピタキシャル層14下面に第1電極層20を有する半導体装置10において、前記N型エピタキシャル層14下面の前記第1電極層20が形成されていない部分の凹部の底に、N型半導体基板12に接続された第2電極層21を有する構成にする。

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

半導体素子の製造方法

【課題】 簡単な方法によりゲート電極を斜めに傾け、ゲート長を短縮することができる半導体素子の製造方法を得る。

【解決手段】 まず、半導体基板11上にゲート電極15を形成する。次に、半導体基板上にゲート電極の一方の側面のみに接触するようにレジスト16を形成する。そして、レジストを収縮又は膨張させることによりゲート電極を傾ける。ここで、ゲート電極の断面形状をΓ型、T型又はY型とするのが好ましい。また、ゲート電極をソース側へ傾けるのが好ましい。

(もっと読む)

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

フィールドプレートに接続されたソース領域を有する、ワイドバンドギャップ電界効果トランジスタ

本発明に係る電界効果トランジスタは、基板(12)上に連続的に形成されるバッファ及びチャネル層(16)を備える。ソース電極(18)、ドレイン電極(20)、並びに、ソース及びドレイン電極間にあるゲート(22)はすべて、チャネル層に電気的に接続して形成される。スペーサ層(26)は、前記ゲートと前記ドレイン電極との間にあるチャネル層の表面の少なくとも一部の上に形成され、フィールドプレート(30)は、前記ゲート及びチャネル層から絶縁されるスペーサ層上に形成される。フィールドプレート(30)は、少なくとも1つの導電性パスによってソース電極に電気的に接続され、金属半導体電界効果トランジスタ内におけるピーク操作電界を低減する。  (もっと読む)

(もっと読む)

自己整列型炭化ケイ素半導体デバイスおよびそのデバイスの作成方法

電流安定性の改善された自己整列型炭化ケイ素パワーMESFETおよびそのデバイスの作成方法を記載する。このデバイスは、ゲート凹部により分離されたレイズドソースおよびドレイン領域を含み、低ゲートバイアスにおいてでさえ表面トラップ効果が低減されるため、電流安定性が改善される。このデバイスは自己整列型プロセスを用いて作成され得る。このプロセスでは、金属エッチマスクを用いて、nドープのSiCチャネル層上のn+ドープのSiC層を備えた基板がエッチングされてレイズドソースおよびドレイン領域が規定される。この金属エッチマスクがアニールされ、ソースおよびドレイン・オームコンタクトが形成される。単層または多層の誘電性フィルムが成長または堆積され異方性エッチングされる。蒸着または別の異方性堆積技術を用いて、ショットキーコンタクト層および最終金属層が堆積され、オプションとして、誘電性層の等方エッチングされる。  (もっと読む)

(もっと読む)

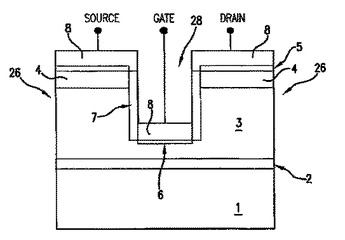

トレンチデバイスのための自動整合された接点構造体

【課題】オン時の電流を下げることなく、セルの実装密度を高める。

【解決手段】 トレンチタイプのパワー半導体デバイスを製造する方法であって、開口部を有するマスク層を半導体の表面に形成するステップを含んでいる。マスクの開口部を通し、半導体本体内に、ゲートを有するトレンチを形成する。次に、ゲートの頂部であって、かつマスク層の開口部内に絶縁プラグを形成する。次に、マスク層を除去し、半導体表面の上方に延びる絶縁プラグを残す。次に、トレンチ間にソース打ち込み領域を形成する。その後、絶縁プラグの側面に沿って、スペーサーを形成し、トレンチに隣接するソース打ち込み領域の部分をカバーする。次に、このスペーサーをマスクとして使用することにより、ソース打ち込み領域の露出部分をエッチングし、除去する。次に、スペーサーの下の残りのソース打ち込み領域を駆動し、ソース領域を形成する。その後、エッチングされた領域内に、浅い高導電タイプの接点領域を形成し、次に、デバイスの上にソースおよびドレイン接点を形成する。

(もっと読む)

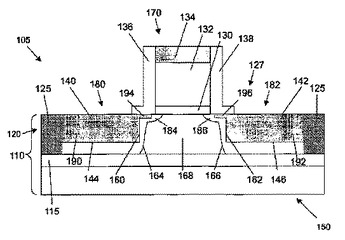

半導体装置及び半導体装置の製造方法

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

PN接合ダイオード装置及びその製造方法

【課題】より小型が可能なPN接合ダイオード装置及びその製造方法を提供することにある。

【解決手段】PN接合ダイオードのカソード電極22及びアノード電極23を共に、シリコン基板10の一方の主面に形成することにより、カソード電極22及びアノード電極23とをリードフレーム26に、ワイヤー等で接続することなく、接着することを可能にする。

(もっと読む)

フリップチップFET素子

【課題】電力素子のオン状態抵抗、放熱特性、インダクタンスを改善する。

【解決手段】半導体素子は導電パッド領域26,36を含み、各々の導電パッド領域は複数の金属トレースに電気的に接続される。複数の金属トレースは各々が順番に拡散に接続される。はんだバンプやビアなどの導電接点素子は各々の導電パッド領域に取り付けられ、導体素子が第1のピッチを有する反復パターンに配列され得る。半導体素子は平行移動トレース50,60も含み、各々の平行移動トレースは2つ以上の導電接点素子に電気的に接続され得る。各々の平行移動トレースはそこに取り付けられる相互接続素子を有し得る。相互接続素子は第1のピッチより実質的に大きい第2のピッチを有する反復パターンに配列され得る。

(もっと読む)

半導体装置

【課題】低オン抵抗の縦型トランジスタが形成されてなる半導体装置を提供する。また、マルチチャネル化の自由度の高い半導体装置を提供する。

【解決手段】半導体基板30の一方の表面である主面側に形成された第1電極と、もう一方の表面である裏面側に形成された第2電極とを有する縦型トランジスタ101が形成されてなる半導体装置100であって、第1電極が、主面上に形成された層間絶縁膜43を介して、主面側の半導体基板30表層部に形成された拡散領域41,42,48に接続する第1金属層44からなり、裏面側には、半導体基板30の内部に向かってトレンチ35が形成され、第2電極が、トレンチ内に形成され、トレンチ35によって露出された半導体基板30内の半導体層33に接続する第2金属層37からなる半導体装置100とする。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

561 - 578 / 578

[ Back to top ]