Fターム[4M104FF03]の内容

Fターム[4M104FF03]に分類される特許

1 - 20 / 102

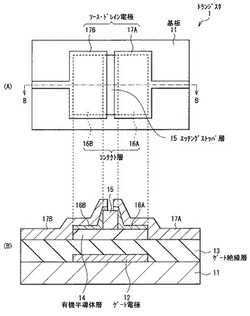

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

ショットキーバリアダイオード

【課題】逆方向耐圧を大きくしても順方向電圧の増大、オーミック電極層とのコンタクト抵抗の増大を抑制することが可能なショットキーバリアダイオードを提供する。

【解決手段】ショットキーバリアダイオード1は、n型の導電性を有するGa2O3系化合物半導体からなるn型半導体層3と、n型半導体層3に対しショットキー接触するショットキー電極層2とを備え、n型半導体層3には、ショットキー電極層2にショットキー接触する電子キャリア濃度が比較的低いn−半導体層31と、n−半導体層31よりも高い電子キャリア濃度を有するn+半導体層32とが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

窒化物系発光素子及びその製造方法

【課題】窒化物系発光素子及びその製造方法を提供する。

【解決手段】窒素物系発光素子は、基板110、n型クラッド層130、活性層140、

p型クラッド層150、格子セル層160及びオーミック接触層が順次に積層された構造

よりなっている。また格子セル層160は導電性を有する素材で30μm以下の大きさを

有する粒子型セルがオーミック接触層内に埋め込まれて、相互離隔されて形成されている

発光素子である。このような窒素物系発光素子とその製造方法は、p型クラッド層とのオ

ーミック接触特性が改善されているため発光効率及び素子寿命を向上させ、かつウェーハ

成長後の活性化工程を省略できて、製造工程を単純化させうる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

半導体発光装置及びその製造方法

【課題】高いオーミック性と反射率を併せ有する電極構造を備える、低駆動電圧で駆動し、良好な光取り出し効率を有する半導体発光装置及びその製造方法を提供すること。

【解決手段】n型半導体層と、p型半導体層と、前記n型半導体層と前記p型半導体層との間に設けられた活性層と、前記n型半導体層に接して設けられたn電極と、前記p型半導体層に接して設けられたp電極とを具備する半導体発光素子。前記p電極が前記p型半導体層上に少なくとも一部が網目状に形成されたNiO層と、このNiO層に接して形成されたAg層とを含む。

(もっと読む)

半導体装置

【課題】リーク電流の少ないダイオードを提供する。

【解決手段】実施形態の半導体装置は、AlXGa1−XN(0<x<1)またはInyAl1−yN(0≦y≦1)からなる第1の半導体層2と、第1の半導体層の同一面上に、ノンドープ、n型又はp型のGaNからなる第1の電子誘起領域1、絶縁膜5とアノード電極7と、第1の電子誘起領域上にカソード電極を備え、第1の電子誘起領域、絶縁膜とアノード電極は第1の半導体層と接合し、絶縁膜は第1の半導体領域とアノード電極の間で、第1の半導体層と接合し、アノード電極と第1の半導体層との接合はオーミック接合であり、カソード電極と第1の電子誘起領域との接合はオーミック接合であることを特徴とする。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、ワイドバンドギャップ材料を用いて電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれの、少なくとも第1半導体層と接合する部分が、所定の半導体材料を用いて正孔を多数キャリアとするように構成されてなる第2半導体層であり、第1半導体層と第2半導体層との接合部においてはP−N接合が形成されてなる、ようにした。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれと第1半導体層との接合部がそれぞれ第1と第2の接合部からなり、第1接合部は、第1半導体層と接続する単位アノード部部分が正孔が多数キャリアの第2半導体層であるP−N接合部であり、第2接合部は、第1半導体層と接続する単位アノード部部分が金属によって構成されたショットキー接合部である、ようにした。

(もっと読む)

半導体装置

【課題】大電力用途の半導体装置に用いるトランジスタには、高いドレイン電流を確保するためのチャネル領域を有する構造が必要である。その一例のトランジスタとして、縦型(トレンチ型)トランジスタも検討されているが、ドレイン電流のオンオフ比がとれず、良好なトランジスタ特性が得られないという課題がある。

【解決手段】導電性を有する基板上において、側面がテーパー形状の断面を有する複数の島状の領域が表面にドット状に設けられた酸化物半導体層を、基板と酸化物半導体層の間に設けられた第1の電極と酸化物半導体層上に設けられた第2の電極とで挟持し、絶縁層を介した酸化物半導体層の島状の領域の側面上に、ゲート電極としての機能を有する導電層を設ける。

(もっと読む)

半導体発光素子

【課題】メタル電極に設けられた延伸部の表面を覆う絶縁膜の剥離が抑制された半導体素子を提供する。

【解決手段】半導体からなる活性層に積層されたn型またはp型の半導体層と、該半導体層の上に配置され接続部および延伸部を有するメタル電極と、該メタル電極の該延伸部の上面および側面を少なくとも覆う絶縁膜と、を備え、該延伸部はメタル多層膜で形成され、該メタル多層膜は少なくとも2層の第1メタル層と、該第1メタル層と交互に積層された第2メタル層とを含み、かつ、その最上層は該第2メタル層のひとつであり、該メタル多層膜に含まれる該最上層の第2メタル層以外の第2メタル層の各々の端面が該延伸部の側面に露出して該絶縁膜と接しており、該第2メタル層を構成する第2メタル材料は該第1メタル層を構成する第1メタル材料よりも導電率は低いが該第1メタル材料よりも該絶縁膜との密着強度に優れている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

ショットキーダイオードおよびPNダイオード

【課題】耐量の大きいダイオードを提供する。

【解決手段】ショットキーダイオードであって、窒化物半導体で形成された半導体層と、半導体層上に形成され、半導体層にショットキー接続されたショットキー電極と、を備え、ショットキーダイオードに逆バイアスがかかったときに、ショットキー電極の端部の下方の半導体層において空乏化する領域は、ショットキー電極の他の一部の下方の半導体層において空乏化する領域より長いショットキーダイオードを提供する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

窒化ガリウム半導体素子

【課題】高出力の窒化ガリウムショットキー・ダイオード素子を提供する。

【解決手段】1〜6μmの厚さを有するn+型ドープしたGaNダイオードから製造した窒化ガリウムベースの半導体ショットキー・ダイオードをサファイア基板の上に配設する。1μmを超える厚さを有するn−型ドープしたGaNダイオードを、複数の細長形の指にパターン化した前記n+型ドープGaNダイオード上に配設し、金属層をn−型ドープGaN層上に配設し、それとの間にショットキー接合を形成する。細長形の指の層厚、長さおよび幅は、降伏電圧が500Vを超え、電流容量が1アンペアを超え、かつ順方向電圧が3V未満である素子を得るように最適化される。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

1 - 20 / 102

[ Back to top ]