Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

101 - 120 / 578

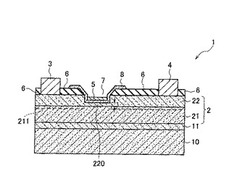

化合物半導体装置

【課題】閾値電圧の高い良好なノーマリオフ特性を有する化合物半導体装置を提供する。

【解決手段】キャリア走行層21とキャリア供給層22を有し、二次元キャリアガス層211が形成される化合物半導体層2と、化合物半導体層2上に互いに離間して配置され、二次元キャリアガス層211とオーミック接続する第1の主電極3及び第2の主電極4と、第1の主電極3と第2の主電極4間で、化合物半導体層2上に配置された金属酸化物半導体膜8と、金属酸化物半導体膜8上に配置された、金属酸化物半導体膜8に接するチタン膜又はチタンを含む化合物膜を有する制御電極5とを備える。

(もっと読む)

トランジスタおよびその製造方法

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタおよびその製造方法を提供する。

【解決手段】本発明の一態様に係るトランジスタ100は、導体領域10aと表面に原子が結合した半導体領域10bとを有し、チャネルとして機能するグラフェン膜10と、グラフェン膜10上にゲート絶縁膜11を介して形成されたゲート電極12と、を有し、導体領域10aと半導体領域10bが形成するショットキー接合のトンネル電流をスイッチング動作に用いる。

(もっと読む)

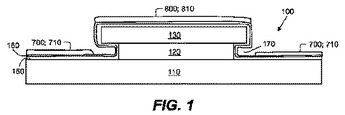

半導体装置及び半導体装置の動作方法

【課題】トランジスタの閾値電圧を高くする。

【解決手段】フローティング電極110は半導体層102上に形成されており、絶縁層はフローティング電極110上に形成されている。バイアス電極134は、絶縁層を介してフローティング電極110の一部に対向することにより、フローティング電極110と容量結合し、かつフローティング電極110が半導体層102にチャネル領域を形成しない大きさの電圧が印加される。制御電極132は、絶縁層を介してフローティング電極110の他の部分に対向することにより、フローティング電極110と容量結合し、かつトランジスタのオン/オフを制御するための制御電圧が入力される。

(もっと読む)

電界効果トランジスタおよび半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

Pチャネル型パワーMOSFET

【課題】PチャネルパワーMOSFETにおいて、同手法に従い、トレンチ内にP+ポリシリコンゲート電極とP+フィールドプレート電極を有するトレンチ内ダブルゲート型PチャネルパワーMOSFETを製作して、種々の特性を測定したところ、高温状態で、基板に対してゲートに負のバイアスを印加し続けると、PチャネルパワーMOSFETの閾値電圧の絶対値がストレス印加時間と共に次第に大きくなってゆく現象があることが明らかとなった。

【解決手段】本願の一つの発明は、N型ポリシリコン線状フィールドプレート電極およびN型ポリシリコン線状ゲート電極を各トレンチ部に有するPチャネル型パワーMOSFETである。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】ドリフト領域、ベース領域およびソース・エミッタ領域からなる寄生素子による影響をなくすことができ、また、オン電圧が増大することを防止することができる半導体素子の製造方法を提供すること。

【解決手段】半導体基板のおもて面に、ベース領域を貫通し、ドリフト領域1まで達するトレンチ3を形成する。ついで、ゲート絶縁膜4を介して、トレンチ3の内部に、ベース領域2の表面と同じ高さにまで達しないようにゲート電極5を埋め込み、第2凹部を形成する。ついで、第2凹部の内部に埋め込むように層間絶縁膜7を形成する。ついで、エッチバックを行い、ゲート電極5の表面にのみ層間絶縁膜7を残す。そして、エッチングによって、ベース領域2の表面がゲート電極5と層間絶縁膜7との界面より低い位置になるまで、ベース領域2の表面層を除去し、第1凹部6を形成する。ついで、第1凹部6の内部にソース電極8を埋め込む。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

多層拡張ドレイン構造を有する高電圧トランジスタを作製する方法

【課題】拡張ドレイン領域を有する高電圧トランジスタを作製する方法を提供する。

【解決手段】拡張ドレイン領域を有する高電圧トランジスタを作製する方法を提供は、第一の導電型である基板上に第一の導電型であるエピタキシャル層を形成し、そして、エピタキシャル層をエッチングして、エピタキシャル層の第一及び第二の側壁部を形成する一対の離間した溝部を形成することを含む。各溝部の一部には、第一及び第二の側壁部をカバーするように、誘電体層が充填される。

そして、溝部の残りの部分に導電材料が充填されて、基板及びエピタキシャル層から絶縁された第一及び第二のフィールドプレート部材が形成される。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた高耐圧半導体整流装置を提供する。

【解決手段】第1導電型のワイドバンドギャップ半導体基板と、ワイドバンドギャップ半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが20μm以上の第1導電型のワイドバンドギャップ半導体層と、ワイドバンドギャップ半導体層表面に形成される第1導電型の第1のワイドバンドギャップ半導体領域と、第1のワイドバンドギャップ半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域と、第1および第2のワイドバンドギャップ半導体領域上に形成される第1の電極と、ワイドバンドギャップ半導体基板の下面に形成される第2の電極と、を備え、第2のワイドバンドギャップ半導体領域の幅が15μm以上であることを特徴とする半導体整流装置。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

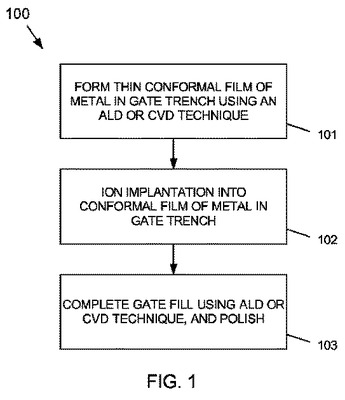

イオン注入を用いた圧縮金属ゲート応力の導入によるトライゲートMOSFETの駆動電流の増大化

半導体デバイスは、フィン及び金属ゲート膜を有する。フィンは半導体材料の表面に形成されている。金属ゲート膜は、フィン上に形成され、且つ金属ゲート内に圧縮応力を形成するために当該金属ゲート膜内に注入されたイオンを有する。典型的な一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<100>方向に沿っている。典型的な他の一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<110>方向に沿っている。フィンは、金属ゲート膜内の圧縮応力によって生成される面外圧縮を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

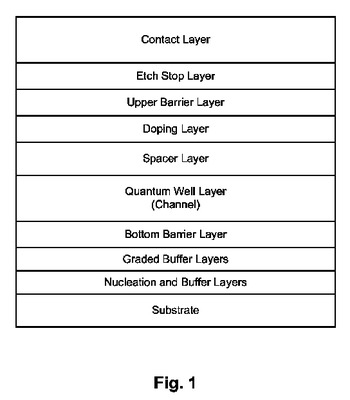

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

メモリ素子及びその動作方法

【課題】メモリ素子及びその動作方法を提供する。

【解決手段】メモリセルを含み、該メモリセルは、バイポーラメモリ要素及び双方向スイッチング要素を含み、該双方向スイッチング要素は、該バイポーラ・メモリ要素の両端に連結され、該双方向スイッチング要素は、第1スイッチング要素及び第2スイッチング要素を含み、該第1スイッチング要素は、該バイポーラ・メモリ要素の一端に連結され、第1スイッチング方向を有することができ、該第2スイッチング要素は、該バイポーラ・メモリ要素の他端に連結され、第2スイッチング方向を有することができ、該第2スイッチング方向は、該第1スイッチング方向に反対方向でありうる。

(もっと読む)

101 - 120 / 578

[ Back to top ]