Fターム[4M104FF01]の内容

Fターム[4M104FF01]の下位に属するFターム

背面配置 (461)

段状配置(メサ型配置) (102)

側面配置 (267)

Fターム[4M104FF01]に分類される特許

121 - 140 / 578

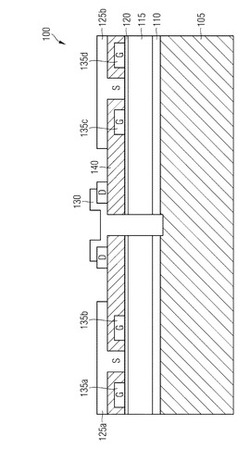

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

窒化物系化合物半導体装置、及びその製造方法

【課題】オーミック電極のオーミックコンタクト抵抗を確実に低減させる。

【解決手段】各オーミック電極3、4は、GaNキャップ層26表面のリセス28周辺部位に接触する第1電極51と、第1電極51に接触して、リセス28を介して2次元電子ガス層27に及ぶ第2電極52とを有している。第1電極51は、リセス28の開口部を囲む環状のものである。第2電極52は、第1電極51に重なる頭部52a、及びリセス28内に形成された柱状部52bからなる。第1及び第2電極51、52を第1及び第2温度でそれぞれ熱処理しているので、第1及び第2電極51、52のオーミックコンタクト抵抗を共に低減させ、各オーミック電極3、4そのもののオーミックコンタクト抵抗を低減させることができる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】表示品質と開口率を向上することができる液晶表示装置及びその製造方法を得る。

【解決手段】基板上に位置し、相互に交差して画素領域を定義するゲート配線204及びデータ配線と、ゲート配線に接続されるゲート電極202と、ゲート電極上に位置するゲート絶縁膜と、ゲート絶縁膜上に位置するアクティブ層220と、アクティブ層上に位置し、相互に離間されたソース電極234及びドレイン電極236と、アクティブ層及びソース電極間、並びにアクティブ層及びドレイン電極間に位置するオーミックコンタクト層と、アクティブ層上に位置し、ソース電極及びドレイン電極の内側に向かう二つの側面を有し、二つの側面のうち、少なくとも一つは、ソース電極及びドレイン電極の内側間に位置するシールドパターン222と、画素領域に位置し、ドレイン電極に接続される画素電極とを設けた。

(もっと読む)

半導体装置

【課題】三次元半導体であるsurrounding gate transistor(SGT)のオン電流を増加させることにより、SGTの高速動作を実現する半導体装置を提供することを課題とする。

【解決手段】ソース、ドレイン及びゲートが、基板上に階層的に配置される半導体素子であって、シリコン柱と、前記シリコン柱の側面を取り囲む絶縁体と、前記絶縁体を囲むゲートと、前記シリコン柱の上部又は下部に配置されるソース領域と、前記シリコン柱の上部又は下部に配置されるドレイン領域であって、前記シリコン柱に対して前記ソース領域と反対側に配置されるドレイン領域とを備え、前記シリコン柱と前記ソース領域との接触面は、前記シリコン柱と前記ドレイン領域との接触面より小さい半導体素子を提供することにより上記課題を解決する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

トレンチ金属酸化物半導体電界効果トランジスタの製造方法

【課題】多孔質のトレンチ金属酸化物半導体電界効果トランジスタ(MOSFET)を提供する。

【解決手段】多孔質のMOSFETの製造方法は、トレンチ領域をパターニングするために第1のエピタキシャル(エピ)層の上に第1のフォトレジストを堆積する段階と、メサ領域をパターニングするために第1のゲート導体層の上に第2のフォトレジストを堆積する段階と、ハンプを有する第2のゲート導体層を形成するために前記メサ領域の前記第1のゲート導体層の部分をエッチング除去する段階と、Tiゲート導体層を形成するために前記第2のゲート導体層を結晶的にチタン化する段階と、を含む。メサ領域の端部は、トレンチ領域の端部に位置合わせされる。従って、第2のゲート導体層のポリシリコンの約半分超は、結晶的にチタン化される。スペーサは、第1のゲート導体層の角部を保護し、ゲート構造体を機械的な支持体に対してより強固にするために形成される。

(もっと読む)

半導体装置

【目的】ラッチアップ耐量が高く、低抵抗な縦型半導体装置を提供する。

【解決手段】n型ソース領域4の上面にp型第1ベース領域2aおよびp型第2ベース領域2bが形成され、該n型ソース領域4の下面にソース電極5が設けられ、p型第2ベース領域2bの上面に絶縁膜を介してドレイン電極9が形成されている。該p型第2ベース領域2bの上面にはゲート電極用トレンチと、該第1ベース領域2aと第2ベース領域2bおよびn型ソース領域4を短絡する短絡用トレンチが並設されている。該ゲート電極用トレンチの側壁にはn型ドリフト領域6とn型ドレイン領域8がRESURF状に形成され、短絡用トレンチには短絡用導電体12が形成されて該導電体12は該ドレイン電極9と絶縁されている。

(もっと読む)

電極の作製方法

【課題】金属ドナードープとは全く異なる観点から、電子注入機能および/または正孔注入機能を実現した有機デバイス用電極を提供することを目的とし、また、安定した均質な電極を作製できる電極の形成方法を提供することを目的とする。

【解決する手段】微粒子状の導電性無機化合物からなる導電性微粒子と、π共役系有機化合物とを同一の溶媒に分散させる第1の工程と、前記導電性微粒子と前記π共役系有機化合物とを分散させた前記溶媒を電極形成面へ湿式塗布する第2の工程と、を有する。

(もっと読む)

電気化学デバイス

本発明は、そのレドックス状態を電気化学的の変える能力を有する電気化学的活性層(205)を含んでなる電気化学デバイスに関わる。電解質(201)と電気化学的活性層(205)との間に、耐食性材料の電極(210)の部分(210)を供することにより、電気化学デバイスの電気化学反応による、望ましくない変色が減少する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗の低い半導体装置およびその製造方法を提供する。

【解決手段】複数の層を有する半導体層37の第1の面37aに形成されたソース電極12およびゲート取り出し電極14と、第1の面37aと対向する第2の面37bに形成されたドレイン電極16と、ソース電極12上に分散して形成された複数の第1柱状電極13と、ゲート取り出し電極14上に形成された第2柱状電極15と、ドレイン電極16上に分散して形成された複数の第3柱状電極17と、複数の第1柱状電極13の間、および第2柱状電極15と隣接する第1柱状電極13との間を埋めて、ソース電極12、ゲート取り出し電極14、および半導体層37を覆う第1樹脂層18と、複数の第3柱状電極17の間を埋めて、ドレイン電極16を覆い、第1樹脂層18に連接した第2樹脂層19と、を具備する。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

絶縁ゲートトランジスタ

【課題】 小型であり、スライドによる短絡を防止することができる絶縁ゲートトランジスタを提供する。

【解決手段】 絶縁ゲートトランジスタであって、半導体基板と、第1金属層と、第2金属層と、絶縁層と、メッキ層を有している。第1金属層は、半導体基板の上面に形成されている。第2金属層は、半導体基板の上面に形成されており、第1金属層の側方に間隔を空けて配置されている。第1金属層の下の半導体基板には第1半導体領域と第1ゲート電極を含む第1アクティブ領域が形成されている。絶縁層は、第2金属層と、第1アクティブ領域上の第1金属層の第2金属層側の一部分を覆っている。メッキ層は、絶縁層に覆われていない範囲の第1金属層の表面に形成されている。第1アクティブ領域の上部の絶縁層には、開口部が形成されている。メッキ層は、さらに、開口部内の第1金属層の表面にも形成されている。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストの増加を抑制しつつ、SiC基板の一方面に直接接合されるメタル層の接続信頼性を向上でき、さらにはSiC基板に対するメタル層のオーミック接合を確保することのできる半導体装置およびその製造方法を提供すること。

【解決手段】SiC基板2を有する半導体装置1において、SiC基板2の裏面22側の表層部分に、表面21側の表層部分よりもカーボンが高濃度に含まれる高カーボン濃度SiC層3を形成する。そして、その高カーボン濃度SiC層3の表面にドレイン電極17を直接接合する。

(もっと読む)

アイランドマトリックス化窒化ガリウムマイクロ波トランジスタおよびパワースイッチングトランジスタ

単位面積あたりの電流処理能力が従来の窒化ガリウム(GaN)デバイスよりも非常に優れたGaNデバイスを開示する。当該改良は、レイアウトトポロジの改良によるものである。フィンガー電極ではなくアイランド電極を使用する当該レイアウトスキームは、従来のインターデジタル構造よりも活性面密度を増加させることを示す。当該アイランドトポロジを用いて超低オン抵抗トランジスタを構築することができる。具体的には、本発明は、従来通りのGaN水平方向技術および電極間隔を用いており、すべての水平方向GaN構造のコストパフォーマンス/実効性能を高める手段を提供する。

(もっと読む)

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置

【課題】オン電圧を低減した半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、前記第1の半導体層の上に設けられた第2導電型の第2の半導体層と、前記第1の半導体層の上に前記第2の半導体層と接して設けられた前記第1の半導体層よりも不純物濃度の高い第1導電型の第3の半導体層と、前記第2の半導体層に接続された第1の金属層と、前記第3の半導体層に接続され前記第1の金属層とは異なる金属からなる第2の金属層と、を有する第1の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

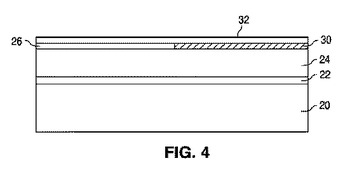

半導体発光デバイスのための反射性コンタクト

半導体構造が、n型領域20とp型領域24との間に配された、発光層22を含んでいる。p側電極が、p型領域の一部の上に配されている。p側電極は、p型領域の第1の部分と直接接触する反射性の第1の材料26と、その第1の部分に隣接するp型領域の第2の部分と直接接触する第2の材料30とを含んでいる。第1の材料26および第2の材料30は、同一の厚さのプラナー状の層として形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

121 - 140 / 578

[ Back to top ]