Fターム[4M104FF19]の内容

Fターム[4M104FF19]に分類される特許

1 - 18 / 18

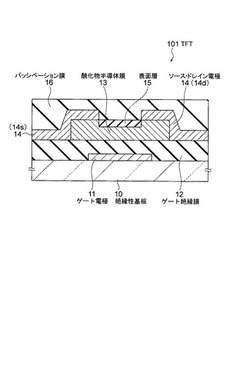

薄膜デバイス及びその製造方法

【課題】酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上のインジウムを含む酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分の表面層15におけるXPSスペクトルのインジウム3d軌道起因のピーク位置が、表面層15の下部に存在する酸化物半導体領域におけるXPSスペクトルのインジウム3d軌道起因のピーク位置よりも、高エネルギ側にシフトしている。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】バリアメタル層を有する半導体装置を製造するに際し、パーティクルの発生を抑制可能な製造方法、及びこの製造方法を用いる半導体装置の製造装置を提供する。

【解決手段】

2つの金属層の間に金属化合物層が挟まれてなるバリアメタル層を有する半導体装置を製造するに際し、チタン及びタンタルのいずれか一方の金属元素から構成されるターゲットを希ガスの雰囲気でスパッタして、複数の金属層を下地配線上に積層する過程において最下層となる第1金属層に酸化処理を施す。次いで、最下層となる第1金属層の表面に第1金属酸化物層を形成した後に、層間において構成元素が異なるように、一つ以上の金属層を含む下地の表面に対して酸化処理、窒化処理、及び酸窒化処理のいずれかの処理を施す。こうした処理より第2金属化合物層を形成する。上記金属化合物層は、金属酸化物層の他、金属窒化物層や金属酸窒化物層であってもよい。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

発光装置及び発光装置の作製方法

【課題】発光装置の信頼性を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路用トランジスタを含む駆動回路部と、画素用トランジスタを含む画素部とを有する発光装置であり、駆動回路用トランジスタ及び画素用トランジスタは、酸化物絶縁層と一部接する酸化物半導体層を含む逆スタガ型のトランジスタである。画素部において酸化物絶縁層上にカラーフィルタ層と発光素子が設けられ、駆動回路用トランジスタにおいて、酸化物絶縁層上にゲート電極層及び酸化物半導体層と重なる導電層が設けられる。なお、ゲート電極層、ソース電極層及びドレイン電極層は金属導電膜を用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置の製造方法

【課題】Ru含有膜の表面に形成される金属含有膜の成膜性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を含むものである。基板(半導体素子や層間膜が形成された半導体基板など)にRu含有膜を形成する工程(S100)、Ru含有膜の表面と接するように、Ruより酸化還元電位が低い金属を含有する膜を形成する工程(S102)、基板をめっき液に浸漬させて、当該膜にめっき液を接触させる工程(S104)、基板をめっき液に浸漬させた状態で、当該膜を電気分解により除去してRu含有膜を露出させるとともに、露出したRu含有膜の表面に金属含有膜を電解めっきにより形成する工程(S106)。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】閾値電圧以外の電流特性に大きな影響を与えることなく、選択的に閾値電圧を制御できる有機薄膜トランジスタを提供する。

【解決手段】本発明の有機薄膜トランジスタ100は、基板1上に、ゲート電極2と、ゲート絶縁膜3と、ソース電極4と、ドレイン電極5と、有機半導体層7とが形成されており、さらに、ソース電極4表面に、ベンゼンチオール化合物からなるチオール化合物層8が形成され、ドレイン電極5の表面に、ベンゼンチオール化合物からなるチオール化合物層9が形成されている。

(もっと読む)

バリア膜とドレイン電極膜およびソース電極膜が高い密着強度を有する薄膜トランジスター

【課題】バリア膜とドレイン電極膜およびソース電極膜が高い密着強度を有する薄膜トランジスターを提供する。

【解決手段】上記酸化ケイ素膜のバリア膜と、上記純銅膜のドレイン電極膜およびソース電極膜の間に、水素プラズマ処理後の厚さ方向断面組織が、(a)上記純銅膜のドレイン電極膜およびソース電極膜側に形成された純銅化帯域と、(b)上記酸化ケイ素膜のバリア膜との界面部に形成され、構成成分がCuとCaと酸素とSiからなる成分凝集帯域、の2帯域で構成され、上記成分凝集帯域の厚さ方向に形成されたCaおよび酸素の含有ピークの最高含有量が、それぞれCa:5〜20原子%、酸素:30〜50原子%、であり、かつ、10〜100nmの目標膜厚を有する密着強化膜を介在させる。

(もっと読む)

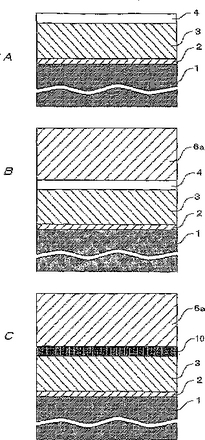

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純AlまたはAl合金のAl系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてAl系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純AlまたはAl合金のAl系合金膜とを備えた配線構造であって、前記半導体層と前記Al系合金膜との間に、基板側から順に、窒素、炭素、およびフッ素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F)層と、AlおよびSiを含むAl−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F)層を構成する窒素、炭素、およびフッ素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

スタックゲート型不揮発性半導体メモリ

【課題】半導体基板上において、下方に浮遊ゲートを有するとともに上方に制御ゲートを有するメモリセルトランジスタの、前記制御ゲートを完全にシリサイド化するとともに、前記半導体基板上において形成した選択ゲートトランジスタなどの制御トランジスタの、シリサイド化の過度の進行を抑制し、書き込み速度の遅延や閾値などの変動を抑制したスタックゲート型不揮発性半導体メモリを提供する。

【解決手段】メモリセルトランジスタの制御ゲートは、酸化層を含まないシリサイドから構成し、制御トランジスタは、層間絶縁膜を貫通するようにして半導体層及びシリサイド層を電気的に接続する追加のシリサイド層を有し、前記追加のシリサイド層は、底面及び側面において、前記半導体層及び前記シリサイド層と、シリサイド化進行防止層で離隔するようにして構成する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】電極材料の材料選択性が広く、キャリア注入効率の高い薄膜トランジスタおよびその製造方法を提供することを課題とする。

【解決方法】絶縁基板上に少なくとも、ゲート電極、ゲート絶縁膜が順次積層され、且つ前記ゲート絶縁膜上にソース電極とドレイン電極が設けられ、且つ半導体膜が前記ソース電極と前記ドレイン電極との間の前記ゲート絶縁膜上に設けられた薄膜トランジスタであって、前記ソース電極と前記ドレイン電極が電子吸引性の官能基を有する化合物で表面処理されていることを特徴とする薄膜トランジスタ。

(もっと読む)

MIS型半導体装置およびMIS型半導体装置の製造方法

ゲート絶縁膜に高誘電率膜を用いるMOSFETにおいて、基板−高誘電率膜間の低誘電率層(シリコン酸化膜)を増大させないようにするために、基板(1)上に高誘電率膜(3)、拡散バリア層(4)を堆積した後、高誘電率膜(3)の膜質改善のための熱処理を行う。次に、ゲート電極材料膜を堆積し、これをパターニングしてゲート電極(6)を形成する。このエッチング工程において、高誘電率膜3)はその側面がプラズマに曝されることにより、電荷が注入されまたダメージを受ける。この電荷を逃がしダメージを修復するために拡散バリア層(8)でゲート部を含む全面を被覆して熱処理を行う。その後、ソース・ドレイン領域となる不純物拡散層を形成する。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]