Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

441 - 460 / 590

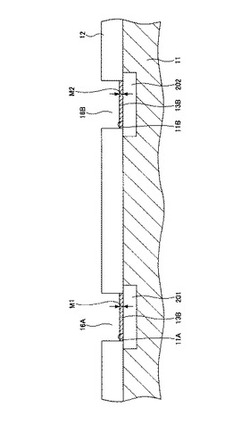

半導体装置の製造方法

【課題】本発明は、Si基板と接続される配線パターンを備えた半導体装置の製造方法に関し、Si基板上におけるSiノジュールの発生を十分に抑制すると共に、半導体装置の製造コストを低減することを課題とする。

【解決手段】開口部16A、16Bを有した絶縁膜12が形成されたSi基板11を、所定の温度Txに加熱された温水に浸漬させて、開口部16A、16Bに露出されたSi基板11上に所定の厚さM1、M2を有する酸化膜13A、13Bを形成し、その後、開口部16A、16Bを充填すると共に、絶縁膜12の上面12Aに亘るように配線パターンを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】ショットキバリア半導体装置において、少ない逆方向洩れ電流と、より高い阻止電圧を有し、順方向電圧降下が小さく電力効率の高い効率的な半導体装置であって、サージや過渡電圧に対して高い耐久性を有する半導体装置を提供すること。

【解決手段】半導体基板101の第1主面上に低濃度の半導体層102が形成され、前記低濃度の半導体層表面から半導体基板101に至る1つ以上のトレンチ103によって、前記低濃度の半導体層内に1つ以上のメサ102aを形成し、前記メサ102aとトレンチ103の境界部に絶縁皮膜104を形成し、絶縁皮膜104の表面上でかつトレンチ内部に第1の電極105を形成し、前記低濃度の半導体層表面にショットキ接合を形成する第2の電極106を前記第1の電極105とオーミック接合して形成し、半導体基板101の第2主面上に第3の電極107を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】改善されたリセスチャンネルトランジスタを備えた半導体素子及びその製造方法に関するものである。

【解決手段】本発明は、半導体素子及びその製造方法に関し、特に3次元リセスチャンネル構造を埋め込む下部ゲート電極を第1下部ゲート導電層、リセスチャンネル構造の埋込み時に発生するシームとその移動を防止する支持層及び第2下部ゲート導電層の積層構造で形成するように半導体素子を設計することで、3次元リセスチャンネル構造のトポロジー特性により、リセスチャンネル構造内に生成するシームと後続する熱処理工程によるシームの移動現象を最小化し、素子の動作特性を向上させることのできる技術である。

(もっと読む)

半導体装置

【課題】半導体装置において半導体素子間の分離を好適に達成するとともに半導体装置の小型化を図ること。

【解決手段】半導体基板1と、半導体基板1上に形成されたエピタキシャル層2と、半導体基板1とエピタキシャル層2との間に形成された埋め込み層3と、エピタキシャル層2表面から埋め込み層3に達する第1のトレンチ7と、第1のトレンチ7内に埋め込まれるとともに埋め込み層3と接続されたドレイン取出電極8bと、ドレイン取出電極8bを電極とした半導体素子と、エピタキシャル層2表面からその半導体素子を囲むように設けられた第2のトレンチ5とを備え、第2のトレンチ5内の少なくとも側壁を絶縁膜6aで被覆した。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】トレンチ構造のトランジスタの形状及び電極構造に関して自由に設計を行なうことができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】シリコン基板10の表面には複数の凹部10a,10a,…が設けられ、各凹部10aには、表面からエミッタ領域REとベース領域RBとがこの順序で配置されている。その他の領域がコレクタ領域RCとなってトランジスタを構成する。基板全面に電極としての導電体を設ける場合、凹部10aによる段差のため、ベース領域RB上のベース電極12Bとエミッタ領域RE上のエミッタ電極12Eとは分離された状態で形成される。そして、エミッタ電極12E及びベース電極12Bを被覆する層間絶縁膜13を形成し、層間絶縁膜13を介してエミッタ電極12E及びベース電極12Bとそれぞれコンタクトを取るためのボンディングパッド14E及び14Bをデバイスの上層に形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 少ない工程数で製造することが可能であるとともに、p型部分領域52とソース電極58の間のコンタクト特性とソース領域54とソース電極58の間のコンタクト特性の両者を改善すること。

【解決手段】 半導体装置10は、p型の不純物を含む窒化ガリウム系半導体のp型部分領域52とn型の不純物を含む窒化ガリウム系半導体のソース領域54を備えている。半導体装置10はさらに、p型部分領域52及びソース領域54に電気的に接続するソース電極58を備えている。半導体装置10は、p型部分領域52とソース電極の間に形成されているとともに酸化ガリウムを含むコンタクト層56を備えている。コンタクト層56は、ソース領域54とソース電極58の間にも形成されている。

(もっと読む)

GaN系半導体装置及びIII−V族窒化物半導体装置

【課題】耐圧が高く且つオン電圧の低いGaN系半導体装置を提供する。

【解決手段】導電性の基板62と、基板62上に形成され、表面の一部が凸部形状をなすIII−V族窒化物半導体層64と、III−V族窒化物半導体層64の凸部64bの上面にオーミック接合して形成されるソース電極72と、凸部64bの側面にショットキー接合して形成されるゲート電極74と、基板62の裏面にオーミック接合して形成されるドレイン電極76とを備えることを特徴とするIII−V族窒化物半導体装置。

(もっと読む)

半導体装置

【課題】ドリフト領域が主に窒化ガリウム層で構成された縦型のパワー半導体装置において、電界集中を緩和して高耐圧とすることができる新たな耐圧構造を有する半導体装置を提供すること。

【解決手段】高濃度シリコン基板の上に窒化ガリウムの半導体層を積層し、窒化ガリウム半導体層側の表面には、窒化ガリウム層の80%以上の深さにエッチングしたメサ溝によって囲まれる主電流の流れる活性領域をそなえる構成の半導体装置とする。

(もっと読む)

半導体装置

【課題】nチャネルMISFETのソースおよびドレインにニッケルまたはニッケル合金のシリサイド領域を形成する場合であっても、オフリーク電流が増加しにくい半導体装置を実現する。

【解決手段】ソースおよびドレイン上にニッケルまたはニッケル合金のシリサイド領域が形成されたnチャネルMISFETのチャネル長さ方向を、半導体基板の結晶方位<100>に平行となるよう配置する。結晶方位<100>の方向には、ニッケルまたはニッケル合金のシリサイド領域は延伸しにくいため、nチャネルMISFETのソースおよびドレインにニッケルまたはニッケル合金のシリサイド領域を形成する場合であっても、オフリーク電流が増加しにくい半導体装置が得られる。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】 窒化物半導体層に形成される制御電極のショットキ特性の向上、高耐圧化、周波数分散の抑制を可能とし、スレッショホールド電圧の制御が容易なノーマリーオフ動作を実現できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 基板上に、第1の窒化物半導体層と微結晶構造からなる第2の窒化物半導体層を形成し、制御電極形成領域にマスク膜を形成する。マスク膜を用いて露出する第1の窒化物半導体層上に、第3の窒化物半導体層と微結晶構造からなる第4の窒化物半導体層を形成する。マスク膜を除去し、第2の窒化物半導体層上に制御電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低抵抗な接合界面を具備し、ジャンクションリークが抑制された高性能なMIS型電界効果トランジスタを有する半導体装置およびその製造方法を提供する。

【解決手段】チャネル領域が形成される第1導電型の第1の半導体領域100と、ゲート絶縁膜101を介して形成されたゲート電極102,103と、チャネル領域の両側に形成されたSiXGe1−X層106と、SiXGe1−X層106上に形成された、不純物の濃度が1021atoms/cm3以上1022atoms/cm3以下の第2導電型の第2の半導体領域108と、第2の半導体領域上に形成されたNi(ニッケル)を含有するシリサイド層110を具備する電界効果トランジスタを有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置

【課題】終端部での局所的な電界集中を抑えることで、高信頼性、高耐量が得られる半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、第1の半導体層の主面上に設けられた第1導電型の第1の半導体ピラー領域と、第1の半導体層の前記主面に対して略平行な方向に第1の半導体ピラー領域と共に周期的配列構造を形成するように、第1の半導体ピラー領域に隣接して第1の半導体層の主面上に設けられた第2導電型の第2の半導体ピラー領域と、第1の半導体ピラー領域及び第2の半導体ピラー領域の周期的配列構造が形成された素子部の外側の終端部における第1の半導体層の上に設けられ、第1の半導体ピラー領域よりも不純物濃度が低い第1導電型の第2の半導体層と、第2の半導体層中に選択的に埋め込まれた第2導電型半導体の埋め込みガードリング層と、を備えている。

(もっと読む)

ヘテロ接合電界効果型トランジスタ

【課題】コンタクト抵抗が小さくかつゲートリーク電流の少ないノーマリオフタイプのヘテロ構造電界効果型トランジスタを提供する。

【解決手段】分極性を有する化合物半導体を用いて作製されたヘテロ接合電界効果型トランジスタにおいて、その化合物半導体の無極性面上にゲート電極(G)が形成されており、その化合物半導体の極性面上にソース・ドレイン電極(S、D)が形成されていることを特徴としている。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が小さいオーミック電極を備えたIII−V族窒化物半導体を用いた半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板11の上に順次形成された、第1のIII−V族窒化物半導体層12及び第1のIII−V族窒化物半導体12と比べてバンドギャップが大きい第2のIII−V族窒化物半導体層13と、オーミック電極14とを備えている。オーミック電極14は、下部が第2のIII−V族窒化物半導体層13を貫通し且つ第1のIII−V族窒化物半導体層12における2次元電子ガス層よりも下側の領域に達するように形成されている。第1のIII−V族窒化物半導体層12及び第2のIII−V族窒化物半導体層13におけるオーミック電極14と接する部分には、不純物ドープ層18が形成されている。

(もっと読む)

ショットキバリアダイオードおよびエピタキシャル基板

【課題】オン抵抗の上昇を抑える共に、リーク電流を低減することが可能なショットキバリアダイオードの提供。

【解決手段】導電性III族窒化物基板13は、第1の面13aおよび第2の面13bを有する。また、導電性III族窒化物基板13は、1×106cm−2以下の転位密度D13を有する。n型窒化ガリウム系半導体ドリフト層15は、基板13の第1の面13a上に設けられており、また1×1017cm−3以下のキャリア濃度N15を有する。第1のn型窒化ガリウム系半導体層17は、n型窒化ガリウム系半導体ドリフト層15上に設けられており、また0.5×1017cm−3以下のキャリア濃度n17を有する。ショットキ電極19は、第1のn型窒化ガリウム系半導体層17にショットキ接合を成す。オーミック電極21は、基板13の第2の面上に設けられている。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース電極及びドレイン電極のコンタクト抵抗が小さく且つ電極の形成が容易な電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板10の上に形成され、一般式がInxAlyGa1−yN(0<x≦1、0≦y<1、0<x+y≦1)で表されるキャップ層25を含む窒化物半導体積層体20と、キャップ層25の上に互いに間隔をおいて形成されたノンアロイのソース電極31及びノンアロイのドレイン電極32とを備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みSiGeまたはSiCによるソース・ドレインを含むMISFETにおいてSTIのエッジ部分でファセットが発生しないMISFETを提供する。

【解決手段】Si基板10の表面層に形成されて素子形成領域を確定するSTI101と、ゲート絶縁膜13を介して素子形成領域のSi基板10上に形成されたゲート電極19と、ゲート電極19を挟むように、p型MISFETにあってはSiGeから、また、n型MISFETにあってはSiCから、Si基板10の表面層に形成されたソースまたはドレインをなす不純物拡散層61,63と、不純物拡散層61,63の表面に形成された第1のシリサイド62,64と、を備えるMISFETにおいて、STI101の表面の高さを第1のシリサイド62,64の高さと実質的に同一にする。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧性および耐湿性が向上された半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、トランジスタ等が形成される活性領域19を囲むように、分離領域13A、13Bを設けている。この分離領域13A等は、半導体基板11の上面から下面まで連続して延在していおり、内部にはシリコン酸化膜等から成る絶縁物層14Aが形成されている。従って、活性領域19が形成される半導体基板11の側面の全てを絶縁物により被覆することができるので、半導体装置の耐圧性および耐湿性を向上させることができる。

(もっと読む)

半導体装置

【課題】 本発明の目的は、設計の自由度を向上し得る半導体装置を提供する。

【解決手段】 本発明の半導体装置10は、ソースおよびドレイン間に配置される第1導電型の導電層27と、該導電層のソース側に、所定の間隔で埋め込み形成されたトレンチゲート26と、該トレンチゲートの隣り合う一方の側壁にそれぞれ隣接して前記トレンチゲートに印加される電圧で反転層を形成してソースおよびドレイン間の電流制御を行なうための第2導電型の反転層形成領域14と、逆方向電圧の印加による電界を緩和するために前記導電層に埋め込まれた第2導電型の埋め込み領域13と、を備えており、埋め込み領域13はトレンチゲートの隣り合う他方の側壁にそれぞれ隣接して当該トレンチゲートの深さ寸法より深い位置まで埋め込み形成され、かつソースに直接的に接続されている。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた縦型ショットキバリアダイオード(SBD)の高耐圧化を実現できるようにする。

【解決手段】半導体装置は、窒化ガリウムからなり、第1の面及び該第1の面と対向する第2の面を有するドリフト層14と、ドリフト層14の第1の面上に形成されたショットキ電極16と、ドリフト層14の第2の面とコンタクト層13を介して電気的に接続されたオーミック電極15とを有している。ドリフト層14は、少なくとも上部にその一部が選択的に高抵抗化された高抵抗領域14aを有している。

(もっと読む)

441 - 460 / 590

[ Back to top ]