Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

521 - 540 / 590

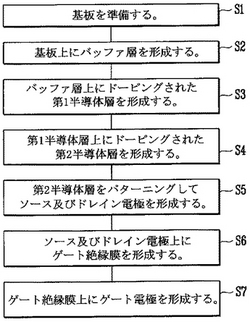

薄膜トランジスター及びその製造方法

【課題】工程を単純化するようにした薄膜トランジスターの製造方法を提供する。

【解決手段】基板上に少なくとも一つのバッファー層を形成する段階と、前記バッファー層上に第1半導体層を形成する段階と、前記第1半導体層上にドーピングされた第2半導体層を形成する段階と、前記第2半導体層をパターニングしてソース及びドレイン電極を形成する段階と、前記ソース及びドレイン電極上にゲート絶縁膜を形成する段階及び前記ゲート絶縁膜上にゲート電極を形成する段階とを含む。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、過電圧から素子を保護するために設けられた保護ダイオードの耐圧特性が向上しないという問題があった。

【解決手段】本発明の半導体装置では、基板2上のエピタキシャル層3には、素子保護用の保護ダイオード1が構成されている。エピタキシャル層3表面にはショットキーバリア用金属層14が形成され、ショットキーバリア用金属層14の端部20の下方にはP型の拡散層9が形成されている。そして、P型の拡散層9よりカソード領域側にフローティング状態のP型の拡散層10、11が形成され、アノード電位が印加された金属層18と容量結合している。この構造により、空乏層の大きな曲率変化を低減し、保護ダイオード1の耐圧特性を向上させている。

(もっと読む)

メモリ素子のトランジスタ構造及びその製造方法

【課題】 新しい形態のメモリ素子のトランジスタ構造及びその製造方法を提供すること。

【解決手段】本発明のトランジスタは、基板111の所定領域から突出した活性領域111aと、活性領域内のチャネル領域に形成された凹溝部gと、活性領域の周りの基板に形成された、前記凹溝部を含む活性領域の上面より低い位置にある表面を有するフィールド酸化膜112と、前記凹溝部、及び表面が露出した前記活性領域の上に形成されたゲート絶縁膜113と、前記凹溝部に重畳し、活性領域の上を横切って延伸するゲート電極114とを備え、ソース及びドレーンラインに沿ったX−X’断面はリセストランジスタ構造であり、ゲートラインに沿ったY−Y’断面は突起型トランジスタ構造である。

(もっと読む)

可制御半導体ダイオード、電子部品および電圧中間形コンバータ

少なくとも1つのpn接合を有し、第1の状態と第2の状態との間で切換可能であり、かつ第2の状態が第1の状態に比べて高い順方向導通抵抗および小さい蓄積電荷を有する可制御半導体ダイオードにおいて、可制御半導体ダイオードがショットキーダイオード部分とMOSFET部分とからなる直列接続を有し、この直列接続がpn接合を橋絡する。本発明のダイオードは、高い信頼性をもって機能し、かつ状態1と状態2との順方向電圧降下間に大きな比を達成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を低減し、素子特性のばらつきの少ない半導体装置の製造方

法を提供する。

【解決手段】多結晶シリコン層を構成要素として備え、この多結晶シリコン層が

P型多結晶シリコン層5とN型多結晶シリコン層6とを有する半導体装置の製造

方法であって、P型多結晶シリコン層5を形成する工程と、P型多結晶シリコン

層5と一部分が重なるようにN型となる不純物を導入してN型多結晶シリコン層

6を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 活性領域とタングステンプラグとの接触面積の低下を防止する。

【解決手段】 シリコン基板1にSTI2を形成し、活性領域3を区画形成する。ゲート電極4aを形成した後に、活性領域3のコンタクトホール5を形成する領域の表面を上に凸の滑らかな表面となるようにRIE加工する。層間絶縁膜10にコンタクトホール5を形成する際に、パターンずれが発生してもコンタクトプラグ13との接触面積の低下を防止できる。設計ルールの縮小化に伴う不具合を回避することができる。

(もっと読む)

ショットキーダイオード、電界効果トランジスタおよびその製造方法

【課題】 高耐圧で、高い動作電圧を有するショットキーダイオードや電界効果トランジスタを作製する。

【解決手段】 半絶縁性基板31上に積層されたアンドープAlN層32と、アンドープAlN層32上に積層されたSiドープn型AlN層33と、Siドープn型AlN層33上に、高濃度Siドープn型AlN層34を介して形成されたオーミック電極36と、Siドープn型AlN層33上に形成されたショットキー電極35とを備え、Siドープn型AlN層33のSi濃度は、5×1016cm−3〜5×1018cm−3であり、高濃度Siドープn型AlN層34のSi濃度は、5×1019cm−3以上である。

(もっと読む)

半導体装置

【課題】 電極とチャネル層間のオーミック抵抗の少ない良好な高周波特性を有する半導体装置を得る。

【解決手段】 キャップ層としてのアンドープガリウム砒素(GaAs)層15a上のドレイン電極16及びソース電極17の形成位置に凹状の溝16a及び17aを設け、これらの溝16a及び17aにそれぞれドレイン電極16及びソース電極を17を形成し、それぞれの電極とチャネル層としてのn型ガリウム砒素(GaAs)層13との距離を短くする。また、ドレイン電極16及びソース電極17を、キャップ層としてのアンドープガリウム砒素(GaAs)層15aの表面に張り出すような形状に形成して、溝16a及び17aの周縁部の露出を防ぎ、この部位における表面準位の変動がチャネル層としてのn型ガリウム砒素(GaAs)層13に及ぼす影響を減らす。

(もっと読む)

トレンチゲート電界効果トランジスタおよびその形成方法

一体的に統合されたトレンチFETおよびショットキーダイオードを含む構造体であって、半導体領域内に伸張するゲートトレンチと、ゲートトレンチの各側面に位置し、実質的に三角形状のソース領域と、隣接するトレンチ間における半導体領域内部に伸長するコンタクト開口と、コンタクト開口を満たし、各ソース領域の傾斜した側壁部の少なくとも一部に沿ってソース領域と電気的に接触し、且つコンタクト開口の底部に沿って半導体領域と電気的に接触し、且つ半導体領域とショットキーコンタクトを形成する導電体層と、を含む。 (もっと読む)

半導体装置およびその製造方法

【課題】高温リーク電流が少なく、低オン抵抗、高速動作が可能なバンドギャップアシスト構造のショットキーダイオードとしての半導体装置およびその製造方法を提供する。

【解決手段】基板領域1と、基板領域1上に形成された第1エピタキシャル成長層3と、第1エピタキシャル成長層3上に形成され, 第1エピタキシャル成長層3よりも広いバンドギャップエネルギーを備えることによって,第1エピタキシャル成長層3とヘテロ接合を形成する第2エピタキシャル成長層2と、第1エピタキシャル成長層3が形成される基板領域1表面と反対側の表面上に形成されるカソード電極5と、第2エピタキシャル成長層2上に形成されるアノード電極4とを備える。

(もっと読む)

窒化物半導体装置

【課題】 耐圧が高く、且つオン電圧が低い、新たなIII−V族窒化物半導体装置を提供する。

【解決手段】 III−V族窒化物半導体層からなる凸形状の第1の窒化物半導体層の側面に、微結晶構造の第2の窒化物半導体層が積層し、凸形状の上面に第1のアノード電極がショットキー接合し、側面に第2のアノード電極がショットキー接合する。また第2のアノード電極と第2の窒化物半導体層との間で形成される接合のショットキーバリアの高さが、第1のアノード電極と第1の窒化物半導体層との間で形成される接合のショットキーバリアの高さより高くなるように構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 雑音特性を劣化を抑制して高周波特性の向上を可能とする半導体装置を提供する。

【解決手段】 基体層23、基体層23上の基体層23より幅の狭い中間層22、及び中間層22上の中間層22より幅の狭い頭部21を備える第1導電型(n型)のコレクタ領域2と、頭部21の上面に配置された第2導電型(p型)のベース領域3と、ベース領域3の上部の一部に配置された第1導電型(n型)のエミッタ領域4と、基体層23の上面から頭部21の側面まで達する絶縁領域5と、絶縁領域5の上面にベース領域3の側面と接して配置されたベース電極6とを備える。

(もっと読む)

半導体素子

【課題】 発振のS/N比を向上させ、安定した波形の低周波発振を可能とする半導体素子を提供する。

【解決手段】 低周波発振半導体素子10は、半導体基板1と、半導体基板1の裏面に接して配置された裏面電極4と、半導体基板1の表面に接し、平面的に見て裏面電極4と重なるように形成されたパッド電極2とを備えている。パッド電極2の垂直真下の領域Aに存在する半導体基板1の表面のエッチピット密度が0または3×104/cm2以上6×104/cm2以下である。

(もっと読む)

半導体装置の製造方法、半導体装置、半導体レーザ装置、光伝送モジュールおよび光ディスク装置

【課題】歩留を向上させて、製造コストを低減することができる半導体装置の製造方法、半導体装置、半導体レーザ装置、光伝送モジュールおよび光ディスク装置を提供する。

【解決手段】n−GaAs基板101上にはp−Al0.5Ga0.5As第2上クラッド層111’を形成する。p−Al0.5Ga0.5As第2上クラッド層111’上には、p−Al0.5Ga0.5As第2上クラッド層111’のエッチング速度よりも遅いエッチング速度を持つIn0.25Ga0.75As0.54P0.46エッチング減速層112’を形成する。このIn0.25Ga0.75As0.54P0.46エッチング減速層112’上には、In0.25Ga0.75As0.54P0.46エッチング減速層112’のエッチング速度よりも速いエッチング速度を持つp++−GaAs第2コンタクト層114’を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクトプラグとのコンタクト抵抗を低減したトランジスタを有する半導体装置を提供する。

【解決手段】 トランジスタとコンタクトプラグとを有する半導体装置であって、トランジスタのドレイン電極は、ゲート電極側に設けられ、導電性不純物が拡散された第1の不純物拡散層3と、第1の不純物拡散層よりもゲート電極から離れて配置され、コンタクトプラグと接触し、第1の不純物拡散層よりも濃度の高い第2の不純物拡散層4と、第2の不純物拡散層よりもゲート電極から離れて配置され、コンタクトプラグと接触し、第2の不純物拡散層よりも濃度の高い第3の不純物拡散層5とを有する構成である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高耐圧な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】第一導電型の第一の半導体材料からなる半導体基体100と、半導体基体の第一主面に接するように形成されたアノード電極7と第一主面に対向する反対主面に接するように形成されたカソード電極6を備えた半導体装置において、アノード電極と半導体基体との間に、第一の半導体材料と第一の半導体材料とはバンドギャップの異なる第二の半導体材料とによって形成されるヘテロ接合と、ヘテロ接合と接するように第一の半導体材料に形成された不純物導入領域4からなる電界緩和領域5を備えたことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ガードリングからのリーク電流を低減することができるショットキーダイオードなどの半導体装置および半導体装置の製造方法を提供する。

【解決手段】 N型のSiCからなる高濃度層3と、高濃度層3上に積層されN型のSiCからなり高濃度層3よりも不純物濃度が低いドリフト層4と、ドリフト層4上に積層されN型のSiCからなりドリフト層4よりも不純物濃度が低い低濃度層6aと、低濃度層6a上に形成され低濃度層6aとショットキー接触したバリアメタル膜8と、P型のSiCからなり低濃度層6a内に埋設されている部位、低濃度層6aから露出している部位、その露出している部位の一部であってバリアメタル膜8の周辺部と接している部位を有するガードリング領域5とを有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の上昇や漏れ電流の増加を抑えつつ、微細化に伴う短チャネル効果を効果的に抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上には、ゲート絶縁膜2を介してゲート電極3が形成されており、ゲート電極3の側壁にはサイドウォール絶縁膜5が形成されている。サイドウォール絶縁膜5の直下の半導体基板1には、エクステンション領域6が形成されており、エクステンション領域6の外側には深いソース・ドレイン領域7が形成されている。ソース・ドレイン領域7の内側であって、ソース・ドレイン領域7と半導体基板1との界面に、拡散抑制膜8が形成されている。拡散抑制膜8は、例えば酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜からなる。拡散抑制膜8により、ソース・ドレイン領域7中の不純物の横方向拡散が抑制される。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキバリアダイオードとパワーMOSとが同一基板上に形成されたものであって,熱が局所的に集中して発生することを抑制し,高耐圧かつ低オン抵抗であり,製造が容易な半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置200は,ショットキバリアダイオードとパワーMOSトランジスタとが同一基板上に形成されたトレンチゲート型半導体装置であり,ショットキ領域とMOS領域とがトレンチゲート21を境界として交互に配置されている。さらに,N- ドリフト領域12中に濃度が異なる3つの領域(N- ドリフト領域12sm,N--ドリフト領域12s,Nドリフト領域12m)を設けることとしている。具体的に,ショットキ領域に位置するN--ドリフト領域12sは低濃度の領域とし,MOS領域に位置するNドリフト領域12mは高濃度の領域とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高速動作が可能なLDD型MISFETと、かつ高電圧駆動が可能なLDD型MISFETとを内蔵する半導体集積回路装置を低コストで実現する。

【解決手段】高速動作が可能なMISFETは、ゲートサイドウオール層に自己整合された高濃度領域に金属シリサイド層を有し、高電圧駆動が可能なMISFETは、上記ゲートサイドウオール層の幅よりも大きい幅を有するLDD部を有し、そのLDD部に接して高濃度領域を有し、そしてその高濃度領域に金属シリサイド層を有する。

(もっと読む)

521 - 540 / 590

[ Back to top ]