Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

561 - 580 / 590

半導体装置

【課題】ゲート電極近傍のヘテロ接合界面で生じる漏れ電流を低減する。

【解決手段】第一導電型の基板1とドレイン領域2からなる半導体基体と、該半導体基体の一主面に接し、該半導体基体とはバンドギャップが異なるヘテロ半導体領域3と、ヘテロ半導体領域3と前記半導体基体との接合部にゲート絶縁膜5を介して形成されたゲート電極6と、ヘテロ半導体領域3と接続されたソース電極6と、前記半導体基体とオーミック接続されたドレイン電極7と、少なくともヘテロ半導体領域3と前記半導体基体とゲート絶縁膜5とが互いに接する領域から所定距離離れたドレイン領域2中に、第二導電型のウェル領域4とを有し、ウェル領域4内に空乏層が形成されない場合の該ウェル領域4内のフリーキャリア濃度が、該ウェル領域4内に空乏層が形成される場合の空乏層内の空間電荷濃度よりも小さくなっている。

(もっと読む)

半導体装置

【課題】第一のヘテロ半導体領域とソース電極間のコンタクト抵抗を低減する。

【解決手段】N+型炭化珪素基板1及びN−型炭化珪素エピタキシャル層によるドレイン領域2からなる第一導電型の半導体基体と、前記半導体基体の一主面に接し、該半導体基体とはバンドギャップが異なる第一のヘテロ半導体領域9及び第二のヘテロ半導体領域10と、第一のヘテロ半導体領域9と前記半導体基体との接合部にゲート絶縁膜6を介して形成されたゲート電極7と、第一のヘテロ半導体領域9と接続されたソース電極12と、前記半導体基体とオーミック接続されたドレイン電極11とを有し、該半導体装置が複数の基本単位セルの並列接続により形成され、第一のヘテロ半導体領域9の少なくともソース電極12とコンタクトする側に、ソース電極12とコンタクトするために面積を拡大させた第一のヘテロ半導体領域9のコンタクト領域13を設けた構成。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧に優れ、強度の高いIII−V族窒化物半導体からなる半導体装置を実現する。

【解決手段】本発明の構造では、第1のソース電極106がバイアホール112を介して導電性基板101に接続されており、また、第2のソース電極110が形成されている。これにより、ゲート電極108とドレイン電極107との間に高い逆方向電圧が印加されても、ゲート電極108のうちドレイン電極107に近い側の端部に起こりやすい電界集中を効果的に分散または緩和することができるため、耐圧が向上する。また、素子形成層を形成する基板として導電性基板101を用いているため、導電性基板101には裏面まで貫通するバイアホールを設ける必要がない。したがって、導電性基板101に必要な強度を保持したまま、第1のソース電極106と裏面電極115とを電気的に接続することができる。

(もっと読む)

発光ダイオード

【課題】コンタクト層と透明電極とのオーミックコンタクトを容易に取ることができる発光ダイオードを提供する。

【解決手段】発光ダイオードは、p型AlGaInP活性層15、透明電極用p型GaAsコンタクト層17およびITO透明電極110を備えている。このp型GaAsコンタクト層17のキャリア濃度は1.0×1019cm-3に設定されている。

(もっと読む)

半導体素子のための非活性化保護リング

【課題】 半導体素子、特にショットキーダイオードのような金属対半導体整流接合を組み込む半導体素子を提供する。

【解決手段】 保護リングは、ショットキー接合又はショットキーダイオードの一部である半導体領域に形成される。保護リングは、高抵抗領域を形成するために、半導体コンタクト層を完全にアニール処理することなく半導体コンタクト層内へのイオン注入によって形成される。保護リングは、層のエッジ部か又は代替的に層のエッジ部からある一定距離を離して位置することができる。ショットキー金属接点は、層の上に形成され、ショットキー接点のエッジ部は、保護リングの上に配置される。

(もっと読む)

CMOSデバイスのソースおよびドレインの寄生抵抗低減

ドープされた半導体基板を与えることと、pn接合部を画定するべく基板に第二ドーパントを導入することと、pn接合部に対応する容量を低減するべくpn接合部付近の基板中に中性化種を導入することとを含む、半導体系デバイスを製造するための方法である。半導体系デバイスは、第一および第二ドーパントを有する半導体基板と、中性化種とを含む。第一および第二ドーパントはpn接合部を画定し、中性化種は、pn接合部に対応する容量を低減するべくpn接合部付近の第一ドーパントの一部を中性化する。 (もっと読む)

窒化物半導体素子およびその製造方法

【課題】 発光波長200nm付近で発光出力が極めて高い発光素子を提供し、またn型AlNを用いた高出力電子素子を提供すること。

【解決手段】 半導体または絶縁体基板上に、アンドープAlN層、n型AlN層、p型AlN層をエピタキシャル成長し、AlNのpn接合を形成する。これにより、欠陥の少ないアンドープAlN層によって電気的特性の優れたn型AlN層、p型AlN層が得られ、発光波長200nm付近において発光出力を大幅に増加できる。また、電子素子に適用した場合は、欠陥の少ないアンドープAlN層により電気伝導性が極めて優れたn型AlN層が得られるので、ショットキーバリア高さや絶縁破壊電圧を大幅に増加することができる。

(もっと読む)

GaN系電界効果トランジスタ

【課題】 動作時のオン抵抗が小さく耐圧が大きいGaN系電界効果トランジスタを提供することを目的とする。

【解決手段】ソース電極、ゲート電極、ドレイン電極、チャネル層を有するGaN系電界効果トランジスタにおいて、前記チャネル層の導電型と同一のコンタクト層が、前記チャネル層に至る深さのエッチング溝に埋め込まれ、かつ、前記コンタクト層はソース電極のみに接続していることを特徴とするGaN系電界効果トランジスタ。

(もっと読む)

窒化ガリウム系半導体発光素子及びその製造方法

【課題】 本発明は高い透過率を有する同時にp型GaN層との接触抵抗の問題を改善できる窒化ガリウム系半導体発光素子及びその製造方法に関するものである。

【解決手段】 本発明によれば、p-GaNから成る上部クラッド層の上部にMIO、ZIO、CIO(Mg、Zn、Cu中いずれかを含むIn2O3)でオーミック形成層をさらに形成した後、ITO等で具現される透明電極層と第2電極を形成することにより、上記上部クラッド層と第2電極との接触抵抗の問題を改善し、高い透過率を得られる。

(もっと読む)

半導体装置、及びそれらの作製方法

【課題】 本発明では、工程、装置を複雑化することなく、要求される特性を有する薄膜トランジスタを作製することを目的とする。また、薄膜トランジスタの特性を精密に自由に制御することで、高い信頼性や優れた電気特性を有する半導体装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 本発明は、薄膜トランジスタにおいて、ゲート電極層で覆われている半導体層のソース領域側かドレイン領域側の一方に、低濃度不純物領域を作製する。低濃度不純物領域は、ゲート電極層をマスクとして、半導体層表面に対し、斜めにドーピングすることによって形成される。よって、薄膜トランジスタの微細な特性の制御を行うことができる。

(もっと読む)

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 n型SiCに対して良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】 第1の主面と該第1の主面に背向する第2の主面とを有するn+型SiC基板11と、第2の主面上に形成されたエピタキシャル層13と、エピタキシャル層13上に形成されると共に、エピタキシャル層13とオーミック接触した電極14とを有することを特徴とする。

(もっと読む)

ショットキダイオードを含む半導体装置及びその製造方法

【課題】 本発明は、比較的低いコストにより、比較的低いシリーズ抵抗を有するショットキダイオードを含む半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 ショットキダイオードにおいて、ウェル領域の表面領域の不純物濃度はそのウェル領域の不純物濃度よりも小さく、ウェル領域の表面領域より深い、所定の深さ領域の不純物濃度はそのウェル領域の不純物濃度よりも大きく分布する、ウェル領域と同一型の不純物の濃度分布をウェル領域内に設定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】HEMT性能を向上させる。

【解決手段】

本発明は、ヘテロ構造上で、若干のHEMTトランジスタを製造する方法と同様に、MOCVDを用いてSiN層をいささかも除去することなく、表面に接点を蒸着させることにより、構造の冷却および反応器からの試料の取り出しに先立ち、高温で成長が起こる反応器内で、最上部AlGaN層上の表面を薄いSiN層で覆うことにより、より高性能(出力)を伴い、有機金属気相成長法により成長させられた、HEMT、MOSHFET、MISHFET素子、またはMESFET素子のような、III族−N電界効果素子を製造するための新規な方法を解説している。本発明は素子も解説している。

(もっと読む)

電力用半導体装置

【課題】 ソフトスイッチング方式に適したパワーMOSFETを有する電力用半導体装置を得ることを可能にする。

【解決手段】 スーパージャンクション構造を有したMOSFETのライフタイムを短くし、ソース・ドレイン間にリカバリーが高速なスーパージャンクション構造を有したショットキーバリアダイオードを接続する。

(もっと読む)

半導体装置

【課題】 リーク電流の低減が可能でかつ歩留まりがよい半導体装置を提供する。

【解決手段】 半導体装置1は、縦型のパワーMOSFETである。n型の複数の第1半導体領域9は、n型の単結晶シリコン層に複数のトレンチ13を設けることにより形成される。複数のトレンチ13の底面15上にそれぞれ絶縁領域17が設けられている。各トレンチ13には、p型のエピタキシャル成長層である第2半導体領域11が埋め込まれている。領域9,11によりスーパージャンクション構造が形成されている。

(もっと読む)

ショットキー素子及びその形成方法

導電層(41)は第1部分を含み、第1部分は下層の第1導電型の第1領域とともにショットキー領域(25)を構成する。第2導電型の第2領域(11)は第1領域(22)の下に設けられ、第2導電型は第1導電型とは逆の導電型である。第1導電型の第3領域(21)は第2領域(11)の直下に位置し、かつ素子のカソード(52)に電気的に接続される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 小型化及び低コスト化できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】 N型半導体基板12下面に形成され、該N型半導体基板12よりも高抵抗なN型エピタキシャル層14下面の一部分にP型拡散層22,22を設け、該P型拡散層22,22及びその周辺のN型エピタキシャル層14下面に第1電極層20を有する半導体装置10において、前記N型エピタキシャル層14下面の前記第1電極層20が形成されていない部分の凹部の底に、N型半導体基板12に接続された第2電極層21を有する構成にする。

(もっと読む)

半導体装置

【課題】 オン抵抗を低減でき、リーク電流も抑制できる半導体装置。

【解決手段】 半導体装置は、所定間隔を隔てて略平行に配置される複数のトレンチ1と、これらトレンチ1の内部に絶縁層2を介して形成される複数のソース3と、トレンチ1の上部に形成されるソース金属層4と、隣接するトレンチ1の間に形成されるn-半導体領域5と、トレンチ1の下部に形成されるn型ドリフト層6と、n型ドリフト層6の下部に形成されるn+基板7と、n+基板7の下面に形成されるドレイン金属層8とを備えている。トレンチ1内のソース3はp型ポリシリコンで形成されている。ソース3はソース金属層4と接触している。n-半導体領域5とソース金属層4とはショットキー接合されている。

(もっと読む)

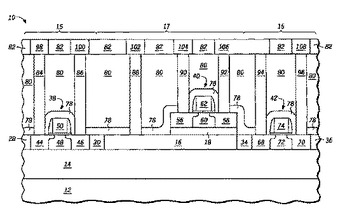

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

窒素化合物含有半導体装置

【課題】 シリコン基板上に形成された窒素化合物含有半導体層を含むヘテロ構造を備え、数百V以上の高耐圧を有する窒素化合物含有半導体装置を提供する。

【解決手段】 本発明の実施の一形態に係る窒素化合物含有半導体装置は、シリコン基板と、シリコン基板上に島状に形成されたチャネル層としての第1の窒化アルミニウムガリウム(AlxGa1−xN(0≦x≦1))層と、第1の窒化アルミニウムガリウム層上に形成された第1導電型又はi型のバリア層としての第2の窒化アルミニウムガリウム(AlyGa1−yN(0≦y≦1,x<y))層と、を備えているものである。

(もっと読む)

561 - 580 / 590

[ Back to top ]