Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

461 - 480 / 590

サージ電流保護を伴う半導体デバイスとその製造方法

サージ電流保護を伴う広域バンドギャップ半導体デバイスおよび該デバイスの製造方法を記載する。該デバイスは、高ドーピングn型基板上で成長させた第1のエピタキシャル層をプラズマエッチングして形成される低ドーピングn型領域および第1のエピタキシャル層上に成長させた第2のエピタキシャル層をプラズマエッチングすることにより形成される多数の高ドーピングp型領域を含む。p型領域上およびn型基板の背面にオーミックコンタクトを形成する。n型領域の上面にショットキーコンタクトを形成する。通常の操作条件では、デバイス内の電流はショットキーコンタクトを通って流れる。しかし該デバイスは、p型領域からの少数キャリアの注入によって引き起こされる伝導性変調による非常に高い電流密度に耐えることができる。 (もっと読む)

半導体素子、半導体装置及びそれらの製造方法

【課題】チャネル領域の電位に対するゲート電極の制御性を向上させ、且つ電流駆動力が高くすることを可能にする。

【解決手段】半導体基板1に形成された、特定の導電型の不純物を含む半導体領域3と、半導体領域中に相互に向かい合う様に形成され、金属または金属と半導体領域をなす半導体との化合物を含むソースおよびドレイン領域4a、4bと、ソースおよびドレイン領域と、ソース領域とドレイン領域との間の半導体領域を覆うとともにソースおよびドレイン領域のそれぞれの一部を覆うように形成された絶縁膜5と、絶縁膜上に形成されたゲート電極6と、を有し、ソースおよびドレイン領域間の半導体領域の少なくとも一部の領域上に於ける絶縁膜とゲート電極との界面は、ソースおよびドレイン領域と半導体領域との接合部の上に於ける絶縁膜とゲート電極との界面よりも半導体領域側に存在する。

(もっと読む)

高効率および/または高電力密度のワイドバンドギャップトランジスタ

少なくとも4GHzの周波数で動作する場合に、40W/mm以上の電力密度を持つ電界効果トランジスタを提供する。135Vのドレイン電圧で、少なくとも40W/mmの電力密度を提供することができる。また、28V乃至48Vのドレインバイアスを与え、10GHzで動作させる場合、60%以上のPAEと少なくとも5W/mmの電力密度を有するトランジスタを提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】順方向動作時の特性劣化を改善する。

【解決手段】ヘテロ半導体領域3に接する第1の電極4は、第1の電極4とドリフト領域2の仕事関数差が少なくともヘテロ半導体領域3とドリフト領域2の仕事関数差よりも大きくなるように選択された金属材料により形成されている。これにより、ヘテロ半導体領域3とドリフト領域2のヘテロ接合部の障壁高さよりも高い接合となるために、漏れ電流が生じず、本来のヘテロ接合が示すIV波形を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】リセス量の制御が容易で,かつリセス時にダメージを受けにくい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置が,半導体基板上に配置され,開口を有し,かつSiおよびGeを含む層と,この開口に対応して配置されるゲートとを有する。

(もっと読む)

半導体装置

【課題】 本発明の目的はビルトイン電圧の低減を図り得る半導体装置を提供する。

【解決手段】 第1導電型の半導体基板20の一方の面にアノードのための電極30と、前記半導体基板の他方の面にカソードのための電極40と、半導体基板の一方の面層に所定の間隔で高濃度の第2導電型のチャネル制御領域23とを備え、該各チャネル制御領域に前記アノード電極が電気的に接続された半導体装置において、前記一方の面層において前記各チャネル制御領域間に低濃度の第1導電型のチャネル領域22と、前記第1導電型のチャネル領域および前記アノード電極間に高濃度の第1導電型のオーミック接触領域24とを備える。

(もっと読む)

電力用半導体素子、その製造方法及びその駆動方法

【課題】大電流化が可能な電力用半導体素子、その製造方法及びその駆動方法を提供する。

【解決手段】半導体装置1において、半導体層2内にストライプ状のゲート電極6を設け、半導体層2上に層間絶縁膜11を設ける。そして、層間絶縁膜11を貫通するように、ゲート電極6と同じ方向に延びるエミッタプラグ12及びゲートプラグ13を設ける。エミッタプラグ12は、N型層4を貫通させてP型層3に接続し、ゲートプラグ13は、ゲート電極6内に埋め込み、その長手方向に沿ってゲート電極6に接続する。また、絶縁膜11上にエミッタパッド14及びゲートパッド15を設け、エミッタプラグ12をエミッタパッド14に接続し、ゲートプラグ13をその長手方向の一端部においてゲートパッド15に接続する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 自己整合的に基板のコンタクト部をユニバーサルコンタクトホール内に形成することができる半導体装置の製造方法及びこの製造方法により形成された半導体装置を提供する。

【解決手段】 層間絶縁膜9にソース領域3が露出されたユニバーサルコンタクトホール7を開口し、ユニバーサルコンタクトホール7から半導体基板100に第1導電型(P型)不純物を注入してユニバーサルコンタクトホール7の底面中央に露出するソース領域3を基板領域と同じ導電型の第1導電型領域5にする。ユニバーサルコンタクト13はユニバーサルコンタクトホール7底面周縁部に露出するソース領域3に電気的に接続されている。基板領域とソース領域のコンタクトの位置関係が一定となりソース領域における電流の不均衡が解消される。

(もっと読む)

集積化ショットキーダイオードに設けられた高密度トレンチとその製造方法

モノリシックICのFET及びショットキーダイオードは第1導電型の第1シリコン領域内に終端する一組のトレンチを含む。第1導電型の第2シリコン領域によって離間された第2導電型の2つの本体領域が、一組のトレンチの間に設けられている。第1導電型のソース領域は本体領域の各々の上に設けられている。接触開口部は一組のトレンチの間においてソース領域よりも下方の深度にまで拡がっている。相互接続層は接触開口部を充填して、ソース領域及び第2シリコン領域と電気的に接触している。相互接続層が第2シリコン領域と電気的に接触する位置において、ショットキー接触が形成されている。  (もっと読む)

(もっと読む)

SiC基板の製造方法及びSiC基板並びに半導体装置

【課題】SiC基板の製造方法及びSiC基板並びに半導体装置において、マイクロパイプだけでなく基底面内転位及び積層欠陥も低減すること。

【解決手段】マイクロパイプを有するSiC単結晶基板1上に、SiCエピタキシャル成長層2を化学的気相成長させるSiC基板の製造方法であって、SiC単結晶基板1の表面近傍又はSiCエピタキシャル成長層2の中間領域に、ブリスタリングが生じない条件で水素又は希ガス元素のイオン注入を行う工程を備えている。

(もっと読む)

半導体装置

【課題】従来よりも高い遮断性能と高温に強い特性を有する半導体装置(スイッチ素子:いわゆるトランジスタ)を提供する。

【解決手段】第一導電型の炭化珪素半導体基体100の上に形成した第一導電型のエピタキシャル領域2と、エピタキシャル領域2とはバンドギャップが異なり、かつエピタキシャル領域2とヘテロ接合する第二導電型の多結晶シリコン領域3と、ヘテロ接合部の一部に接するようにゲート絶縁膜9を介して形成されたゲート電極8とを有する半導体装置であって、前記ヘテロ接合部に逆バイアスを印加したときに、多結晶シリコン領域3の一部は空乏化しないように、多結晶シリコン領域3の不純物濃度と厚さを設定した半導体装置。順方向はショットキー接合ダイオードと同等の特性が得られ、遮断時には多結晶シリコン領域3側からの伝導電子の供給元を抑えられるため、ヘテロ接合界面のヘテロ障壁を介した漏れ電流を大幅に低減できる。

(もっと読む)

炭化ケイ素半導体装置の製造方法および炭化ケイ素半導体装置

【課題】オーミックコンタクト抵抗が低減できるようなオーミックコンタクト形成のためのアニール処理を施した、炭化ケイ素(000-1)面上に絶縁膜を有する半導体装置の製造方法および半導体装置を提供すること。

【解決手段】炭化ケイ素半導体の(000-1)面8上に、少なくとも酸素と水分を含むガス中で熱酸化し前記炭化ケイ素半導体の(000-1)面8上に接するように絶縁膜18を形成する工程と、絶縁膜18の一部を除去し開口部を形成する工程と、開口部の少なくとも一部にコンタクトメタル20を堆積する工程と、熱処理によりコンタクトメタル20と炭化ケイ素の反応層21を形成する工程とを有する炭化ケイ素半導体装置の製造方法において、前記熱処理を不活性ガスと水素の混合ガス中にて実施することを特徴とする炭化ケイ素半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】 本発明の目的はパッケージサイズの低減化を図り得る半導体装置を提供する。

【解決手段】 半導体基板1の一方の面に備えた第1電極3への逆方向電圧の印加によって生じる電界集中を空乏層の形成で緩和するためのガードリングを前記一方の面に備えた半導体装置10において、ガードリングは、空乏層を前記半導体基板の他方の面に誘因するためのコンタクト領域7と、誘因された空乏層を前記他方の面において展開するための展開領域8とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】P+層を形成する時にステッパーマスクを用いることなく、約2.0μmの幅を有するP+層を、約2.5μmの幅を有するP−層の外縁よりも内側に配置する

【解決手段】P−層5上にP+層7を配置する工程を含む半導体装置の製造方法において、P−層5を形成する時に用いられた酸化膜3の開口3aと同じものをP+層7を形成する時に用い、P−層5を形成するための熱処理よりも、P+層7を形成するための熱処理を弱くした。好ましくは、P−層5を形成する時に用いられた酸化膜3の開口3aに形成された新たな酸化膜3bに対してリンデポジションを行う工程を、P+層7を形成する工程の前に設けた。

(もっと読む)

窒化物系半導体装置

【課題】高い貫通転位密度を有するコア部の配置の影響を低減することができ素子面積を大きくできる構造のダイオードを提供する。

【解決手段】第1導電型窒化ガリウム系半導体層15の第1及び第3の領域15a、15cはそれぞれ貫通転位密度D1より小さい貫通転位密度D11、D13を有する。第2の領域15bは貫通転位密度D1より大きい貫通転位密度D12を有する。電極17a、17bは第1および第3の領域15a、15cにショットキ接合を成す。保護絶縁膜18は、電極17a、17b上にそれぞれ位置する第1および第2の開口を有すると共に、電極17a、17bのエッジを覆う。絶縁層19は、第2の領域15bと保護絶縁膜18との間に設けられている。配線導体20は、保護絶縁膜18上に設けられると共に、保護絶縁膜18の第1および第2の開口を通して電極17a、17bに接続される。

(もっと読む)

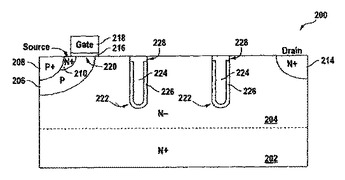

セルフバイアス電極を有するラテラルパワーデバイス

第1導電タイプのドリフト領域及び当該ドリフト領域内の第2導電タイプのウェル領域を含み、当該ウェル領域及び当該ドリフト領域の間でpn接合を形成する半導体パワートランジスタである。第1導電タイプの第1ハイドープシリコン領域が当該ウェル領域にありかつ第2ハイドープシリコン領域が当該ドリフト領域にある。当該第2ハイドープシリコン領域が当該ウェル領域から横方向に離間されており、導電状態において当該と連ジスたがバイアスするときに電流が当該ドリフト領域を介して第1と第2ハイドープシリコン領域の間を横方向に流れる。当該ドリフト領域内に当該電流の流れに対して垂直方向に伸長する複数のトレンチの各々が当該トレンチ側壁の少なくとも一部及び導電性電極の少なくとも1つをライニングする誘電層を含む。  (もっと読む)

(もっと読む)

炭化珪素半導体装置

【課題】 素子破壊を防止し得る炭化珪素半導体装置を提供する。

【解決手段】 本発明の炭化珪素半導体装置は、第1導電型の炭化珪素基板20と、該炭化珪素基板の一方の面にアノードのための電極30と、炭化珪素基板の他方の面にカソードのための電極40と、炭化珪素基板の一方の面側の層の所定位置で所定の間隔を有してアノード電極と電気的なコンタクトを得る第2導電型の炭化珪素領域50と、炭化珪素基板の他方の面側の層において、一方の面層からの空乏層のリーチスルーを誘因すべく、第2導電型の領域に対向する位置でカソード電極と電気的なコンタクトを得る第1導電型の高濃度領域をリーチスルー誘因領域60として備える。

(もっと読む)

半導体装置

【課題】電流破壊を起こしにくい半導体装置を提供すること。

【解決手段】N+型炭化珪素基板1上にN−型炭化珪素エピタキシャル領域2が積層され、N−型炭化珪素エピタキシャル領域2中の所定領域にはP型の電界緩和領域10が形成され、エピタキシャル領域2表面および電界緩和領域10表面の所定領域上にN型多結晶シリコン領域4およびP型多結晶シリコン領域3が形成され、エピタキシャル領域2とN型多結晶シリコン領域4との界面に隣接しゲート絶縁膜5を介してゲート電極6が配置され、N型多結晶シリコン領域4およびP型多結晶シリコン領域3にはソース電極8が接続し、N+型炭化珪素基板1の裏面にはドレイン電極9が形成されている半導体装置において、電界緩和領域10とソース電極8とがP型多結晶シリコン領域3を介してオーミック接続していることを特徴とする半導体装置を構成する。

(もっと読む)

半導体装置

【課題】 キャリア移動度を向上しつつトランジスタ特性の劣化を抑制した半導体装置を提供する。

【解決手段】 シリコン基板100上にゲート絶縁膜103を介してゲート電極104を有し、ゲート電極104の側面に第一の側壁絶縁膜105を有し、第一の側壁絶縁膜105の側面に第二の側壁絶縁膜106を有し、第二の側壁絶縁膜106の下方に第一のソース/ドレイン層108を有し、第二の側壁絶縁膜106の外側に第一のソース/ドレイン層108と接し、かつシリコンゲルマニウムを含有し、表層部にゲルマニウム層110を有する第二のソース/ドレイン層111を有し、第二のソース/ドレイン層111のゲルマニウム層110上にジャーマナイド層113を有する。

(もっと読む)

光起電力型紫外線センサ

【課題】複雑な装置等を必要とせず、可視光に感度がなく、且つ、応答速度の速い紫外線センサを提供すること。

【解決手段】紫外線センサは、光起電力型のものであり、酸化亜鉛単結晶基板11と、その+c面上に形成されたショットキー電極12からなる紫外線受光部を備える。ショットキー電極12は、紫外線透過性を呈するような膜厚を有しており、例えば、Pt,Ru,Pd,Au,Ni,Ir,Os,Re,Rh,Te又はWからなる層を少なくとも一層備えたものを用いることができる。

(もっと読む)

461 - 480 / 590

[ Back to top ]