Fターム[4M104GG12]の内容

Fターム[4M104GG12]に分類される特許

101 - 120 / 697

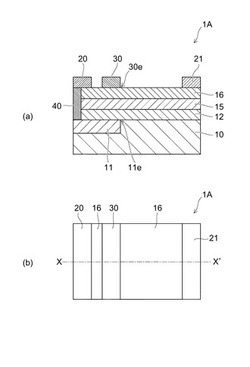

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体エピタキシャル結晶基板及びその製造方法

【課題】高性能の窒化ガリウム系トランジスタを製造するための、誘電体膜付の半導体エ

ピタキシャル結晶基板を提供すること。

【解決手段】下地基板1上にエピタキシャル法によって、バッファ層2、チャネル層3、

及び電子供給層4から成る窒化ガリウム半導体結晶層を形成した後、エピタキシャル成長

炉内で連続してAlNを電子供給層4上に誘電体膜の前駆体として積層し、しかる後、積

層した前駆体に対して酸化処理を施すことによって誘電体膜5を形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性が均一であって、歩留りの高い半導体装置の製造方法を提供する。

【解決手段】第1の半導体層12及び第2の半導体層13が順次形成されている半導体層の表面にレジストパターンを形成する工程と、前記レジストパターンの開口領域における前記第2の半導体層の一部または全部をドライエッチングにより除去しゲートリセス22を形成する工程と、前記レジストパターンを除去した後、ゲートリセスの底面及び側面に付着しているドライエッチング残渣23を除去する工程と、前記ドライエッチング残渣を除去した後、前記ゲートリセスの底面、側面及び前記半導体層上に絶縁膜31を形成する工程と、前記ゲートリセスが形成されている領域に前記絶縁膜を介しゲート電極を形成する工程と、前記半導体層上にソース電極及びドレイン電極を形成する工程と、を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層の表面におけるダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】電極溝2Cの内壁面を含む化合物半導体層2の表面は、電極溝2Cを形成する際のドライエッチングによるエッチング残渣物12a及び変質物12bが除去されて、化合物半導体がフッ素(F)で終端されており、この電極溝2Cをゲート絶縁膜6を介してゲートメタルで埋め込み、或いは電極溝2Cを直接的にゲートメタルで埋め込んで、ゲート電極7が形成される。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

化合物半導体装置

【課題】電流コラプス現象が抑制され、且つフィールドプレート電極による電界集中を緩和する効果の低下が抑制された化合物半導体装置を提供する。

【解決手段】III族窒化物半導体層と、III族窒化物半導体層上に配置された絶縁膜7と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたドレイン電極4と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたソース電極3と、ドレイン電極とソース電極間においてIII族窒化物半導体層の上面から膜厚方向に第2の距離T3の位置に絶縁膜を介して配置されたゲート電極5と、ドレイン電極とゲート電極間においてIII族窒化物半導体層の上面から膜厚方向に第1の距離T1より短い第2の距離T2の位置に絶縁膜を介して配置されたフィールドプレート電極6とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

半導体装置

【課題】オーミック電極のコンタクト抵抗を低減する。

【解決手段】半導体装置は、第1の窒化物半導体層13上に形成され第1の窒化物半導体層13よりバンドギャップが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14を貫通して第1の窒化物半導体層13の一部を除去する形状の凹部と、凹部を埋め込む電極17とを備える。第1の窒化物半導体層13の第2の窒化物半導体層14との界面直下に2次元電子ガス層13aを有する。電極17と第2の窒化物半導体層14とは第1のコンタクト面16aにて接する。電極17と2次元電子ガス層13aの部分とは、第1のコンタクト面16aの下に接続された第2のコンタクト面16bにて接する。第1のコンタクト面16aは凹部の幅が下から上に広くなる形状である。接続箇所において、第2のコンタクト面16bは、第1のコンタクト面16aよりも第1の窒化物半導体層13の上面に対して急峻である。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置において、高温且つ高電圧下のスイッチング時においても電流コラプスによるオン抵抗の増大が生じないようにする。

【解決手段】基板1上には、バッファ層2、GaNからなるチャネル層3及びアンドープAlGaNからなるバリア層4が順次形成されている。チャネル層3は、該チャネル層3の下部にp型不純物層3aを有し、その上にアンドープ層3bを有している。バリア層4及びチャネル層3の端部が除去されており、露出したバリア層4及びチャネル層3の側面と接するように、それぞれソース電極5及びドレイン電極6が設けられている。バリア層4上におけるソース電極5とドレイン電極6との間の領域にはゲート電極7が設けられている。

(もっと読む)

窒化物半導体装置

【課題】高周波数動作が可能で、ゲートリーク電流や電流コラプスを抑制できる窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極上に絶縁膜9を介してゲート電極7を配置する。さらに、ソース電極とドレイン電極との間の電子供給層表面を珪素膜11で被覆する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】制御性の良い製造方法のみで形成することができる高周波数動作が可能なノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層4とショットキー接触する浮遊電極8を配置し、この浮遊電極8上に絶縁膜を介してゲート電極7を配置する。さらに、ソース電極5とドレイン電極6との間の電子供給層表面を珪素膜11で被覆する。そして、ゲート電極7に正バイアス印加し、浮遊電極8に電子を蓄積される。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】

本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】

化合物半導体装置は、基板と、前記基板上に形成された窒化ガリウム系半導体と、前記窒化ガリウム系半導体上に形成された窒化ガリウム系保護層と、前記窒化ガリウム系保護層上にタンタルとアルミニウムが任意の順に積層されてなるオーミック電極とを備え、前記オーミック電極が形成された箇所の前記窒化ガリウム系保護層の膜厚は、前記オーミック電極が形成されていない箇所の前記窒化ガリウム系保護層の膜厚よりも薄い。

(もっと読む)

101 - 120 / 697

[ Back to top ]