Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

121 - 140 / 219

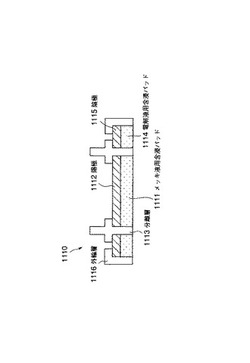

メッキ方法

【課題】ダマシンプロセスに適した溝や孔への優先的なメッキ膜形成を実現する。

【解決手段】半導体基板と少なくとも前記半導体基板に形成された導電層を有する被処理基板と、メッキ液を含む第1の含浸体1111及び電解液を含む第2の含浸体1114が設けられたメッキヘッド1110とを用意し、第1の含浸体1111に陽極1112の電位を与えると共に、第2の含浸体1114に陰極1115の電位を与えた状態で、第1及び第2の含浸体1111,1114を導電層に対向させ、導電層の少なくとも一部にメッキ層を形成するために、メッキヘッド1110を導電層に対して相対的に移動させる。

(もっと読む)

半導体装置の作製方法

【課題】材料や形成されたパターンが異なる複数の層が積層された構造の半導体装置において、CMP法による研磨処理やSOG膜成膜による平坦化処理を行わなくても平坦化でき、さらに基板材料を選ばず、簡便に平坦化を行う方法を提供することを課題とする

【解決手段】異なる層が複数積層されて形成された半導体装置において、絶縁膜に開口部を形成し、その開口部内に配線(電極)または半導体層を形成することにより、絶縁膜および配線(電極)または半導体層上に形成される絶縁膜に対してCMP法による研磨処理またはSOG膜の成膜による平坦化を行わなくても表面の平坦化を行うことができる。

(もっと読む)

レーザー照射による電気伝導性銅パターン層の形成方法

【課題】

【解決手段】本発明は銅配線層、銅電極層などのような電気伝導性銅パターン層の形成方法に関し、(ステップ1)銅粒子、酸化銅粒子及びこれらの混合物からなる群より選択された銅系粒子の分散液を用意する段階;(ステップ2)前記銅系粒子の分散液を基材に所定形状で印刷または充填して銅系粒子パターン層を形成する段階;及び(ステップ3)前記銅系粒子パターン層にレーザーを照射し、前記銅系粒子パターン層に含まれた銅系粒子を焼成しながら相互連結させる段階を含む。本発明による電気伝導性銅パターン層の形成方法は、レーザーを用いて短時間で強いエネルギーで銅系粒子パターン層を焼成することで、空気中でも酸化が殆ど進まない銅パターン層が得られるため、電気伝導性の良好な銅パターン層を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

太陽電池の製造方法および太陽電池ならびに印刷用スクリーン

【課題】表面電極の収縮応力を低減してマイクロクラック等の発生が抑制される太陽電池の製造方法、太陽電池および印刷用スクリーンを提供する。

【解決手段】印刷用スクリーン2には、バスバー電極のパターンに対応した露出したメッシュのスクリーンの領域S1における所定の領域に第2遮蔽部5が形成されている。銀ペーストをスキージによって押し広げることで銀ペーストパターンが印刷され、印刷用スクリーンを取外すと、第2遮蔽部5によって銀ペーストパターンが印刷されなかった領域に、銀ペーストの粘性によって銀ペーストがだれて流れ込み、銀ペーストパターンの幅方向の端部の厚みがより薄くなる。これにより、銀ペーストパターンの幅方向の端部と中央付近とで厚みの差が小さくなって、バスバー電極の収縮応力が大幅に低減される。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの電極形成時に、MOSトランジスタを覆う層間絶縁膜上のポリシリコン膜のエッチング残りの発生を低減可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)バイポーラトランジスタ5とMOSトランジスタ6a、6bとが形成された半導体基板51を覆うように層間絶縁膜65を形成する工程と、(b)層間絶縁膜65を平坦化する工程と、(c)層間絶縁膜66におけるバイポーラトランジスタ5の電極70用の開口部68を形成する工程と、(d)層間絶縁膜66及び開口部68を覆うようにポリシリコン膜69を形成する工程と、(e)層間絶縁膜66上のポリシリコン膜69をエッチバックして、開口部68内に電極70を形成する工程とを具備する。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体装置の製造方法

【課題】 集積度が低下することを最大限抑制しつつ、必要に応じて大きい電流容量の確保を可能にしたコンタクトプラグを備えた半導体装置の製造方法を提供する。

【解決手段】 半導体基板1上にソース・ドレイン領域8を形成後、層間絶縁膜10を堆積し、ソース・ドレイン領域8の上面が露出するようにコンタクトホールを開口する。このとき、比較的小電流容量で機能を奏するロジック素子形成領域上面においては最小加工寸法で規定される程度の小さい孔径で開口する一方、大電流容量を必要とする保護素子形成領域上面においては、第1孔径よりも大きい第2孔径で開口する。その後、これらのコンタクトホールを完全に充填するように、コンタクトプラグ材料膜13を層間絶縁膜10の堆積膜厚以上成膜する。その後、コンタクトプラグ材料膜13に対して平坦化処理を行った後、配線層を形成する。

(もっと読む)

絶縁膜の作製方法及び半導体装置の作製方法

【課題】非感光性のシロキサン樹脂を用いて、ウェットエッチング法で所望の形状に形成された絶縁膜を形成することができる、絶縁膜の作製方法を提供する。

【解決手段】有機溶媒中にシロキサン樹脂またはシロキサン系材料を有する懸濁液を用いて薄膜を形成し、薄膜に第1の加熱処理を施し、第1の加熱処理後の薄膜上にマスクを形成し、有機溶媒を用いてウェットエッチングすることで、第1の加熱処理後の薄膜の形状を加工し、加工された薄膜に第2の加熱処理を施す。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、ゲート電極のトリミングを良好に実施できるように、また、レジストトリミングを行ってもレジスト倒れやレジスト変形が発生しないように、更に、従来のトリミングがプラズマエッチングで実施されていることに起因する問題を解消し、更にまた、ゲート電極のトリミングに関連してサイドウォールの形成時にSTI部が過剰に損傷されないようにしようとする。

【解決手段】金属を含む材料である金属シリサイド或いは金属単体から成るゲート電極をもつ半導体装置を作製する工程に於いて、ゲート電極14Gのエッチング後にゲート部の表面を酸化させ、ゲート部を有機酸を含むガス状物質に曝露すると共に加熱して金属と有機酸との反応生成物を揮発させてゲート電極14Gのトリミングを行う。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン型ゲートあるいはリプレース型ゲートを有する半導体装置において、ゲートパターン密度の偏りを小さくし、ダミーゲートの上面を露出させるCMP工程において、ディッシングが発生しないようにする。

【解決手段】ダマシン型ゲートあるいはリプレース型ゲートを有する半導体装置において、ゲート形成位置以外の位置14に、ダミーゲート12aを追加して配置することにより、ゲートパターン密度の偏りを小さくする。あるいはダミーゲート12aの代わりにインターフェーストランジスタ、あるいはアナログ回路用容量の電極を配置することにより、ゲートパターン密度の偏りを小さくする。

(もっと読む)

LEDエピウエハに用いるランドパッドの製造工程及び構造

【課題】ランドパッドとエピウエハの間の付着力を確実にし、ランドパッド表面粗度過大の問題を改善するLEDエピウエハに用いるランドパッドの製造工程及び構造を提供する。

【解決手段】LEDエピウエハに用いるランドパッドの製造工程及び構造は、先ずエピウエハ表面に対して界面結合力を高める手段、次にエピウエハ表面に金属沈殿手段、先ずエピウエハの表面にプラズマ処理を行い、ランドパッドとエピウエハの間の付着力を確実にする。この他、更に電気メッキ条件を制御して、電気メッキ沈殿の粒を極粒にし、ランドパッド表面粗度過大の問題を改善し、ランドパッドと電線接合の接着強度を高める。また第一金属層及び第二金属層の間に導電粘着層を沈殿させ、第一金属層及び第二金属層の界面結合力を高める。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETおよびPMOSFETに適した組成のフルシリサイド相を、少ない工程数で、容易に得ることが可能な製造方法を提供すること。

【解決手段】基板1上に、ゲート絶縁膜2を介して前記NMOSFET用第1ゲート電極、およびPMOSFET用第2ゲート電極を形成する工程と、前記ゲート電極を覆う層間膜8を形成する工程と、前記層間膜8を平坦化し、前記第1、第2ゲート電極のシリコン層3を露出する工程と、前記第2ゲート電極の上部を選択的に除去する工程と、前記第2のゲート電極および第1のゲート電極のシリコン層3上に金属膜11を形成し、シリサイド化熱処理を行う工程と、熱処理工程後に未反応の金属膜を除去する工程と、を含み、第2のゲート電極上部を選択的に除去する工程の前に、前記第1および第2のゲート電極の各シリコン層3に、シリサイド相の組成制御のための不純物を同時に導入する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極上に積層するポリサイド層、バリアメタル層、メタル層、絶縁膜ハードマスクの膜剥がれを抑制する効果を発揮させた半導体装置およびその製造方法を提供することを目的とする。

【解決手段】トレンチゲート型のMOSトランジスタTr1、Tr2を備えた半導体装置の製造方法であって、半導体基板1の表面にトレンチ12、13を形成してからゲート絶縁膜20を形成する工程と、前記半導体基板1上にゲート電極8用のポリシリコン層を形成する工程と、前記トレンチ12、13上に位置する前記ポリシリコン層の上面に生じた凹部を除くための水素雰囲気中アニールを行なう工程と、前記ポリシリコン層を選択的に除去することによりトレンチ12、13上のポリシリコン層を残してこれをゲート電極8とする工程とを具備してなることを特徴とする半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造装置

【課題】配線抵抗のばらつきが抑制された高品質の半導体装置を安価に作製することが可能な半導体装置の製造装置を得ること。

【解決手段】化学研磨液を用いて化学的機械的研磨を行う研磨パッドと、前記研磨パッドを設置する回転可能な定盤と、表面層に凹部が形成された基板の前記凹部の形成面を前記研磨パッドの表面に対向させて保持する保持手段と、前記保持手段により保持された前記基板を前記研磨パッドに対して押圧して前記基板の前記凹部の形成面を前記研磨パッドの表面に当接させる押圧手段と、前記基板の前記凹部の形成面と前記研磨パッドとの当接面にめっき液を供給するめっき液供給手段と、前記基板および前記定盤間にめっき電圧を印加する電圧印加手段と、前記研磨パッドの表面に前記化学研磨液を供給する研磨液供給手段と、を備え、前記基板の表面に対するめっき膜の形成と、前記基板の表面の化学的機械的研磨と、を行うことが可能である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 上層配線が半導体層に接続された薄膜トランジスタにおいて、コンタクトホール形成部の層間絶縁膜の厚さを薄くし、均一なコンタクトホールの形成を可能とする。

【解決手段】 多結晶半導体層3を活性層とし、層間絶縁膜6に形成されたコンタクトホール7を介して配線が多結晶半導体層3に接続されている。多結晶半導体層3に接続される配線は、複層配線のうちの2層目以上の上層配線(第2配線8)である。コンタクトホール7に対応する位置に所定の厚さを有する下地パターン10が形成され、この下地パターン10上に多結晶半導体層3の第2配線8との接続部分(ソース領域3a及びドレイン領域3b)が形成されている。

(もっと読む)

ポリシリコン層及び層構造のパターニング方法

【課題】金属或いは金属シリサイド層を多結晶シリコン層の上に含む層構造のパターニング方法において、ドーピング物質が全析出面にわたって均質に分布され、その表面性質及び隣接の層との接着性ができるだけ良くなる方法を提供する。さらに、高い選択性と、大きな均質性とをもって、かつエッチングされる全ての層にわたって真っ直ぐにエッチングされた側面部を形成するようにパターニングする方法を提供する。

【解決手段】ドーピング化合物がプロセスガスとしてポリシリコンの化学気相蒸着の際に添加され、そのプロセスガスへの供給が気相蒸着の終了近くで停止され、その結果非ドープのシリコンからなる境界層が析出される。このパターニング法は、少なくとも3段階のエッチングプロセスを含み、第一の段階ではフッ素を含むガスが、第二の段階では塩素を含むガスが、第三の段階では臭素を含むガスがエッチングのために使用される。

(もっと読む)

窒化物半導体装置

【課題】電極パッドの面積を確保しつつ、装置面積が小さい窒化物半導体装置を実現でき電極パッドの面積を確保しつつ、装置面積が小さい窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板11と、基板11の主面の上に形成され、主面と平行な方向に電子が走行するチャネル領域を有する窒化物半導体層13と、窒化物半導体層13における活性領域30の上に互いに間隔をおいて形成された第1の電極18及び第2の電極17とを備えている。窒化物半導体層13の上には、第1の電極18を露出する開口部を有し且つ上面が平坦化された層間絶縁膜23が形成され、層間絶縁膜23における活性領域30の上側の領域には、開口部から露出した第1の電極18と電気的に接続された第1の電極パッド25が形成されている。

(もっと読む)

TFTアレイ構造及びその製造方法

【課題】TFTアレイ基板及びその製造方法を提供する。

【解決手段】透明ガラス基板11と、上方に順次ゲート絶縁層13、半導体層14、オーミック接触層15が被覆しているゲートライン12b及びゲートライン12bと一体となるゲート電極12aと、ゲートライン12b及びゲート電極12a、ゲート絶縁層13、半導体層14、オーミック接触層15の両側に形成された絶縁層16と、オーミック接触層15に形成され、半導体層14の中間位置の上方でオーミック接触層15を分断する分断溝15aと、絶縁層16及びオーミック接触層15の上方に形成されたデータライン及び第1、第2のソース・ドレイン電極と、を備えるTFTアレイ基板であり、該TFTアレイ基板はスリットフォトリソグラフィー処理を使用しない4回のフォトリソグラフィー処理により製造できる。

(もっと読む)

平坦化された金属高密度パワーMOSFET

パワーMOSFETの製造方法。当該方法は、パワーMOSFETの複数の層を加工して上部表面の活性領域を形成すること、当該活性領域に化学機械研磨プロセスを施して実質的に平坦な表面を形成することを含む。次に、金属化堆積プロセスが実質的に平坦な表面上に実施され、パワーMOSFETの製造がその後に完了する。 (もっと読む)

121 - 140 / 219

[ Back to top ]