Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

201 - 219 / 219

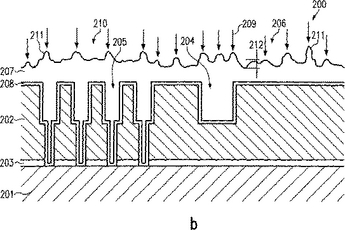

後続の化学機械研磨(CMP:ChemicalMechanicalPolishing)プロセスのプロセス均一性が向上するようにパターン誘電層上に銅を電気メッキするための方法

直径の小さなビアと直径の大きなトレンチ205を含む誘電層に金属をメッキする新しい方法で、例えば誘電層203の少なくとも非パターン領域におけるメッキ槽においてレベラーの量を低減することによって表面粗度が生成され、後続の化学機械研磨(CMP)における材料除去の均一性を向上させる。  (もっと読む)

(もっと読む)

有機金属化学蒸着用有機ニッケル化合物及び該化合物を用いたニッケル含有膜の製造方法

【課題】高い平坦性で膜を形成することができる。不純物含有量の少ない膜を形成することができる。

【解決手段】本発明の有機ニッケル化合物は、Ni(R-Cp)2で表される有機ニッケル化合物である。但し、式中のCpはシクロペンタジエニル基を示し、Rは水素又は炭素数が1〜4の直鎖若しくは分岐状アルキル基をそれぞれ示す。また、本発明のニッケル含有膜の製造方法は、上記有機ニッケル化合物を用いてMOCVD法によりニッケル含有膜を作製することを特徴とする。

(もっと読む)

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】 パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、上記パターン上を含む領域を平坦にするバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】 機能液により形成するパターンに対応した凹部が設けられた隔壁構造体であって、第1パターンに対応して隔壁34に設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して隔壁34に設けられた第2凹部56と、を含み、第2凹部56の底面の高さが、第1凹部55の底面の高さよりも高く設けられていることを特徴とする。

(もっと読む)

エッチバック方法、それを用いた無機偏光子製造方法及びそれらの方法を実現するエッチング停止制御装置、並びに製造される無機偏光子

【課題】

微細な凹部パターンに金属が埋め込まれ堆積されたパターン表面の平坦化と、パターン高さを精度よくエッチバックにより制御する。

【解決手段】

表面に微細な格子パターン12が形成されている基板10の表面上に格子パターン12を被ってアルミニウム膜14を堆積し、その上にレジスト層16を塗布し、レジスト層16には格子パターン12が形成されている領域以外の領域に開口18を設ける。レジスト層16とアルミニウム膜14をエッチバックし、SiFから発生するプラズマ強度の微分値が所定の値を越えた時点から所定の設定時間(制御時間)後にエッチングを停止する。

(もっと読む)

半導体装置、およびその半導体装置を用いた電力変換器、駆動用インバータ、汎用インバータ、大電力高周波通信機器

イオン注入で形成されたP型、N型の不純物半導体領域を有する炭化珪素半導体基板を用いた半導体装置において炭化珪素半導体基板表面の凹凸を小さくすることにより、最終的に半導体装置の電気特性を向上できるようにする。この発明の半導体装置は、(000−1)面あるいは(000−1)面からある角度傾いた面を最表層面として有する炭化珪素半導体領域1,2に、P型半導体領域3およびN型半導体領域の少なくとも一方がイオン注入により選択的に形成され、その最表層面に金属電極が形成され、その金属電極に電圧を印加することにより最表層面に垂直な方向に流れる電流の方向を制御するショットキー・バリア・ダイオード、若しくはPN型ダイオードである。  (もっと読む)

(もっと読む)

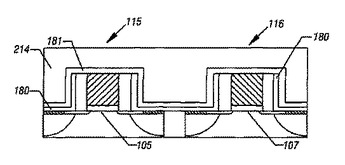

半導体デバイスの製造方法およびこのような方法で得られる半導体デバイス

本発明は、半導体ボディ(1)と基板(2)とを有し、少なくとも1つの半導体素子(3)を備える半導体デバイス(10)の製造に関し、この半導体デバイスは、少なくとも1つの接続領域(4)と、接続領域に接続された、上に位置する帯状の接続導体(5)と、を備え、この接続領域および接続導体は、両方とも誘電体に凹設され、第1材料の誘電体領域(6)が、半導体ボディ(1)の、接続領域(4)が形成される位置に設けられ、その後、誘電体領域(6)は、第1材料とは異なる第2材料の誘電体層(7)で被覆され、この誘電体層には、帯状の接続導体(5)が形成される位置に帯状の凹部(7A)が設けられ、この凹部は、誘電体領域(6)に重なり、かつ前記誘電体領域まで延び、凹部(7A)の形成と誘電体領域(6)の除去の後、接続領域(4)が、誘電体領域(6)の除去により作られた空間(6A)に導電性材料を堆積することにより形成され、接続導体(5)が、凹部(7A)に導電性材料を堆積することにより形成される。本発明によると、第1材料には、有機材料が用いられ、第2材料には、この有機材料より高い分解温度を有する材料が用いられ、誘電体領域(6)は、有機材料の分解温度より高く、第2材料の分解温度よりは低い温度で加熱することにより除去される。本発明に係る方法は、非常にシンプルであり、第2材料を任意に選択することにより、得られるデバイス(10)に高い平面性をもたらすことができる。誘電体領域(4)には、好ましくはフォトレジストが用いられ、誘電体層(7)には、好ましくはSILKまたはSOG材料などの液体材料が用いられ、これは、加熱により固体状に変換することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 シリサイド膜を有する半導体装置において配線抵抗を低減し、また配線抵抗のばらつきを低減する。

【解決手段】 コバルトシリサイドあるいはニッケルシリサイドを使う超高速半導体装置において、シリサイド膜形成のためシリコン表面に金属膜を堆積する前に、シリコン表面から自然酸化膜をウェットエッチングプロセスで除去した後、化学酸化膜を形成する。

(もっと読む)

エピタキシャルSiC膜とその製造方法およびSiC半導体デバイス

【課題】表面にステップバンチングがないエピタキシャルSiC膜を提供すること。さらにその膜を用いてリーク電流が低く、MOS界面の移動度が高いデバイスを提供すること。

【解決手段】 六方晶系結晶構造を有するSiC基板のオフカット面上で成長させたエピタキシャルSiC膜であって、前記SiC基板のオフカット面が、(0001)面から0.5°以上10°以下のオフカット角度を有し、前記オフカット面の結晶方向が、前記SiC基板の12種の等価な<21−30>方向([21−30]、[−2−130]、[2−310]、[−23−10]、[12−30]、[−1−230]、[1−320]、[−13−20]、[−3120]、[3−1−20]、[−3210]および[3−2−10]方向)のいずれかの方向から±7.5°以下のうちの1方向を向いていることを特徴とするエピタキシャルSiC膜。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

銅の配線層を形成する方法

【課題】 少なくとも1つの窪みを有する第1領域と、前記少なくとも1つの窪みのアスペクト比とは異なるアスペクト比を有する窪みが複数個並んだ第2領域とを有する半導体構造に、低コストで銅の配線層を形成する方法を提供すること。

【解決手段】 本方法は、線幅の異なる2以上の溝を有する半導体構造に、第1の硫酸濃度を有するめっき液で銅の導電層を形成する第1工程と、前記第1の硫酸濃度より薄い第2の硫酸濃度を有するめっき液で、前記導電層上に更に導電層を積層する第2工程と、前記半導体構造上に成膜された銅の導電層を研磨する研磨工程とを有する。これにより、線幅の異なる2以上の溝を有する半導体構造に、低コストで銅の配線層を形成することができる。

(もっと読む)

固体撮像素子の製造方法

【課題】 単層電極構造の電荷転送電極を形成するに際し、平坦化工程におけるアクティブ領域の膜減りを防止し、均一な膜厚の配線を形成することにより配線抵抗のばらつきを低減する。

【解決手段】 固体撮像素子の製造方法において、ゲート酸化膜の形成された半導体基板表面に、第1の電極、前記光電変換部および前記周辺回路部の第1層配線を構成する第1層導電性膜のパターンを形成する工程と、前記第1の電極の少なくとも側壁に電極間絶縁膜となる絶縁膜を形成する工程と、前記第1の電極および前記電極間絶縁膜の形成された前記半導体基板表面に第2の電極を構成する第2層導電性膜を形成する工程と、前記第1の電極上に突出する前記第2層導電性膜の突出部を除去し、表面を平坦化する工程と、前記アクティブ領域の前記第2層導電性膜をパターニングする工程とを含み、前記平坦化する工程に先立ち、アクティブ領域に除去抑制層を形成する工程を含む。

(もっと読む)

層形成方法、配線基板、電気光学装置、および電子機器

【課題】 下地層の段差を吸収して平坦な面を提供する絶縁層であって、コンタクトホールを有する絶縁層を、インクジェット法で形成すること。

【解決手段】 インクジェット法を用いた層形成方法は、(a)第1レベル面上に位置する第1導電層21の側面が第1絶縁材料31Aで覆われるように、前記第1レベル面上に第1の濃度を有する前記第1絶縁材料31Aを吐出するステップと、(b)吐出された前記第1絶縁材料31Aを活性化または乾燥して、前記第1導電層21に接する第1絶縁層31Bを形成するステップと、(c)前記第1導電層21上と前記第1絶縁層31B上とに、前記第1の濃度よりも高い第2の濃度を有する第2絶縁材料を吐出するステップと、(d)吐出された前記第2絶縁材料を活性化または乾燥して、前記第1導電層21と前記第1絶縁層31Bとを覆う第2絶縁層を形成するステップと、を含んでいる。

(もっと読む)

薄膜トランジスタの製造方法、半導体装置、電気光学装置及び電子機器

【課題】 1度の不純物注入工程によってLDD構造を形成することができる薄膜トランジスタの製造方法等を提供する。

【解決手段】 本発明は、ゲート絶縁膜上に、チャネル長方向において端部から中央部に向けて徐々に膜厚が厚くなる傾斜部を有するゲート電極20を形成する工程を含む薄膜トランジスタうの製造方法を提供する。該ゲート電極20をマスクとしてリンなどの不純物元素のイオン打ち込みを行うことで、最終的には図3(B)に示すようなソース/ドレイン領域としての高濃度のN+型不純物拡散領域22a、低濃度のN-型不純物拡散領域22b、及びチャネル領域24が形成される。

(もっと読む)

固体撮像素子の製造方法および固体撮像素子

【課題】 単層電極構造の電荷転送電極を形成するに際し、第2層導電性膜の平坦化工程に起因する膜減りを防止し、均一な膜厚の電荷転送電極を形成することにより電荷転送効率の改善を図る。

【解決手段】 ゲート酸化膜の形成された半導体基板表面に、第1の電極を構成する第1層導電性膜のパターンを形成する工程と、前記第1の電極の少なくとも側壁に電極間絶縁膜となる絶縁膜を形成する工程と、前記第1の電極および前記電極間絶縁膜の形成された前記半導体基板表面に第2の電極を構成する第2層導電性膜を形成する工程と、少なくとも前記第1の電極上の前記第2層導電性膜を除去し、平坦化する工程とを含み、前記平坦化する工程に先立ち、前記第2層導電性膜の上層の一部に除去抑制層を形成する工程を含む。

(もっと読む)

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

絶縁層及び接続孔の形成方法、配線構造及びその形成方法

【課題】 絶縁層及びヴィア形成において、形成された絶縁層の表面が非常に平滑となり、薄膜素子等を信頼性及び歩留り良く、高い自由度を以って形成でき、さらには微小なヴィア形成が可能である絶縁層及びヴィア(接続孔)の形成方法、及びそれを用いた多層配線基板並びにモジュール基板等の配線構造及びその形成方法を提供する。

【解決手段】 台座20を介してマスク基板21を配置し、この基板21とコア基板1との間に感光性エポキシ樹脂などの感光性絶縁材料3Aを介在させ、これをパターン露光して現像してヴィアホール7を形成する。この現像により、微小なヴィアホール7を形成できると同時に、マスク基板21のコア基板対向面21aによって絶縁材料(従って、絶縁層3)を平坦かつ滑らかな表面に、しかも常に設定された厚みに形成することができる。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

201 - 219 / 219

[ Back to top ]