Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

101 - 120 / 219

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、半導体基体との界面における組成の均一性に優れ、ショットキー接合層との十分に高い密着性が得られるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第一半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第二半導体領域6bと、第一半導体領域1aにオーミック接触するオーミック接合層7と、第二半導体領域6bにショットキー接触するショットキー接合層8とを備え、オーミック接合層7の二乗平均粗さが、20nm以下である半導体装置とする。

(もっと読む)

無電解めっき方法および無電解めっき装置

【課題】触媒付与処理を行った後、配線表面における異状粒状金属の発生及び配線表面のめっき膜のラフネス悪化を防止しつつ、コバルト合金膜等のめっき膜を配線の表面に選択的に形成できるようにする。

【解決手段】絶縁膜に設けた配線用凹部内に金属を埋込んで形成した埋込み配線を有する基板を用意し、基板表面を触媒付与液に接触させて配線表面に触媒を付与し、触媒付与後の基板表面に洗浄液を供給しつつ該表面を物理的に洗浄し、しかる後、基板表面に無電解めっきを行って配線表面にめっき膜を選択的に形成する。

(もっと読む)

メッキ厚算出プログラム、メッキ厚算出装置およびメッキ厚算出方法

【課題】最適なメッキ厚を短時間で算出することを課題とする。

【解決手段】メッキ処理、研磨処理、過研磨処理の順に実行される半導体集積回路の製造処理の中で、過研磨処理により削り取られる導電体の削取導電体厚を過研磨処理時の研磨時間および研磨速度を用いて算出し、研磨処理後の基板上の配線溝以外の箇所に残存することが予想される残存導電体厚が、削取導電体厚以下となるまで、メッキ処理によって基板上にメッキされる導電体のメッキ厚を変更して、残存導電体厚を得るためにメッキ処理から前記研磨処理に至るシミュレーションを繰り返し実行する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】耐湿性を向上することのできる化合物半導体装置およびその製造方法を提供する。

【解決手段】化合物半導体装置は、オーミック電極OMEa〜OMEdと、絶縁膜ILと、金を含む配線IC1a〜IC1dと、金を含む配線IC2a〜IC2dとを備えている。絶縁膜ILはオーミック電極OMEa〜OMEdの一部上に形成されている。配線IC1a〜IC1dは、オーミック電極OMEa〜OMEd上で絶縁膜ILが形成されていない部分であって、絶縁膜ILの側面に接触する位置に形成されている。配線IC2a〜IC2dは、絶縁膜IL上および配線IC1a〜IC1d上に形成されている。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】 プラズマダメージを与えることなく膜中の残留不純物を低減でき、膜の平坦性を向上でき、さらには、プリカーサの使用量を抑えつつ堆積速度を向上させることができる半導体装置の製造方法および基板処理装置を提供することを目的とする。

【解決手段】 基板上に絶縁膜を形成する工程と、絶縁膜上に高誘電率絶縁膜を形成す

る工程と、高誘電率絶縁膜上に窒化アルミニウムチタン膜を形成する工程と、を有し、窒化アルミニウムチタン膜を形成する工程では、窒化アルミニウム膜の形成と、窒化チタン膜の形成と、を交互に繰り返し行い、その際、最初および/または最後に前記窒化アルミニウム膜を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに導電性パターン及びその形成方法

【課題】有機トランジスタの電極として利用可能で、かつ、塗布法で形成可能な金属種を用いて電極を形成し、当該電極と下地層との間の段差を無くす。

【解決手段】薄膜トランジスタの製造方法であって、基板101上に有機金属化合物を塗布する第1塗布ステップと、基板101上に塗布された有機金属化合物の第1領域を第1雰囲気中で加熱することで、導電性の低い平坦化絶縁層103を形成する第1絶縁領域形成ステップと、有機金属化合物の第1領域とは異なる第2領域を、第1雰囲気とは異なる第2雰囲気中で加熱することで、平坦化絶縁層103より導電性の高いゲート電極102を形成する電極領域形成ステップとを含み、平坦化絶縁層103の厚さとゲート電極102の厚さとは等しく、平坦化絶縁層103とゲート電極102との表面が平坦である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】CMP(Chemical Mechanical Polishing)ストッパ膜を終点検出膜として利用しつつ、CMPによる平坦化精度を向上させる半導体装置及びその製造方法の提供。

【解決手段】ゲート電極3a上にはシリサイド層7aを形成するとともに、ゲート電極3b上にはシリサイド防止膜4bを形成し、半導体基板1上の第1の領域においては、シリサイド防止膜4bが露出するように、犠牲膜10、CMPストッパ膜9および層間絶縁膜8のCMPを行い、第2の領域においては、CMPストッパ膜9が露出するように、犠牲膜10のCMPを行うことで、第1の領域R1および第2の領域R2を平坦化する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置又はその製造方法を提供する。また、消費電力の低い半導体装置又はその製造方法を提供する。

【解決手段】ゲート電極として機能する透光性を有する導電層と、該透光性を有する導電層上に形成されるゲート絶縁膜と、ゲート電極として機能する透光性を有する導電層上にゲート絶縁膜を介して半導体層と、半導体層に電気的に接続されたソース電極又はドレイン電極として機能する透光性を有する導電層とで構成されている。

(もっと読む)

配線の作製方法及び表示装置の作製方法

【課題】配線の凹凸やコンタクト不良を大幅に低減した配線の作製方法を用いることによって半導体装置の信頼性を向上させること。

【解決手段】層間絶縁膜207に設けられた開口部に液滴吐出法を用いてノズル208から導電性組成物が分散された液滴209を滴下し配線210を形成する。さらに、加熱処理を行うことで配線210をリフローする。これにより、配線表面を平坦化し、且つ配線のコンタクト不良を改善することができる。

(もっと読む)

水性酸浴および銅を電解析出するための方法

特に、ブラインドマイクロビア(BMV)およびトレンチにおいて非常に均一な銅析出を生成させるために、銅を電解析出するための水性酸浴が提供され、前記浴は、少なくとも1種の銅イオン源、少なくとも1種の酸イオン源、少なくとも1種の光沢剤化合物および少なくとも1種のレベラー化合物を含み、少なくとも1種のレベラー化合物は、合成によって製造される非官能基化ペプチドおよび合成によって製造される官能基化ペプチドおよび合成によって製造される官能基化アミノ酸を含む群から選択される。  (もっと読む)

(もっと読む)

銅表面上への選択的コバルト堆積

本発明の実施形態は、露出誘電表面を覆う銅表面上にコバルト層を選択的に形成するプロセスを提供する。一実施形態では、前処理プロセスの間に金属銅表面を形成している間は処理チャンバー内の基板の汚染された銅表面を還元剤にさらすステップと、気相堆積プロセスの間に基板上の誘電表面を露出したままにしながら金属銅表面を覆ってまたは上にコバルトキャッピング層を選択的に形成するために基板をコバルト前駆体ガスにさらすステップと、コバルトキャッピング層および誘電表面を覆ってまたは上に誘電障壁層を堆積させるステップとを包含する、基板上の銅表面をキャッピングするための方法が、提供される。別の実施形態では、堆積−処理サイクルは、気相堆積プロセスを実行した後に後処理プロセスを実行するステップを包含し、その堆積−処理サイクルは、複数のコバルトキャッピング層を形成するために繰り返されてもよい。  (もっと読む)

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】特性劣化を引き起こすゲート電極表面の凹凸が抑えられた、可視光に対して透明な薄膜トランジスタおよびその製造方法を提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、半導体層と、ソース電極と、ドレイン電極と、から少なくとも構成されるボトムゲート型の薄膜トランジスタであって、該トランジスタを構成するすべての部材は、可視光に対して透明であり、該ゲート電極と該ゲート絶縁層との界面において、該界面の垂直方向の凹部と凸部の差は30nm以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置および、その製造方法

【課題】LDDサイドウォール形成時に、NMOS/PMOS境界領域の2重エッチングによる不具合を克服する。

【解決手段】NMOS/PMOS境界領域にゲートレベル配線を形成し、LDDサイドウォール形成時に2重エッチングされるゲートレベル配線の最上層に、サイドウォール絶縁膜層とエッチング選択比のとれる膜107をハードマスクとして形成しておくことで、ゲートレベル配線に接続するプラグコンタクト112形成時にゲート電極のオーバーエッチによる堆積物の付着を防止する。

(もっと読む)

半導体装置の製造方法、電子機器の製造方法、半導体装置および電子機器

【課題】半導体装置の特性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、第1基板(S1)上に、ゲート電極(15)を形成する工程と、第2基板(S2)の上部にソース、ドレイン電極(25s,25d)を形成する工程と、前記第1基板と第2基板とを絶縁材料よりなる接着材(35)を介して貼り合わせる工程であって、前記ゲート電極およびソース、ドレイン電極が、前記接着材中に埋め込まれるよう貼り合わせる接着工程と、前記第2基板を剥離することにより前記ソース、ドレイン電極および前記接着材表面を露出させる工程と、前記ソース、ドレイン電極および前記接着材表面上に有機半導体膜(45)を形成する工程と、を有する。かかる方法によれば、接着材等の表面の平坦性が向上し、有機半導体膜の成膜性を向上できる。また、ゲート絶縁膜となる前記接着材と有機半導体膜との界面が良好となる。

(もっと読む)

半導体装置

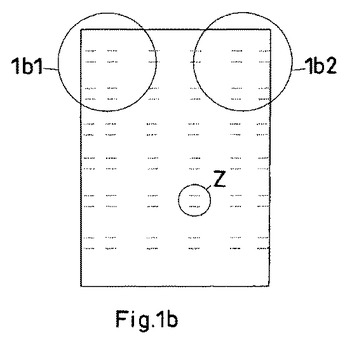

【課題】メタルCMP本来の平坦化効果を維持しつつ、マスクずれが発生してもトランジスタ特性の不均一性を可能な限り抑制し得るような、メタルダミーパターンの構造を提案する。

【解決手段】ゲート電極1の上方に形成されたメタルダミーパターン6は、ゲート長方向D1に延びており、かつ、その両端がゲート電極1の領域から突き出している。配線のマスクずれの発生により、メタルダミーパターン6の位置が設計時からずれた場合であっても、ゲート電極1の領域内において、ゲート電極1の中心GCから見たメタルダミーパターン6の形状は、左右対称性が保たれる。

(もっと読む)

有機半導体発光装置

【課題】低電圧駆動,高駆動電流の有機薄膜トランジスタと集積化され、平坦性を保持し、発光特性や歩留りの向上する面発光型の有機半導体発光装置。

【解決手段】基板10上に配置されたゲート電極120と、ゲート電極上に配置されたゲート絶縁膜15と、ゲート絶縁膜上に配置されたソース電極16およびドレイン電極18と、ソース電極とドレイン電極間のゲート絶縁膜上に配置された有機半導体層400と、有機半導体層400上に複数層繰り返し配置された正孔輸送層/発光層/電子輸送層の積層構造からなる有機薄膜トランジスタと、有機薄膜トランジスタの周辺部において、基板10上に配置されたアノード電極30と、アノード電極上に複数層繰り返し配置された正孔輸送層/発光層/電子輸送層の積層構造からなる有機半導体発光素子とを備える。

(もっと読む)

液晶表示装置

【課題】IPS方式の反射型液晶表示装置において、凹凸を有する反射電極の影響で液晶層の厚さにバラつきが出て、コントラストが劣化することを対策する。

【解決手段】TFT基板の樹脂層18の上に凹凸を有する反射電極19、20が形成されている。反射電極19、20の上には画素電極23として塗布型のITOが0.5μm〜1μmの厚さで塗布されている。塗布型ITOの表面は平坦になっている。画素電極23の上には容量絶縁膜22が形成され、容量絶縁膜22の上には櫛歯状のコモン電極21が形成されている。コモン電極21と画素電極23の間に電圧を印加すると漏れ電界によって液晶25が制御される。コモン電極21が平坦な面に形成されているために、液晶層25の厚みを均一にすることが出来、最適なコントラストを得ることが出来る。

(もっと読む)

銅含有薄膜及びその製造法

【課題】ルテニウム含有薄膜を下層金属膜とした、平坦な連続銅含有薄膜及びその製造法を提供する。

【解決手段】アルコキシアルキルメチル基を有するβ-ジケトナト及び少なくともふたつの二重結合をもつ不飽和炭化水素化合物を配位子とする、有機ルテニウム錯体を化学気相蒸着法によりルテニウム含有薄膜を製造させた後、次いで、そのルテニウム含有薄膜の上に、ビス(2,6-ジメチル-2-トリメチルシリルオキシ-3,5-ヘプタンジオナト)銅(II)錯体を化学気相蒸着法により銅含有薄膜を形成する。

(もっと読む)

101 - 120 / 219

[ Back to top ]