Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

81 - 100 / 219

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

導電性ポリマー組成物およびそれから作製されたフィルム

本開示は、導電性ポリマー組成物、およびそれらの電子デバイス中での使用に関する。本発明の組成物は:(i)非フッ素化ポリマー酸でドープした少なくとも1種類の導電性ポリマーと;(ii)少なくとも1種類の高フッ素化酸ポリマーと;(iii)電気絶縁性酸化物ナノ粒子とを含む水性分散体である。  (もっと読む)

(もっと読む)

半導体ウェーハの薄膜を堆積および平坦化する装置

【課題】半導体ウェーハの堆積および平坦化に関し、特に、局所堆積を使用して薄膜をより効果的に堆積させると共に、局所平坦化を可能にする装置および手法を提供する。

【解決手段】陽極として帯電可能な近接ヘッド102を、ウェーハ104の表面に極めて近接して配置する。メッキ流体を、前記ウェーハと前記近接ヘッドとの間に提供し、局所金属メッキを形成する。近接ヘッドが方向120でウェーハ全体を進む際に、シード層106上に堆積層108が形成される。堆積層は、近接ヘッドとシード層との間に定められたメニスカス116に含有される電解質110によって促進される電気化学反応を介して形成される。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】表面性状が良好なCVD−Cu膜を成膜することができるCu膜の成膜方法を提供する。

【解決手段】表面にCVD−Ru膜を成膜したウエハを準備する。酸素雰囲気にさらすことによりRu膜表面を酸化処理し、次に水素プラズマによる還元処理をし、清浄化する。清浄化されたRu膜表面にCu錯体からなる成膜原料を供給してCVD法によりCu膜を成膜する。

(もっと読む)

高導電性と高透明性を併有する有機薄膜とその製造法ならびにそれらを用いて形成された有機デバイス。

【課題】本発明は、高導電性と高透明性を併有する有機薄膜とその製造法、ならびにそれらを用いて製造される有機デバイスを提供する。

【解決手段】先ず、導電性高分子とこの導電性高分子材料の溶解性を高めるための絶縁性の高分子材料からなるドーパントとを溶媒に溶解し、導電性を高めるために1次粒子を分割して粒径の小さく揃った溶液を基板の表面に供給すると共に、当該基板を回転させ、前記基板の表面に1次コロイド粒子の単層又は数層からなる塗布膜を形成する。続いて前記基板を加熱して前記塗布膜中の溶媒を除去し、高導電性と高透明性を併有する有機薄膜を形成する。また前記溶液を基板の中心部に供給する前に、当該溶液に対して基板の漏れ性を高めるためにプリウエット液を基板の表面に塗布してもよい。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー内にウエハを搬入し、安定化させた後、ウエハを加熱しつつチャンバー内にCu錯体からなる成膜原料を気相状態で導入してウエハ上にCVD法によりCu膜を成膜し、成膜後、チャンバー内をパージして残留ガスを除去し、その後、チャンバーから基板を搬出するCu膜の成膜方法を実施するにあたり、パージの際に、ウエハへの入熱をCu膜成膜の際よりも低下させる。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供する。

【解決手段】ウエハW上の絶縁膜にビアホールとトレンチを形成し、この上にバリア層としてCVD−Ru膜を成膜する。チャンバー1内にウエハWを収容し、チャンバー1内に1価Cuβジケトン錯体であるCu(hfac)TMVSと、これを還元するアンモニア、還元性Si化合物、カルボン酸などの還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

半導体装置

【課題】半田凝固時の半田から保護膜への圧縮応力により電極を覆う部分の保護膜が割れることを低減することが可能な半導体装置を提供することを目的とする。

【解決手段】それぞれの上面が面一になるように形成された層間絶縁膜37、エミッタ電極38、及びゲート電極39の上に形成される保護膜2と、保護膜2の上に形成され保護膜2に形成されるスルーホール6を介してエミッタ電極38に接続されるエミッタ電極3とをさらに備えてトレンチゲート型の半導体装置を構成する。

(もっと読む)

エッチング液組成物

【課題】アルミニウム膜やアルミニウム合金膜などの金属膜を制御性よく、かつ、レジスト滲みの発生を抑制、防止しつつエッチングし、意図する低テーパー角を有する望ましい形状と、優れた平坦性を有する金属膜を得ることができるようにする。

【解決手段】リン酸、硝酸、有機酸塩、界面活性剤を含有する水溶液を、基板上の金属膜をエッチングするためのエッチング液組成物として用いる。

前記有機酸塩として、脂肪族モノカルボン酸、脂肪族ポリカルボン酸、脂肪族オキシカルボン酸、芳香族モノカルボン酸、芳香族ポリカルボン酸、芳香族オキシカルボン酸からなる群より選ばれる少なくとも1種の、アンモニウム塩、アミン塩、第四級アンモニウム塩、アルカリ金属塩からなる群より選ばれる少なくとも1種を用いる。

また、本発明のエッチング液組成物を、前記金属膜がアルミニウムまたはアルミニウム合金である場合に用いる。

(もっと読む)

積層構造体及びその製造方法

【課題】生産性が向上し、かつ、半導体膜の導電膜からのはみ出し量が低減できる積層構造体及びその製造方法を提供すること。

【解決手段】本発明にかかる積層構造体は、半導体膜15、ゲート絶縁膜12、ソース電極17、及びドレイン電極18を有するものである。ゲート絶縁膜12は、半導体膜15下において、半導体膜15の端から徐々に膜厚が薄くなるテーパー部を有する。ソース電極17及びドレイン電極18は、半導体膜15上において、半導体膜15のパターンからはみ出さないように形成され、半導体膜15端からの距離が0以上0.3um以下である。

(もっと読む)

半導体素子の製造方法

【課題】タングステン等のCMP(化学機械研磨)後、エロージョン量をモニタリングできるパターンを提示する。

【解決手段】ホールアレイサイズスプリットaと配列間スペースの長さスプリットbを一定に規定したモニタリングパターンを利用して、プラグCMP時に発生するエロージョンレベルを評価する。前記ホールアレイサイズによる影響はホールアレイサイズに応じて増加するため、エロージョン量は特定のサイズにおいて飽和になるのかをモニタリングする。また前記配列の間で影響を受けるスペースの長さをモニタリングする。

(もっと読む)

ジピリジル系レベリング剤によるマイクロエレクトロニクスにおける銅の電子沈積

【課題】半導体集積回路デバイス基板におけるビア構造をメタライズするための方法を提供する。

【解決手段】半導体集積回路デバイス基板は、前面、背面、ビア構造を備え、ビア構造は、基板の前面に開口部、基板の前面を内向きに伸びる側壁部、および底部を備え、前記方法は以下からなる:

半導体集積回路デバイス基板に、(a)銅イオン源、および(b)レベラー化合物からなる電解銅沈積組成物を接触させて、前記レベラー化合物はジピリジル化合物およびアルキル化剤の反応生成物からなり;

電流を電解銅沈積組成物に供給し銅金属をビア構造の底部および側壁部に沈積し、これによって銅充填ビア構造を得る。

(もっと読む)

電極の製造方法、これを用いた薄膜トランジスタ素子及び有機エレクトロルミネッセンス素子

【課題】透明導電性微粒子を含む流動性材料の塗布により、ゲート電極を形成する方法において、従来よりも低抵抗、かつ充分な表面平滑性をもった透明導電膜の製造方法を提供する。

【解決手段】ガラス基板106上に、金属酸化物微粒子(ITO)及び金属酸化物の前駆体を含む薄膜104”を塗布する。この薄膜にマイクロ波を照射することにより、前駆体が発熱体として作用し、焼成され、導電性薄膜を形成する。これをパターンニングしゲート電極104とする。ついで、ゲート絶縁膜105を形成し、半導体前駆体を塗布、乾燥し、半導体前駆体材料薄膜101’を得る。これにマイクロ波を照射することにより、ゲート電極が発熱し、この熱により半導体前駆体材料薄膜が加熱され、酸化物半導体膜に変換され半導体層101が形成される。マスクを介して金を蒸着し、ソース、ドレイン電極102,103を形成し、薄膜トランジスタとする。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

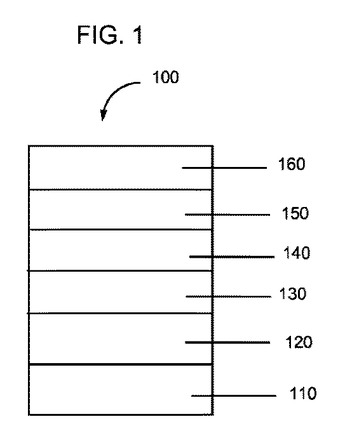

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁膜のプラズマ処理方法を提供する。

【解決手段】本発明に係るプラズマ処理方法の一形態は、絶縁膜が形成された基板を真空容器内に搬入する工程と、上記真空容器内に供給された処理ガスに300MHz以上2500MHz以下の周波数を有する高周波電力を供給することによりプラズマを生成し、上記プラズマにより、上記絶縁膜を改質する工程と、を含むプラズマ処理方法であって、上記処理ガスは、希ガスと酸素を含む混合ガス、または希ガスと窒素を含む混合ガスであり、上記プラズマは、上記処理ガスが希ガスと酸素を含む混合ガスの場合、上記酸素ガスの流量を1〜1000sccm、上記希ガスの流量を200〜3000sccmとして、上記処理ガスが希ガスと窒素を含むガスの場合、窒素ガスの流量を10〜500sccm、上記希ガスの流量を200〜3000sccmとして生成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の高抵抗化を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板10の表面に設けられ、上面がほぼ同一平面をなすメモリセル部6の不純物拡散層11a及び周辺回路部7の不純物拡散層11bと、不純物拡散層11a、11bの上面を被うように形成さられた膜厚がほぼ一定の絶縁膜12、14と、絶縁膜12、14内に形成され、不純物拡散層11aと接続されたメタルプラグ13aと、絶縁膜12の内に形成され、メタルプラグ13aより短く形成され、不純物拡散層11bと接続されたメタルプラグ13bと、メタルプラグ13aの上端部と接続され、上面が絶縁膜14と面一に埋め込まれたメタル配線15aと、メタルプラグ13bの上端部と接続され、上面が絶縁膜14と面一に埋め込まれたメタル配線15bとを備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、半導体基体との界面における組成の均一性に優れ、ショットキー接合層との十分に高い密着性が得られるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第一半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第二半導体領域6bと、第一半導体領域1aにオーミック接触するオーミック接合層7と、第二半導体領域6bにショットキー接触するショットキー接合層8とを備え、オーミック接合層7の二乗平均粗さが、20nm以下である半導体装置とする。

(もっと読む)

81 - 100 / 219

[ Back to top ]