Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

41 - 60 / 219

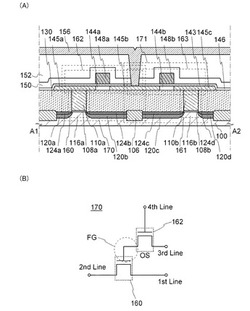

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造工程数を大幅に増加することなく高性能な薄膜トランジスタを備えた薄膜トランジスタ回路基板、及び、薄膜トランジスタ回路基板の製造方法を提供する。

【解決手段】 絶縁基板上に配置されたゲート電極と、前記ゲート電極の上に配置されたゲート絶縁膜と、前記ゲート絶縁膜の上に配置されたポリシリコンによって形成され、前記ゲート電極の直上に位置するチャネル領域、前記チャネル領域に隣接するとともに前記チャネル領域よりも高濃度の不純物を含む低濃度不純物領域、及び、前記低濃度不純物領域に隣接するとともに前記低濃度不純物領域よりも高濃度の不純物を含む高濃度不純物領域を含む半導体層と、前記チャネル領域及び前記低濃度不純物領域の上に配置され、前記チャネル領域の直上の膜厚が前記低濃度不純物領域の直上の膜厚よりも厚い保護膜と、前記高濃度不純物領域に電気的に接続された電極と、を備えたことを特徴とする薄膜トランジスタ回路基板。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

透明導電膜の形成方法

【課題】透明導電膜を低コストかつ高効率で作製することができ、基板の大面積化への対応も容易な透明導電膜の形成方法を提供する。

【解決手段】本発明の透明導電膜の形成方法は、酸化インジウム錫化合物からなるITO粒子を含有する導電性インク(Ink)を、その表面に所定のパターンのインク保持部が形成されたフレキソ印刷版11に保持させる工程と、このフレキソ印刷版11に、絶縁透光性基板10を密着させ、上記インク保持部に保持された導電性インクを基板10の所定位置に転写する工程と、この転写後に上記転写された導電性インクを加熱して、絶縁透光性基板10上に、所定パターンの透明導電膜を形成する工程と、を備える。

(もっと読む)

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ工程を行う際に、光が乱反射することを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板1上に下層配線構成膜2aを形成し、当該下層配線構成膜2aをパターニングして下層配線2を形成する工程と、基板1に下層配線2を覆う層間絶縁膜4を形成し、層間絶縁膜4にビアホールを形成する工程と、スパッタ法により層間絶縁膜4上に第1上層配線構成膜7aを形成する工程と、第1上層配線構成膜7aを形成する工程の温度より高い温度で、第1上層配線構成膜7aをリフローする工程と、リフローする工程より低い温度のスパッタ法により第1上層配線構成膜7a上に第2上層配線構成膜8aを形成する工程と、第2上層配線構成膜8a上に反射防止膜9を成膜する工程と、反射防止膜9上にレジストを形成する工程と、を含む工程を行う。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

導電性薄膜の形成方法及び導電性薄膜形成装置

【課題】スパッタ成膜において、あらゆる膜特性を同時に満足させる手法を提供すること。

【解決手段】スパッタ現象を利用して基板上に導電性薄膜を形成する方法であって、薄膜形成中に、スパッタ電力、スパッタガス、および反応性ガスを含む成膜パラメータの少なくとも1つを2つの値に変動させ、その時間分割比を制御することを特徴とする導電性薄膜の形成方法である。また、p型またはn型の導電型を有する半導体上に導電性薄膜を形成する方法において、半導体上への成膜開始時点に、強度にプラズマ照射を行うことを特徴とする導電性薄膜の形成方法も採用できる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

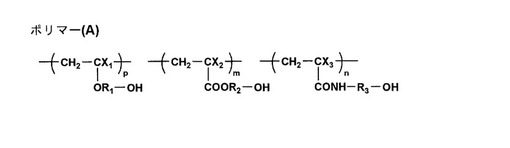

有機電子デバイス用電極

【課題】透明性、導電性且つ生産後のロール状態での保存性が良好な有機電子デバイス用電極の提供。

【解決手段】透明基材上に、導電性の金属細線パターンと、導電性ポリマー層を設けた有機電子デバイス用電極において、該金属細線パターンの金属細線の厚みをaとし、開口部における該導電性ポリマー層の厚みをbとしたとき、以下式1〜式3で表される条件を満たし、且つ、導電性ポリマー層がπ共役系導電性高分子とポリアニオンとを含んでなる導電性ポリマーおよび下記ポリマー(A)を有する有機電子デバイス用電極。0.2≦a≦2.0(式1)0.2≦b≦2.0(式2)−0.2≦b−a≦1.8(式3) (もっと読む)

(もっと読む)

41 - 60 / 219

[ Back to top ]