Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

61 - 80 / 219

半導体素子用エピタキシャル基板の製造方法、半導体素子用エピタキシャル基板、および半導体素子

【課題】簡便な手法によってエピタキシャル基板の障壁層表面の平坦性を向上させ、ショットキーコンタクト特性の優れたエピタキシャル基板を実現する方法を提供する。

【解決手段】半導体素子用のエピタキシャル基板を製造する方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層をエピタキシャル形成するチャネル層形成工程と、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層をエピタキシャル形成する障壁層形成工程と、障壁層形成工程における加熱温度よりも100℃以上250℃以下高い加熱温度で障壁層が形成された下地基板を加熱することにより、障壁層の表面平坦性を向上させる平坦化処理工程と、を備える。

(もっと読む)

SiC半導体素子の製造方法

【課題】薄板化に伴うSiC基板の反りを修正するSiC半導体素子の製造方法の提供を目的とする。

【解決手段】本発明の半導体素子の製造方法は、(a)表面側に素子活性領域が形成されたSiC基板1を準備する工程と、(b)SiC基板1の表面を平坦面に固定し、裏面を研削する工程と、(c)SiC基板1の表面を平坦面に固定したまま、研削によるSiC基板の反りを相殺する応力を付与する内部応力層を、SiC基板内部に形成する工程とを備える。

(もっと読む)

半導体デバイスの製造方法

【課題】アンダーバンプメタル形成のための無電解めっき処理の際に、薄型ウェハのハンドリング性を維持しながら、めっき時のウェハの破損を防止すると共にウェハの非めっき面へのめっき付着を防止する。

【解決手段】ウェハ裏面のバックグラインディング工程1と、次いで、ウェハの裏面に再剥離型粘着剤を粘着面にもつ粘着フィルムを1枚又は2枚以上積層して貼り付ける工程2と、次いで、粘着フィルムが裏面に貼り付けられたウェハに対して、ウェハ表面にアンダーバンプメタル(UBM)を形成するための無電解めっき処理工程3と、次いで、粘着フィルムを剥離する工程4を実施することを含む半導体デバイスの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】ボイド、ディッシング、及びエロージョンの発生を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に幅の異なる複数の開口部36,37を形成し、次いで、絶縁膜の上面、及び幅の異なる複数の開口部内にシード層38を形成し、次いで、第1の成長速度により、シード層の表面を覆う第1のめっき膜71を形成し、次いで、第1の成長速度よりも速く、かつボイドを生じさせない第2の成長速度により、第1のめっき膜の表面に第2のめっき膜72を形成し、次いで、第2の成長速度よりも速い第3の成長速度により、第2のめっき膜上に第3のめっき膜73を形成し、その後、シード層及び第1乃至第3のめっき膜のうち、絶縁膜の上面よりも上方に形成された部分を研磨により除去することで、開口部内に少なくとも第1及び第2のめっき膜よりなる導電部を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、電極表面を平坦化した高い信頼性を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】n形ベース層2と、n形ベース層2の表面に設けられたp形ベース領域3と、p形ベース領域3の表面に選択的に設けられたn形エミッタ領域4と、p形ベース領域3およびn形エミッタ領域4とゲート絶縁膜を介して対向するゲート電極5と、p形ベース領域3およびn形エミッタ領域4に電気的に接続されたエミッタ電極21と、エミッタ電極21の表面に形成された凹部31を埋め込んだ絶縁部材25と、エミッタ電極21と絶縁部材25との上に設けられたエミッタ電極23と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

電極形成方法および電極形成装置

【課題】基板上に電極を形成する方法および装置において、互いに交わる電極の交点における凹凸を少なくする。

【解決手段】基板に多数本のフィンガー電極を形成した後に(ステップS102)、これらと交わる幅広のバス電極を塗布により形成する。電極材料および光硬化性樹脂を含む塗布液を基板に塗布した後(ステップS103)、所定時間が経過するのを待ってから塗布液にUV光を照射し塗布液を硬化させる(ステップS104)。塗布から光照射までの時間差tsについては、予め実験的に塗布した塗布液の高さの変化を測定した結果に基づいて設定しておく(ステップS101、S201〜S204)。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

成膜方法、半導体装置の製造方法及び半導体装置

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

半導体装置、設計装置、及びプログラム

【課題】リングゲート型MOSトランジスタ間の領域だけでなく、リング内の領域においてもディッシング現象の発生を抑止する。

【解決手段】半導体装置1は、基板10と、基板10上に形成されたリング形状のゲート電極21を有するトランジスタ20bと、ゲート電極21の外側に配置され、ゲート電極21と同層に設けられる複数の外部ダミーパターン40と、ゲート電極21の内側に配置され、ゲート電極21と同層に設けられる少なくとも1つの内部ダミーパターン41とを備える。

(もっと読む)

成膜装置、成膜方法及び記憶媒体

【課題】真空容器内にて反応ガスによりチタンナイトライド膜を形成するにあたり、当該チタンナイトライド膜を速やかに成膜すると共に、表面形状が平滑なチタンナイトライド膜を得ること。

【解決手段】チタンナイトライド膜の成膜処理を行う時に、回転テーブル2と各ガスノズル31、32、41、42とを100rpm以上で相対的に回転させることによって、反応ガスの供給サイクル(反応生成物の成膜サイクル)を高速で行うことができるので、薄膜を速やかに形成することができ、またサイクル間の時間が極めて短いので、基板の表面に生成した反応生成物の結晶化による粒子径の粗大化が進行する前に次の反応生成物の層を上層側に積層して平滑な表面を得ることができる。

(もっと読む)

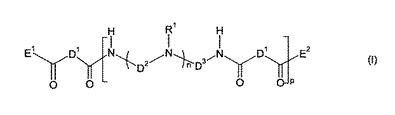

平滑化剤を含む金属電気メッキのための組成物

金属イオン供給源、及び式I

【化1】

によって表される、少なくとも1種のポリアミノアミド、又は完全な、又は部分的なプロトン化、N−四級化、又はアシル化によって得ることができる、式Iのポリアミノアミドの誘導体を含む、少なくとも1種の添加剤を含む組成物。

(もっと読む)

半導体装置の製造方法

【課題】CMPのストッパ膜として多結晶シリコン膜を用いた場合においても、多結晶シリコン膜の表面に発生するスクラッチを低減させる。

【解決手段】半導体基板11上に形成された多結晶シリコン膜13をストッパ膜としてシリコン酸化膜15を化学的機械的研磨にて平坦化する半導体装置の製造方法において、多結晶シリコン膜13の上層には表面改質膜13aが形成され、化学的機械的研磨のスラリ8には、セリア砥粒21と、界面活性剤と、カチオン性またはアニオン性の官能基を有する樹脂粒子22、23が含有されている。

(もっと読む)

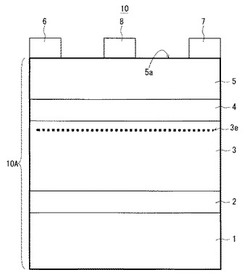

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

太陽電池素子の製造方法及び太陽電池素子

【課題】凹凸が小さく滑らかな半円形状で抵抗の低い集電極を備えた曲線因子の高い太陽電池素子を提供する。

【解決手段】半導体基板10上にスクリーン印刷法により導電性ペースト8を複数回重ねて印刷して多層電極を形成するに際し、スクリーン印刷製版7を用いて一層目の電極を印刷した後、上記基板又はスクリーン印刷製版の位置を一層目の電極印刷時の基板又はスクリーン印刷製版位置より一層目の電極の長手方向に沿ってずらした状態で上記一層目の電極の直上にこれと重ねて二層目の電極を印刷し、更に必要により、三層目以降の電極を上記と同じ方向に順次ずらして印刷して多層電極を形成する。

(もっと読む)

スパッタリング装置およびスパッタリング方法

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料のコンタクト埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、Alからなるターゲット35Bおよび開口部が形成された基板34Bを格納可能なスパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマを磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34Bとターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al材料からなる堆積膜のカバレッジ性が、プラズマ放電電流IDおよび基板バイアス電圧VAに基づいて調整されている。

(もっと読む)

半導体装置及びその製造方法

【課題】エロージョンの発生及び研磨残渣の発生がない金属からなる配線又はプラグを形成できるようにする。

【解決手段】半導体基板1上の層間絶縁膜3にコンタクトホール3aを形成する。続いて、層間絶縁膜3上に金属を含む化合物及び第1の還元性ガスを供給することにより、コンタクトホール3aを含む層間絶縁膜3の上に第1のシード層5を形成する。続いて、第1のシード層5上に金属を含む化合物及び第2の還元性ガスを供給することにより、第1のシード層5の上に第2のシード層6を形成する。続いて、第2のシード層6の上に、金属をコンタクトホール3aを埋め込むように形成する。続いて、CMP法により、層間絶縁膜3のコンタクトホール3aを除く上面に残存する金属、第2のシード層6及び第1のシード層5を除去することにより、コンタクトホール3aにプラグ7Aを形成する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】凹凸の大きいステップバンチングに対しても平坦化可能で、かつ平坦化にあたりCMP研磨などの研磨工程を必要としない炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】炭化珪素基板の表面上に、活性領域となり表面にステップバンチングが生じやすいC/Si比を有する第1の炭化珪素層を形成する第1工程と、前記第1の炭化珪素層の表面上に、表面が平坦となるC/Si比を有する第2の炭化珪素層を形成する第2工程と、前記第2の炭化珪素層をエッチング除去する第3工程とを備えている。

(もっと読む)

導電膜パターン及び導電膜パターンの形成方法

【課題】膜厚のばらつき及び表面の平坦性に優れ、基材との十分な密着性を有する導電膜パターンを、複雑、高価な設備、工程を必要とせずに形成する導電膜パターン及びその形成方法を提供する。

【解決手段】金属微粒子含有インクを基材上に配置し、焼成することにより形成される導電膜パターンにおいて、前記基材のインク被配置面に、有機塩あるいは無機塩の含有されたプライマー層が形成されているものであることを特徴とする導電膜パターン。

(もっと読む)

有機半導体に電気接点を形成する方法

【課題】雰囲気条件下で簡単に実施でき、安価な金属箔を使用できる、有機半導体表面に電気接点を形成する方法を提供する。

【解決手段】半導体表面に溶媒層を形成し、前記表面、少なくともその下面が部分的に酸化された金属箔を載置し、次いで前記溶媒を蒸発させる。本発明方法によると、経済的な競争力が向上し、同時に半導体の構造の保持、及び高い界面導電性がその品質的な価値を上昇させる。

(もっと読む)

61 - 80 / 219

[ Back to top ]