Fターム[4M104HH12]の内容

Fターム[4M104HH12]に分類される特許

21 - 40 / 219

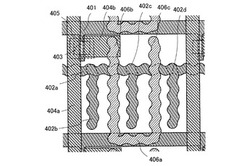

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 より平滑な表面を持ち、かつ、更なる薄膜化を達成することが可能なアモルファスシリコン膜の成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを供給し、下地2表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2表面のシード層3にアミノ基を含まないシラン系ガスを供給し、シード層3上にアモルファスシリコン膜4を、層成長する厚さに形成する工程と、層成長する厚さに形成されたアモルファスシリコン膜4をエッチングし、該アモルファスシリコン膜4の膜厚tを減ずる工程とを備える。

(もっと読む)

半導体装置及びそれを用いた電力変換装置

【課題】低損失、高耐圧、出力電圧のdV/dtの制御が容易で、製造が容易なIGBTを提供する。

【解決手段】第1導電型の第1半導体層と、第1半導体層の表面の第2導電型の第2半導体層と、第1半導体層の表面に形成されたトレンチと、第1半導体層の表面の半導体凸部と、半導体凸部の表面形成された第3半導体層と、第3半導体層の表面の第4半導体層と、トレンチの内壁に沿って設けられたゲート絶縁層と、トレンチの内壁に沿って設けられた第1層間絶縁層と、ゲート絶縁層を介して第4半導体層に対向する第1導電層と、第1層間絶縁層の第2導電層と、第2導電層の表面を覆う第2層間絶縁層と、第3半導体層と第4半導体層の表面に形成され、前記第4半導体層に電気的に接続される第3導電層と、第3導電層と第3半導体層を接続するコンタクト部と、第2半導体層の表面に形成された第4導電層とを備え、半導体凸部の表面の一部が第1半導体層である。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

Ni膜の形成方法

【課題】 成膜温度、成膜圧力、還元ガスの使用量・使用割合等の成膜条件を設定することにより、所望の物性を有する利用範囲の広いNi膜の形成方法を提供すること。

【解決手段】 真空槽の中でSi基板を一定温度に保持してニッケルアルキルアミジナート(但し、アルキルは、メチル基、エチル基、ブチル基及びプロピル基から選ばれる。)とH2とNH3とをこの真空槽内に導入し、CVD法でNi膜を形成する方法であって、成膜温度が280℃より高く350℃以下であること。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

導電性膜形成用銀合金スパッタリングターゲットおよびその製造方法

【課題】 ターゲットの大型化に伴い、ターゲットに大電力が投入されてもスプラッシュを抑制することができると共に、耐食性および耐熱性に優れ、低電気抵抗の膜を形成可能な導電性膜形成用銀合金スパッタリングターゲットおよびその製造方法を提供すること。

【解決手段】 導電性膜形成用銀合金スパッタリングターゲットが、Ga,Snの内の1種または2種を合計で0.1〜1.5質量%を含有し、残部がAgおよび不可避不純物からなる成分組成を有した銀合金で構成され、銀合金の結晶粒の平均粒径が120〜400μmであり、結晶粒の粒径のばらつきが、平均粒径の20%以下である。

(もっと読む)

金属酸化物粒子分散組成物

【課題】成膜後の金属酸化物粒子の緻密性を改善することができ、所望の性能を有する金属酸化物半導体薄膜や透明導電膜を形成することが可能な金属酸化物粒子分散組成物を提供する。

【解決手段】金属酸化物粒子と、金属塩及び/又は有機金属化合物と、溶媒とを含有する透明導電膜形成用の金属酸化物粒子分散組成物であって、前記金属酸化物粒子は、Zn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属の酸化物を含有し、かつ、前記金属塩及び/又は有機金属化合物は、Zn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属の金属塩及び/又はZn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属を含む有機金属化合物である金属酸化物粒子分散組成物。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】より良質なゲート電極を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、ドレイン層と、前記ドレイン層の上に設けられたドリフト領域と、前記ドリフト領域の上に設けられたベース領域と、前記ベース領域の表面に選択的に設けられたソース領域と、前記ソース領域から前記ベース領域を貫通し、前記ドリフト領域に到達するトレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、前記ドレイン層に接続された第1主電極と、前記ソース領域および前記ベース領域に接続された第2主電極と、を備える。前記ゲート電極は、第1導電層と、前記第1導電層と前記ゲート絶縁膜との間に介在する第2導電層と、を含み、前記第2導電層の不純物濃度は、前記第1導電層の不純物濃度よりも低い。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

21 - 40 / 219

[ Back to top ]