Fターム[4M106DA15]の内容

半導体等の試験・測定 (39,904) | 不良素子識別装置 (308) | マップ (169) | ウエハマップ (161)

Fターム[4M106DA15]に分類される特許

121 - 140 / 161

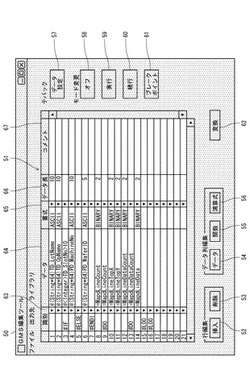

基板検査システム及び記憶媒体

【課題】基板検査システムの稼働率の低下を防止することができると共に、検査プローバの製造者の工数を削減することができる基板検査システムを提供する。

【解決手段】GMS10は、ICチップの電気的検査を行う検査プローバ11及びディスプレイ39を有するPC44を備え、PC44は、利用者の所望のタイミングでディスプレイ39にGMS編集ツール50を表示し、GMS編集ツール50のフォーマット入力部51において編集された検査結果のフォーマットを表すデータを受け付け、さらに、受け付けた検査結果のフォーマットを表すデータをスクリプトに変換して検査プローバ11に送信し、検査プローバ11は、送信されたスクリプトを出力用プログラムに変換し、該出力用プログラムに応じてICチップの検査結果を出力する。

(もっと読む)

異なるコンポーネントを備える集積回路の製造方法

第1タイプの第1の電気コンポーネントと、第2タイプの第2の電気コンポーネントとを備え、当該2つのコンポーネントは、これらのコンポーネントが欠陥であるかないかをテストするために、異なる測定条件を必要とする、集積回路素子の製造方法について記載する。当該製造方法は、(a)基板上に第1及び第2のコンポーネントを形成するステップと、(b)第1及び第2のコンポーネントを接続し、第1のコンポーネントを測定装置と個別に接続することを可能にするガルバニックギャップを有する導体路を、基板上に設けるステップと、(c)測定装置によって第1のコンポーネントのテストを行うステップと、(d)テスト結果が第1のコンポーネントに欠陥がないことを示す場合に、導電接続によってガルバニックギャップを閉じ、テスト結果が第1のコンポーネントに欠陥があることを示す場合には、対応する集積回路素子を欠陥品として識別するステップと、を備えている。更に、複数の回路素子、1つの回路素子及び1つの集積回路を備えている集積回路の製造方法について記載する。  (もっと読む)

(もっと読む)

集積回路の製造方法。

【課題】集積回路の設計ルールの微細化が進むにつれて、歩留まりとの相関関係を考慮しなければならない欠陥数が指数関数的に多くなるので、高効率かつ高い信頼性をもつ欠陥と電気的歩留まりの相関関係を抽出するためのキラーレイシオ法(Killer-Ratio)の精度を維持する方法を提供する。

【解決手段】ウェハ120のチップ121a〜121iにおける機能PT(n)のが良品である領域(m,n)122b(領域122b内の欠陥123bが存在するものも含む)の歩留まりと機能PT(n)のが不良である領域(m,n)122a(領域122a内の欠陥123aが存在しないものも含む)との機能PT(n)の歩留まりとを用いて、キラーレイシオを算出する。

(もっと読む)

ウエーハマップデータの解析方法および解析プログラム

【課題】システム不良とランダム不良との不良種別の分類を簡単に行うことができるウエーハマップデータの解析方法および解析プログラムを提供する。

【解決手段】有効チップ領域の検査合否を表すウエーハマップデータ30から検査データが“1”である不良チップ座標を1つ選択する。選択した不良チップ座標31に隣接するように複数のチップ座標からなる判定領域32を設定する。この判定領域32のデータが全て“1”の場合には不良チップ座標31の不良種別をシステム不良とし、その他の場合には不良チップ座標31の不良種別をランダム不良とする。なお、有効チップ領域外を仮想的に“1”に設定し、エッジ部も含め、有効チップ領域内の全ての不良チップ座標について不良種別の分類を行う。

(もっと読む)

シリコンウェーハ表面歪分布測定装置

【課題】合理的な測定時間内に十分な測定点数を伴った、シリコンウェーハの最表面層の歪分布を測定することが可能なシリコンウェーハ表面歪分布測定装置を提供する。

【解決手段】アルゴンイオンレーザ10から発せられる波長約363.8nmの紫外光を集光照射機構40等を介して測定対象試料60であるシリコンウェーハ上に集光させる。紫外光が照射されるシリコンウェーハ上の領域から発せられたラマン散乱光は、集光照射機構40を介してモノクロメータ式の分光器80に入射される。CCD検出器90の映像信号からラマン散乱光のエネルギ分布を演算し、紫外光が照射されるシリコンウェーハの領域における歪量を演算する。このシリコンウェーハ表面の歪分布は、コンピュータ100等によりマッピング表示される。

(もっと読む)

特性検査図の検索システムおよび検索方法

【課題】検査対象となる製品に対応する検査図を選び出す作業には、多くの工数が必要であり、検査者にとって多大な負担となっていた。

【解決手段】検索システム1は、記憶部10、入力受付部20、検索部30、表示部40、および作成部50を備えている。記憶部10は、特性検査図を記憶する記憶手段である。特性検査図は、チップ位置情報、電極位置情報、および検査順序情報を含む。入力受付部20は、上記複数の半導体チップのうち検査対象となる半導体チップの識別情報の入力を受け付ける入力受付手段である。検索部30は、入力受付部20から入力された識別情報と関連付けられた特性検査図を、記憶部10に記憶された特性検査図の中から検索する検索手段である。表示部40は、検索部30により検索された特性検査図を表示する表示手段である。

(もっと読む)

不良検出方法

【課題】 ウェーハ毎に発生した不良の分布に基づき、半導体集積回路の製造工程に用いた異常製造装置を検出可能な不良検出方法を提供する。

【解決手段】 ウェーハに複数の領域区分を設定する。テストにおける対象ロット内の対象ウェーハのウェーハ内の不良の位置情報を抽出する。対象ウェーハ毎に不良のウェーハ面内での分布の偏りを領域区分に基づいて定量化する第1ウェーハ特徴量を計算する。この第1ウェーハ特徴量から対象ロット毎の第1ロット特徴量を算出する。処理履歴情報から対象ロットの製造工程で使用した製造装置を対象ロット毎に抽出する。第1ロット特徴量毎に、製造工程毎の製造装置間の有意差検定を行う。有意差のある製造装置を第1異常装置として検出する。

(もっと読む)

不良原因工程特定システムおよび方法、並びにその方法を実行するためのプログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】基板に対して1つ以上の工程を実行する製造プロセスにおいて不良発生の原因となった工程を容易に特定できるような不良原因工程特定システムを提供すること。

【解決手段】基板に対する所定の工程終了後に、その基板の表面で区分された各閉領域について1つ以上の不良種別に関して検査して得られた検査情報を入力する検査情報入力部を備える。複数の不良種別のうち指定された不良種別について、基板上の各閉領域の検査結果の良否を表すデータを、この製造プロセスで処理された1枚以上の基板について累積してマップデータを作成するマップデータ作成部14を備える。そのマップデータに基づいて、基板上で不良となった閉領域の分布が有する特徴を抽出する特徴抽出部15を備える。

(もっと読む)

欠陥検査装置

【課題】表面に透明薄膜が形成された基板等の試料において、透明薄膜の上面の微小な異物、キズ等の欠陥を高感度且つ高速に検査することができる欠陥検査装置を提供する。

【解決手段】本発明の欠陥検査装置によると、照明光学系は、試料の表面の法線に対して所定の入射角を有する検査用照明光を試料表面に照射し、試料表面にスリット状のビームスポットを生成する。試料の表面に対して所定の傾斜角にて傾斜した光軸を有する斜方検出系と試料の表面の法線に沿った光軸を有する上方検出系によって、ビームスポットからの光を検出する。斜方検出系と上方検出系の出力によって、試料の表面の透明薄膜上の欠陥を検出する。検査用照明光の入射角は、試料の表面の透明薄膜下面にて反射した反射光が透明薄膜上面にて全反射するときの入射角より僅かに小さい角度である。

(もっと読む)

欠陥解析システム、欠陥解析方法及び欠陥解析プログラム

【課題】 解析精度を向上し、且つ解析時間の増大を抑制する欠陥解析システム、欠陥解析方法及び欠陥解析プログラムを提供する。

【解決手段】 一連の製造工程で製造された製品のレイアウト情報に基づき、製品の欠陥解析対象領域を分割するメッシュ候補を異なるピッチで複数作成するメッシュ候補作成部31と、一連の製造工程のそれぞれにおいて検査装置11〜1nによって検査された欠陥検査の結果及びテスタ2によって試験された製品の特性試験の結果に対して、欠陥の解析精度及び解析時間を複数のメッシュ候補を用いてそれぞれ予測し、その予測に基づき複数のメッシュ候補から最適メッシュを選択するメッシュ選択部32と、最適メッシュで分割された領域毎に欠陥検査の結果及び特性試験の結果を照合して、製品の不良原因の欠陥を特定する特定部33とを備える。

(もっと読む)

半導体ウエハ上の局所性不良を検出するテスト方法及びこれを用いるテストシステム

【課題】半導体チップを有するウエハのテスト方法及びそのテストシステムを開示する。

【解決手段】このテスト方法はウエハが欠陥性のウエハ(defective wafer)であるか、または非欠陥性のウエハであるかを判断する方法として、前記判断は空間的に係るグループの濾過された不良チップをベースとする。前記空間的に係るグループは前記ウエハ上の局所性の不良に対応し欠陥指数値(defect index value)を算出するのに用いられる。

(もっと読む)

位置情報算出方法

【課題】 ウェハにおける特定のチップの位置情報を正確に算出する。

【解決手段】 チップ1aが複数個形成されたウェハ1の各チップ1aの位置情報を算出する位置情報算出方法において、ウェハ1における各チップ1aに対し、X方向のアドレスとX方向と直交するY方向のアドレスとが付与される。それらのX方向のアドレス及びY方向のアドレスを用い、ウェハ1の中心1bが算出される。その中心1bから特定のチップ1aまでのX方向のチップ数及びY方向のチップ数が算出される。算出されたX方向のチップ数とY方向のチップ数とに、それぞれX方向のチップサイズとY方向のチップサイズとが掛け合わされ、特定のチップ1aの位置情報を示す特定位置情報が算出される。

(もっと読む)

欠陥データ解析方法およびその装置

【課題】

半導体基板の製造工程において、検査装置によって検出された欠陥データに基

づいて欠陥分布状態解析を行い、装置あるいはプロセス起因の不良原因の特定を

容易にする。

【解決手段】

検査装置によって検出された欠陥位置座標に基づいて欠陥の分布状態を解析し

、繰り返し欠陥、密集欠陥、線状分布欠陥、環・塊状分布欠陥、ランダム欠陥の

うちいずれかの分布特徴カテゴリに分類する。

(もっと読む)

レーザマーキングシステム内でウエハを検査するシステム及び方法

【課題】半導体ウエハの裏面検査アセンブリで使用する照明システムが開示されている。【解決手段】照明システムは、高反射性および指向反射性表面に対して約45度〜約75度の角度αで高反射性および指向反射性表面に照明を方向付けるように構成された照明光源を備える。 (もっと読む)

半導体装置ダイの選別方法及び半導体基板

【課題】

ウエハに直接マーキングを行うことに起因する歩留まりの低下を防止すると共に、電気的特性の評価結果のデータとウエハとのデータ不一致の発生を防止することが可能な半導体装置ダイの選別方法及び半導体基板を提供する。

【解決手段】

複数の半導体装置ダイの電気的特性の評価を行い、それぞれの半導体装置ダイの評価結果とそれぞれの半導体装置ダイの半導体基板表面での位置との対応関係を記録する。そして、半導体基板の表面に保護膜を貼り付け、この貼り付けた保護膜に、電気的特性の評価結果と位置との対応関係を表示し、その後、保護膜上に表示した評価結果と位置との対応関係を読み取る。さらに、複数の半導体装置ダイを分割し、その読み取った評価結果と位置との対応関係に基づいて分割した半導体装置ダイの選別を行う。

(もっと読む)

品質管理システム及びこれを用いた半導体装置の製造方法

【課題】高歩留まりを維持することができる品質管理システム及びこれを用いた半導体装置の製造方法を提供する。

【解決手段】データ処理装置3は、基板50とこの基板50に対応する既知パターンとにおいて、基板50に対する既知パターンの占有率を示す基板50占有率を算出し、複数の基板50における既知パターンに対応する基板50の数の割合を示す既知パターン発生頻度を算出し、既知パターンに対する不良セルの占有率を示すパターン内不良率を算出し、基板50占有率と既知パターン発生頻度とパターン内不良率とを乗じた値を用いて歩留まり影響度を算出する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置のテスト時間の短縮を図る。

【解決手段】 半導体ウェハ上に形成された複数の半導体素子の各々に対する検査をウェハテストで行い、各半導体素子の各々の半導体ウェハ上の座標位置データとウェハテストの結果とを対応付けて保存(データベース1)し、半導体ウェハをダイシングし個片化した半導体素子を各々パッケージ内に組み込んでから最終テストを行う製造方法において、パッケージ内に半導体素子を組み込むとき半導体素子の半導体ウェハ上の座標位置データとパッケージに刻印されているマークとを対応付けた関連付けデータを生成して保存(データベース2)しておき、最終テストを行うときにパッケージのマークから関連付けデータを参照して求めたパッケージ内の半導体素子に対するウェハテストの結果を求め、最終テストで行うテスト項目のうちウェハテストの結果を利用できるテスト項目の実施をスキップする。

(もっと読む)

検査支援システム、及び方法

【課題】ユーザが、より良い検査条件を効率的に絞り込み可能とする。

【解決手段】本検査支援システムは、複数の検査条件によって検査装置が検出した各欠陥を、その欠陥が検出された検査条件の組み合わせで分類し、各分類ごとに、その分類に属する欠陥の、検査対象の外観上における分布を、当該分類に属する欠陥の位置情報に基づき算出する。そして、各分布を表すマップが、分類ごとに、マップ表示画面上のマップ表示フィールド1000内に表示される。

(もっと読む)

ウェーハ表面形状測定装置、及び、それを用いたウェーハの評価方法

【課題】ナノトポグラフィを正確に測定することができるウェーハ表面形状測定装置、及び、それを用いたウェーハの評価方法の提供。

【解決手段】直径300mmの片面が研磨されたウェーハを、外周部保持手段のみで、すなわち、120度の等間隔で円周上に配置された保持部で、ウェーハの外周部のベベル面を保持し表面形状を測定した。その後、中央部保持手段によりウェーハの中央部裏面を保持し表面形状を測定した。得られた画像信号を解析して、外周部保持手段により得られた画像のうち外周から20mm位置までのウェーハの外周部の画像を除外し、また、中央部保持手段により得られた画像のうち、中央保持部の領域の画像を除外して、それぞれの画像を合成して一つの画像とした。

(もっと読む)

半導体ウエーハのドーパント汚染の評価方法

【課題】半導体ウエーハの表層全体のドーパント汚染量を非接触、非破壊で、しかも正確に求めることが可能な半導体ウエーハのドーパント汚染の評価方法を提供する。

【解決手段】半導体ウエーハのドーパント汚染の評価方法であって、半導体ウエーハのバルク部の抵抗率を渦電流法により測定し、前記半導体ウエーハの表層の抵抗率を表面光電圧法により測定し、前記渦電流法により測定したバルク部の抵抗率の値と表面光電圧法により測定した表層の抵抗率の値の差から、前記半導体ウエーハのドーパント汚染量を求めることを特徴とする半導体ウエーハのドーパント汚染の評価方法。

(もっと読む)

121 - 140 / 161

[ Back to top ]