Fターム[4M119AA11]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 高集積化,微細化 (354)

Fターム[4M119AA11]に分類される特許

121 - 140 / 354

スピンメモリおよびスピントランジスタ

【課題】単方向電流で書き込みをすることを可能にするとともに回路面積が増大するのを防止することを可能にする。

【解決手段】第1強磁性層21、第1非磁性層23、第2強磁性層25、第2非磁性層27、および第3強磁性層29がこの順序または逆の順序で積層された積層構造を有し第3強磁性層と第2強磁性層とが第2非磁性層を介して反強磁性的な交換結合をする強磁性積層膜20を含むメモリセル10を備え、第1強磁性層から第3強磁性層に向かう単一方向の電流を強磁性積層膜に流して、電流の大きさに応じて第1強磁性層に異なる磁化状態の書き込みを行うとともに第1強磁性層からの読み出しを行なう。

(もっと読む)

磁気トンネル接合を有する磁気装置、メモリアレイ、及びこれらを用いた読み出し/書き込み方法

【課題】磁気トンネル接合磁気装置、メモリ、及び前記装置を用いた書き込み及び読み出し方法。

【解決手段】前記装置(16)は、半導体又は絶縁体の層(20b)によって分離された基準層(20c)と記憶層(20a)とを備える。記憶層の磁化のブロッキング温度は、基準層の磁化のブロッキング温度よりも小さい。装置はさらに、磁化のブロッキング温度よりも上に記憶層を加熱する手段(22,24)と、前記基準層の向きを変えることなく基準層の磁化に対して記憶層の磁化の向きを調整する磁場(34)を記憶層に印加する手段(26)と、を備える。

(もっと読む)

半導体集積回路

【課題】セル面積が小さい不揮発性SRAMセルを提案する。

【解決手段】本開示に係わる半導体集積回路は、第1及び第2のインバーターINV1,INV2と、ゲートにワード線WLが接続され、ソースに第1のビット線BLが接続され、ドレインに第2のインバーターINV2の入力端子が接続される第1のトランジスタM5と、ゲートにワード線WLが接続され、ソースに第2のビット線bBLが接続され、ドレインに第1のインバーターINV1の入力端子が接続される第2のトランジスタM6と、第1の端子に第1のトランジスタM5のドレインが接続され、第2の端子に第1のインバーターINV1の出力端子が接続される第1の可変抵抗素子R1と、第1の端子に第2のトランジスタINV2のドレインが接続され、第2の端子に第2のインバーターINV2の出力端子が接続される第2の可変抵抗素子R2とを備える。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】自由層と固定層の相対的な磁化方向を平行から反平行に反転する際、選択トランジスタのバックバイアス効果による書き込み電流の減少を防止でき、かつメモリセルの面積増大を防ぐことができる磁気ランダムアクセスメモリを提供できる。

【解決手段】半導体基板上に形成され、磁化方向が固定された固定層と、固定層上に形成された非磁性層と、非磁性層上に形成され、磁化方向が可変である自由層とを含むMTJ素子11と、半導体基板に形成されたアクティブ領域12と、アクティブ領域12に形成された第1の拡散領域及び第2の拡散領域を有し、第1の拡散領域が自由層に電気的に接続された第1の選択トランジスタとを備える。さらに、アクティブ領域12に形成された前記第1の拡散領域及び第3の拡散領域を有する第2の選択トランジスタと、固定層に電気的に接続された第1の配線とを備える。

(もっと読む)

磁気トンネル接合素子

【課題】より良好な磁化特性を発現し、高記録密度化や高集積化に対応可能であると共に高い信頼性を有する磁気トンネル接合素子を提供する。

【解決手段】本発明のMTJ素子は、NiFeからなり、かつ、平坦化された上面を有する基体としての下部磁気シールド層110と、Taからなり、かつ、スパッタエッチング処理により表層がアモルファス化された被覆層125と、シード層140と、ピンニング層50と、ピンド層60と、Al膜が酸化処理されてなるトンネルバリア層70と、磁化フリー層80と、キャップ層90と、NiFeからなり、下部磁気シールド層110と共に積層面と直交する方向にセンス電流を流すための電流経路となる上部磁気シールド層100とを順に備えたものである。

(もっと読む)

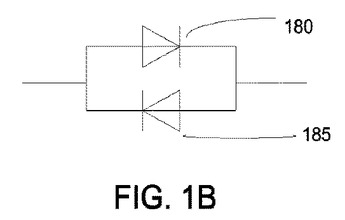

減電圧の入出力デバイス(REDUCEDVOLTAGEINPUT/OUTPUTDEVICE)を有する抵抗ベースメモリ

減電圧のI/Oデバイスを含む抵抗ベースメモリが開示される。特定の一実施形態では、回路は、第1の抵抗メモリセルおよび第1の負荷トランジスタを含むデータ経路を含む。基準経路は、第2の抵抗メモリセルおよび第2の負荷トランジスタを含む。第1の負荷トランジスタおよび第2の負荷トランジスタは、回路内のコアトランジスタのコア供給電圧と同等の負荷供給電圧で動作するように構成された入出力(I/O)トランジスタである。  (もっと読む)

(もっと読む)

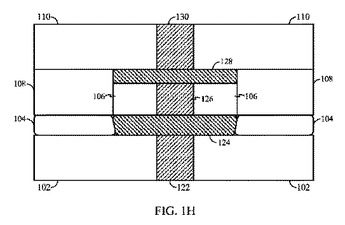

平坦化された電極上の磁気トンネル接合(MTJ)

直接接触を用いた磁気トンネル接合(MTJ)は、より低い抵抗、改善された生産量、及び、より単純な製造を有して製造される。より低い抵抗は、MTJの読み取り方法及び書き込み方法の両方を改善する。MTJ層(126)は、下部電極(124)上に堆積され、下部金属(122)に位置合わせされる。エッチング停止層(302)は、下部金属を囲う絶縁体のオーバーエッチングを防止するために下部金属に隣接して堆積され得る。下部電極は、実質的に平坦な表面を提供するためにMTJ層の堆積前に平坦化される。さらに、下層(202)は、MTJの所望の特性を促進するためにMTJ層の前に下部電極上に堆積され得る。  (もっと読む)

(もっと読む)

磁気メモリセル及び磁気メモリ

【課題】電気的手段により磁気情報の書込みを行う磁気メモリセル及びそれを装備した大容量多値磁気メモリを提供する。

【解決手段】スピン蓄積層1上に配置した複数の磁気記録ビット31〜34と、1つの検出部によって磁気メモリセルを構成し、その磁気メモリセルを多数組み合わせて大容量磁気メモリを構成する。磁気記録ビットは、スピン蓄積層上に中間層、磁気記録層、障壁層、固定層、電極保護層を積層した構造を有し、検出部はスピン蓄積層上に中間層、固定層、電極保護層を積層した構造を有する。検出部は、各記録ビットを構成する磁気記録層の磁化方向の組合せを多値情報として電気的に検出する。

(もっと読む)

マルチフェロイックス素子

【課題】 既に市場で大量に生産されているM(マグネトプラムバイト)型フェライト磁石により、外部磁場で電流を誘起でき、外部磁場で電気分極の強度や方向を制御でき、また、外部電場で誘起した磁化の強度や方向を制御でき、且つ、室温の動作環境温度において動作可能なマルチフェロイックス素子を提供する。

【解決手段】 M(マグネトプラムバイト)型フェライトからなる強誘電性と強磁性を合わせもつマルチフェロイックス固体材料で、室温の動作環境温度において外部磁場を作用させることにより電流を誘起する。例えば、マルチフェロイックス素子は、BaFe12-x-δScx MgδO19(δ=0.05)結晶材料のSc濃度xが1.6から2であるマルチフェロイックス固体材料1とそれを挟むように形成される金属電極2とからなる構造を有し、金属電極2に平行に交流磁界5を印加するように配置され、金属電極2間に誘起される電流を利用する。

(もっと読む)

半導体装置の製造方法

【課題】3次元積層デバイスの歩留まりの向上を図れるリソグラフィ工程を含む半導体装置の製造方法を提供すること。

【解決手段】複数の層を基板上に積層してなる3次元積層デバイスであって、前記複数の層の各々がデバイス回路が含まれたデバイス構造を具備してなる半導体装置の製造方法であって、前記複数の層のリソグラフィ工程に使用され、前記デバイス回路に対応するパターンが互いに同じであり、前記原版の欠陥に基づいた品質、前記原版の前記基板への転写性に基づいた品質、または、前記原版の使用回数に関しての品質が順位付けされた複数の原版のうち、一定以上の品質を有する原版を、下層のリソグラフィ工程に使用し、前記複数の原版のうち、前記一定以上の品質を有する原版を除いた原版を、上層のリソグラフィ工程に使用することを特徴とする。

(もっと読む)

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

導電構造物を含む半導体装置及びその製造方法

【課題】容易に抵抗を調節することができ、高集積化が可能な導電構造物を含む半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に配置され、基板の導電領域を露出させる開口部を含む絶縁膜と、開口部内に配置されるバリア膜パターンと、バリア膜パターン上に配置され、開口部の外部に延長される酸化された部分及び開口部内に位置する酸化されなかった部分を含む導電パターンと、を具備し、導電パターンの幅がバリア膜パターンの厚さによって決定される。

(もっと読む)

情報記憶素子及びその駆動方法

【課題】高い記録密度を実現することができる情報記憶素子を提供する。

【解決手段】連続して形成された導電性の第1の磁性体を含むワード電極1と、第1の磁性体に接して形成された非磁性膜と、第1の磁性体に対して、非磁性膜5を介して接続された第2の磁性体とを含む。そして、ワード電極1の両端部に配置され、ワード電極1の端部の磁化の方向を設定するための磁化設定機構2と、第2の磁性体の保磁力を低減させるための保磁力低減機構と、ワード電極1と交差するように連続して形成された導電性のビット電極3を含む情報記憶素子を構成する。ワード電極1は、第1の磁性体を兼ねていてもよい。ビット電極3は、保磁力低減機構や第2の磁性体を兼ねていてもよい。

(もっと読む)

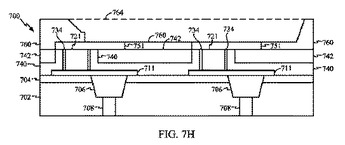

半導体記憶装置

【課題】2つの選択トランジスタと1つの抵抗性記憶素子から成るメモリセルのレイアウト面積を縮小する。

【解決手段】半導体記憶装置は、それぞれが第1および第2のビット線から成り、且つカラム方向に延びる複数のビット線対と、各ビット線対に接続され、且つ複数のメモリセルから成るメモリセル群とを含む。各メモリセルは、第1のトランジスタT1、第2のトランジスタT2および抵抗性記憶素子10から成る。ロウ方向に隣接する2つのビット線対は、第1のビット線同士が共通接続され、もしくは第2のビット線同士が共通接続されて第1のカラムユニットを構成する。少なくとも片側の端部に配置される第1のビット線もしくは第2のビット線は、それと下層との接続部分よりも、第1のカラムユニットの中央寄りに配置される。

(もっと読む)

垂直ナノワイヤを備える情報保存装置

【課題】情報保存装置を提供する。

【解決手段】基板、基板上に垂直に配列された複数のナノワイヤを備え、複数のナノワイヤそれぞれは、情報を保存するための複数のドメインを有するメモリセルアレイ部、基板上に形成され、複数のナノワイヤのうち少なくとも一つを選択するナノワイヤ選択部、基板上に形成され、複数のナノワイヤのうち少なくとも一つに対してドメイン移動動作を制御するドメイン移動制御部、及び基板上に形成され、複数のナノワイヤのうち少なくとも一つに対する読み取り動作及び書き込み動作のうち少なくとも一つを制御する読み取り/書き込み制御部を備えるメモリセルである。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】積層構造を有する柱状の複数のメモリセル間のショート発生を防止した不揮発性半導体記憶装置の製造方法を提供すること。

【解決手段】本発明は、マトリクス状に配置された柱状の複数のメモリセルMCを形成する工程と、直線上に並んだ一群のメモリセルの一方の底面に各々接触し、互いに平行なワードライン47a,47c,47eを形成する工程と、直線上に並んだ一群のメモリセルの他方の底面に各々接触し、互いに平行であり、かつワードラインと同一平面視で交差するビットライン56b,56dを形成する工程とを含み、ワードラインを形成する工程では、複数のメモリセルのうち同じワードラインまたはビットラインに接触する一群のメモリセルの端部に位置する端部メモリセルMCe1,MCe3と所定間隔を隔てて配置され、メモリセルMCと同じ積層構造を有するダミーメモリセルDMC1,DMC2を形成する。

(もっと読む)

スピン注入磁化反転素子、磁気ランダムアクセスメモリ、光変調器、表示装置、ホログラフィ装置、ホログラム記録装置および光変調器の製造方法

【課題】高い垂直磁気異方性を有し、また、熱処理によっても垂直磁気異方性が劣化することのないスピン注入磁化反転素子、このスピン注入磁化反転素子を用いて構成される磁気ランダムアクセスメモリおよび光変調器、この光変調器を用いて構成される表示装置、ホログラフィ装置およびホログラム記録装置、この光変調器の製造方法を提供する。

【解決手段】スピン注入磁化反転素子11は、下地層21と、固定磁化膜層22と、非磁性中間膜層23と、自由磁化膜層24とがこの順序で積層されたスピン注入磁化反転素子構造を有し、固定磁化膜層22と自由磁化膜層24における磁化の方向が膜面に垂直な方向であり、下地層21は、銀膜層であることを特徴とする。

(もっと読む)

半導体集積回路

【課題】リードワード線およびライトワード線のドライブ回路を分割配置してレイアウト面線を減少させる。

【解決手段】

磁性体メモリセルMCは、メモリアレイに行列状に配置される。リードワード線RWL1〜RWLnおよびライトビット線WBL1〜WBLnは、磁性体メモリセルの行に対応して配置される。ライトワード線WWL1〜WWLmおよびリードビット線RBL1〜RBLmは、磁性体メモリセルの列に対応して配置される。この結果、リードワード線ドライバ30rおよびリードワード線ドライバ30wは、メモリアレイに対して異なる方向に隣接するように分割配置することができる。

(もっと読む)

磁気記憶装置

【課題】大容量化が可能な磁気記憶装置を提供する。

【解決手段】第1方向に形成されたアクティブエリア11と、アクティブエリア11上に形成され、抵抗値の変化によってデータを記憶するMTJ素子12と、MTJ素子12の両側のアクティブエリア11上に、第1方向と直交する第2方向に形成されたセルトランジスタT1,T2のゲート電極(ワード線WL)とを備える。さらに、ゲート電極のMTJ素子12と反対側のアクティブエリア11上に形成されたビット線コンタクト13と、MTJ素子12に接続され、第1方向に形成されたビット線BLと、ビット線コンタクト13に接続され、第1方向に形成されたビット線bBLとを備える。MTJ素子12とビット線コンタクト13がゲート電極を間に挟んで交互に配置されている。

(もっと読む)

ショットキーダイオードスイッチおよびそれを含むメモリユニット

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

121 - 140 / 354

[ Back to top ]