Fターム[4M119AA17]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 動作マージンの拡大 (309)

Fターム[4M119AA17]に分類される特許

121 - 140 / 309

薄膜磁性体記憶装置

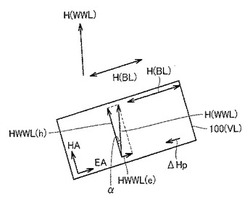

【課題】書込まれる記憶データのレベルに依存せず磁気特性が対称な磁性体メモリセルを有する薄膜磁性体記憶装置を提供する。

【解決手段】トンネル磁気抵抗素子中の自由磁化層においては、静磁性結合に起因する固定磁化層との間の結合磁界ΔHpが、磁界容易軸(EA)に沿った方向に作用している。データ書込磁界H(WWL)は、自由磁化層の磁化困難軸(HA)と完全に平行に印加されるのではではなく、磁化困難軸HAとの間に所定角度αを成すように印加される。これにより、H(WWL)の磁化容易軸(EA)方向に沿った成分によって、一様な結合磁界ΔHpが相殺される。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ、及び磁気記録再生装置

【課題】 大きなMR変化率を有する磁気抵抗効果素子、磁気ヘッドアセンブリ、及び磁気記録再生装置を提供する。

【解決手段】 磁化固着層5と、磁化自由層7と、磁化固着層5と磁化自由層7との間に設けられた非磁性層6と、磁化自由層7の非磁性層6が設けられた側とは反対の側に設けられたAuを含む第1の金属層4と、第1の金属層4の磁化自由層7が設けられた側とは反対の側に設けられたCuNi合金を含む第2の金属層3と第2の金属層3の第1の金属層4が設けられた側とは反対の側に設けられた第1の電極2と、磁化固着層5の非磁性層6が設けられた側とは反対の側に設けられた第2の電極8とを備え、磁化固着層5及び磁化自由層7の一方がハーフメタルを含み、第1の電極2から第2の電極8に向かって電流が流れることを特徴とする。

(もっと読む)

不揮発性記憶素子及びその制御方法

【課題】故障率及び消費電力を充分に小さくすることができる不揮発性記憶素子を提供する。

【解決手段】複数のメモリセルが配列された不揮発性記憶素子100であって、複数のメモリセルのそれぞれは、端子Aと端子Bとを有するインバータ部と、端子Aとビット線140との導通及び非導通を切り替える選択トランジスタ120と、端子Bとビット線141との導通及び非導通を切り替える選択トランジスタ121と、一端が端子Aに接続された固定抵抗130と、固定抵抗130の他端と信号線144との導通及び非導通を切り替える制御トランジスタ122と、一端が端子Bに接続され、固定抵抗130より高抵抗又は低抵抗となることが可能な可変抵抗131と、可変抵抗131の他端と信号線144との導通及び非導通を切り替える制御トランジスタ123とを備える。

(もっと読む)

磁気抵抗記憶素子及び磁気ランダムアクセスメモリ

【課題】書込み電流を低減しつつ、信頼性の高い磁気抵抗記憶素子を提供する。

【解決手段】磁気抵抗記憶素子は、読出し構造体と、読み出し構造体の近傍に設けられた書込み構造体とを具備する。読み出し構造体は、磁化方向が変化する第1のフリー層と、磁化方向が固定された磁化固定層と、第1のフリー層と磁化固定層との間に設けられたトンネル絶縁層とを備える。書込み構造体は、磁化方向が変化する第2のフリー層を備える。第2のフリー層は、第2のフリー層の膜の上面に設けられ、第1方向に磁化が固定された第1の磁化固定領域と、膜の下面に設けられ、第2方向に磁化方向が固定された第2の磁化固定領域とを含む。膜の膜面方向に磁壁が存在する。第1のフリー層と第2のフリー層とは静磁結合している。

(もっと読む)

不揮発磁気薄膜メモリ装置の記録方法

【課題】デバイスの温度が上昇しても、安定的に動作する不揮発磁気薄膜メモリ装置の記録方法を提供する。

【解決手段】不揮発磁気薄膜メモリ装置は、基板と、その基板上に磁気抵抗効果素子を有するメモリセルが二次元状に配されたメモリセルアレイとを有している。不揮発磁気薄膜メモリ装置への情報の記録を行なう前に、メモリセルに情報の試し書きを行ない、試し書きの記録を確認した後、正規のデータを記録する。

(もっと読む)

スピンMOSトランジスタを用いた不揮発性メモリ回路

【課題】MTJ素子を用いた不揮発性メモリ回路では、電源立ち上げ時にMTJ素子の抵抗値によりメモリの記憶内容が決まる。しかしながら、電源電圧が低いときはMOSトランジスタの抵抗が非常に大きいため、MTJ素子の抵抗値の影響が非常に小さい。そのため、電源電圧が低いときにMOSトランジスタの抵抗値のばらつきにより誤動作を引き起こしやすく、高い信頼性が得られない。信頼性の高い不揮発性メモリ回路を提供することを可能にする。

【解決手段】6トランジスタ(11,12,15,16、21,22)で構成されるメモリセルにおいて、トランジスタ12及びトランジスタ16をn型スピンMOSトランジスタとする。

(もっと読む)

磁気抵抗効果素子、それを用いた磁気メモリセル及びランダムアクセスメモリ

【課題】垂直磁化材料を適用し、TMR比の高い磁気抵抗効果素子を提供する。

【解決手段】CoFeB層41/MgOバリア層10/CoFeB層42の外側に融点が1600℃以上の単体金属、もしくはその金属を含んだ合金からなる中間層31,32を挿入する。中間層31,32の挿入により、アニール時におけるCoFeB層の結晶化をMgO(001)結晶側から進行させ、CoFeB層をbcc(001)で結晶配向させる。

(もっと読む)

減電圧の入出力デバイス(REDUCEDVOLTAGEINPUT/OUTPUTDEVICE)を有する抵抗ベースメモリ

減電圧のI/Oデバイスを含む抵抗ベースメモリが開示される。特定の一実施形態では、回路は、第1の抵抗メモリセルおよび第1の負荷トランジスタを含むデータ経路を含む。基準経路は、第2の抵抗メモリセルおよび第2の負荷トランジスタを含む。第1の負荷トランジスタおよび第2の負荷トランジスタは、回路内のコアトランジスタのコア供給電圧と同等の負荷供給電圧で動作するように構成された入出力(I/O)トランジスタである。  (もっと読む)

(もっと読む)

スピンMOS電界効果トランジスタ

【課題】スピン分極率の高いフルホイスラー合金と反強磁性結合を形成する磁性体を含む、TMR比が高い磁気抵抗効果素子を用いたスピンMOS電界効果トランジスタを提供する。

【解決手段】半導体基板10上に形成されたフルホイスラー合金層13と、フルホイスラー合金層13上に形成された、面心立方格子構造を有する強磁性体層14と、強磁性体層14上に形成された非磁性層15と、非磁性層15上に形成された強磁性体層16とを含む構造をソース及びドレインのうち少なくとも一つに備える。非磁性層15を介して形成された強磁性層14と強磁性層16との間には反強磁性結合が形成されている。

(もっと読む)

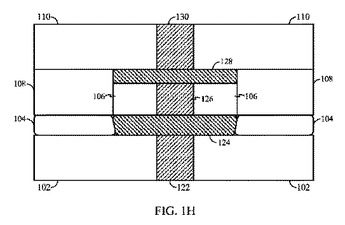

平坦化された電極上の磁気トンネル接合(MTJ)

直接接触を用いた磁気トンネル接合(MTJ)は、より低い抵抗、改善された生産量、及び、より単純な製造を有して製造される。より低い抵抗は、MTJの読み取り方法及び書き込み方法の両方を改善する。MTJ層(126)は、下部電極(124)上に堆積され、下部金属(122)に位置合わせされる。エッチング停止層(302)は、下部金属を囲う絶縁体のオーバーエッチングを防止するために下部金属に隣接して堆積され得る。下部電極は、実質的に平坦な表面を提供するためにMTJ層の堆積前に平坦化される。さらに、下層(202)は、MTJの所望の特性を促進するためにMTJ層の前に下部電極上に堆積され得る。  (もっと読む)

(もっと読む)

垂直磁気トンネル接合構造体並びにそれを含む磁性素子、及びその製造方法

【課題】垂直磁気トンネル接合構造体並びにそれを含む磁性素子、及びその製造方法を提供することである。

【解決手段】本発明の垂直磁気トンネル接合は、上部磁性層及び下部磁性層のうちいずれか1層の磁性層に自由層を含み、トンネリング層と自由層との間に、分極強化層と交換遮断層とが積層されており、該交換遮断層は、非晶質の非磁性層であり、該分極強化層は、Fe層、体心立方(bcc)構造を有するFe系合金層、CoFeB系非晶質合金層、L21型ホイスラ(Heusler)合金層及びそれらの複合層のうちいずれか1層であり、該非晶質非磁性層は、ジルコニウム・ベース非晶質合金層、チタン・ベース非晶質合金層、パラジウム・ベース非晶質合金層、アルミニウム・ベース非晶質合金層及びそれらの複合層のうちいずれか1層であり、また該非晶質非磁性層は、全体的には非晶質であるが、局所的にはナノ結晶構造を有するものでありうる。

(もっと読む)

メモリセル及び磁気ランダムアクセスメモリ

【課題】データ保持安定に優れ、かつ低電流で動作するメモリセル及びそれを用いた磁気ランダムアクセスメモリを提供する。

【解決手段】メモリセルは、磁壁が移動する磁壁移動層と、磁壁移動層の両端部の各々に接続し、両端部のいずれかの近傍で磁壁をトラップする磁化固定層とを具備する。磁壁の移動に伴う磁壁移動層の磁化の向きのスイッチングで情報を記録する。磁化固定層は、磁化固定層に印加する電流又は電圧により磁化、磁気異方性、及び交換結合の少なくとも一つが変化する磁性膜である。

(もっと読む)

高い交換結合エネルギーを有する交換結合膜、それを用いた磁気抵抗効果ヘッド、磁気センサおよび磁気メモリ、並びにその製造方法

【課題】

積層された反強磁性層と固定層からなる交換結合膜、それを有する磁気抵抗効果ヘッド、磁気センサおよび磁気メモリにおいて、反強磁性層と固定層間の交換結合エネルギーを増大し、固定層の磁化の安定性を高める。

【解決手段】

反強磁性層12と固定層13とが積層され、前記反強磁性層12により前記固定層13の磁化方向が一方向に磁気的に固定されている交換結合膜10、それを有する磁気抵抗効果ヘッド、磁気センサおよび磁気メモリにおいて、前記反強磁性層12をMn-X(X=Ir,Rh,Ru)で構成するとともに、前記固定層13の主成分をCo-Fe-Mnで構成する。

(もっと読む)

磁気抵抗効果素子およびそれを用いたセンサ

【課題】 TMR比を大きくすることができるTMR素子およびそれを用いたセンサを実現する。

【解決手段】 TMR素子50を構成するセグメントSG1は、少なくともピンド層43、絶縁層44およびフリー層21を積層して成る第1の積層体20と、少なくともピンド層43、絶縁層44およびフリー層31を積層して成る第2の積層体30とを備える。第1および第2の積層体20,30はピニング層42上に配列されており、かつ、ピンド層43およびピニング層42によって電気的に直列接続されている。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリセルの読み出しディスターブを防ぎ、大電流で高速に読み出す。

【解決手段】 複数のワード線WLと、複数のビット線BLと、複数のメモリセルMCと、選択されたメモリセルから情報を読み出す読み出し回路SA,LAと、読み出し回路SA,LAが読み出した情報に基づいて、選択されたメモリセルに書き換えを行う書き換え回路WD1,WD2とを有し、読み出し回路SA,LAが選択されたメモリセルから情報を読み出す期間は、書き換え回路WD1,WD2が読み出し回路SA,LAが読み出した情報に基づいて選択されたメモリセルに情報を書き込む期間より短い。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】短絡や電流リークを生じさせること無く、しかも、MTJ構造にダメージを生じさせること無く、不揮発性メモリ素子におけるMTJ構造のパターニングを行い得る不揮発性メモリ素子の製造方法を提供する。

【解決手段】第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53が、順次、積層された積層構造体50を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法は、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53を順次形成し、次いで、第2磁性材料層53上にマスク層63を形成した後、マスク層63で覆われていない第2磁性材料層53の部分53’を酸化し、次いで、酸化された第2磁性材料層53の部分53’を還元する工程を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】磁気抵抗素子の短絡不良等が軽減される半導体装置と、その製造方法とを提供する。

【解決手段】メモリセルが形成される層間絶縁膜33において、磁気抵抗素子51が形成されるメモリセル領域Mに位置する層間絶縁膜33の部分の上面の位置が、周辺領域Pに位置する層間絶縁膜33の部分の上面の位置よりも低く形成されている。磁気抵抗素子51を覆うように、層間絶縁膜40が形成されている。その層間絶縁膜40に、磁気抵抗素子に電気的に接続されるビット線41が形成されている。磁気抵抗素子51の直下にディジット線31が形成されている。

(もっと読む)

磁気トンネル接合デバイスおよびその製造方法

【課題】本発明は、磁気トンネル接合デバイスおよびその製造方法に関する。

【解決手段】磁気トンネル接合デバイスは、i)(A100−xBx)100−yCyの化学式を有する化合物を含む第1磁性層と、ii)第1磁性層の上に位置する絶縁層と、iii)絶縁層の上に位置し、(A100−xBx)100−yCyの化学式を有する化合物を含む第2磁性層とを含む。第1磁性層および第2磁性層は垂直磁気異方性を有し、Aおよび前記Bはそれぞれ金属元素であり、CはB(ホウ素)、C(炭素)、Ta(タンタル)、およびHf(ハフニウム)からなる群より選択された一つ以上の非晶質化元素である。

(もっと読む)

磁性媒体の製造法及びスパッタリング装置

【課題】量産時、TMR素子を用いたMARMの完成品間で、MRAMのメモリー特性にバラツキがあり、不良品発生頻度が高かった。このバラツキは、量産時のTMR素子のMR比がウエハー製品間で一定値に維持されず、変動していたことが原因していたので、バラツキを抑制する製造方法を提供する。

【解決手段】高周波成分カットフィルターにより高周波成分をカットした直流電力印加の下で、強磁性体ターゲットをDCスパッタリングすることによってアモルファス状態の強磁性体膜を成膜し、そして酸化マグネシウムターゲットを高周波スパッタリングすることによって結晶酸化マグネシウム膜を成膜する工程及び該工程を実行する制御プログラムを備えた成膜スパッタリング装置200。

(もっと読む)

磁気抵抗メモリ及びその製造方法

【課題】特性の向上、製造コストの低減を可能とする磁気抵抗メモリを提供する。

【解決手段】本発明の例に関わる磁気抵抗メモリは、半導体基板30上に設けられる選択トランジスタ2と、選択トランジスタ2の拡散層23,24上にそれぞれ設けられるコンタクトプラグ50A,50Bと、コンタクトプラグ50Aに電気的に接続される下部電極10と、下部電極10上に設けられる磁気抵抗効果素子1と、磁気抵抗効果素子1上に設けられる上部電極19と、を具備し、下部電極10は、その底面の寸法が上面の寸法より長いテーパー状の断面形状を有し、下部電極10の一端が、コンタクトプラグ50A上面に接触し、磁気抵抗効果素子1は、コンタクトプラグ50Aの直上から半導体基板表面に対して平行方向にずれた位置に設けられている。

(もっと読む)

121 - 140 / 309

[ Back to top ]