Fターム[4M119CC05]の内容

MRAM・スピンメモリ技術 (17,699) | 磁化制御技術 (1,406) | スピン注入磁化反転方式 (781)

Fターム[4M119CC05]に分類される特許

21 - 40 / 781

磁気記憶素子

【課題】書き込み電流を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層12と、記憶層12上に設けられた非磁性層13と、非磁性層13上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層14とを含む。記憶層12の面積は、参照層14の面積より大きく、記憶層12の端部の磁化は、記憶層12の中央部の磁化より小さい。

(もっと読む)

自己参照読み出し操作を使用してMRAMセルに書き込み及びMRAMセルを読み出すための磁気ランダムアクセスメモリ(MRAM)セル及び方法

【課題】磁気トンネル接合を有する磁気ランダムアクセスメモリ(MRAM)セルを提供する。

【解決手段】磁気トンネル接合2は、シンセティック記憶層23、可逆性であるセンス磁化方向211を呈するセンス層21、及びこのセンス層とこの記憶層との間のトンネル障壁層22から構成される。正味の漂遊局所磁界が、前記記憶層を前記センス層に結合させる。前記正味の漂遊局所磁界は、センス層に結合する前記正味の漂遊局所磁界が50エルステッド未満であるような漂遊局所磁界である。また、MRAMセルに書き込み、MRAMセルを読み出すための方法に関する。当該開示されたMRAMセルは、従来のMRAMセルに比べてより低い消費電力で書き込まれ且つ読み出され得る。

(もっと読む)

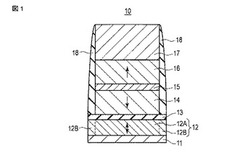

磁気記憶素子

【課題】記憶層に印加される漏れ磁界を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層11と、記憶層11上に設けられた非磁性層12と、非磁性層12上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層13と、参照層13上に設けられた非磁性層14と、非磁性層14上に設けられ、かつ参照層13からの漏れ磁界を低減する調整層15とを含む。調整層15は、界面層16と、膜面に垂直方向の磁気異方性を有する磁性層17とが積層されて構成され、界面層16の飽和磁化は、磁性層17の飽和磁化より大きい。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

磁気メモリ及びその製造方法

【課題】低コストで広帯域の読出方式の、磁壁で区切られた磁区毎に情報が記録された磁

性配線を有する磁気メモリを提供する。

【解決手段】磁区、及び前記磁区を仕切る磁壁を有する第1磁性細線と、前記第1磁性細

線の両端部に配置される電流導入用電極と、前記第1磁性配線に隣接して設けられる書き

込み部と、前記第1磁性配線に交差するように設けられる第2磁性細線と、前記第2磁性

配線の一端部に設けられるスピン波発生部と、前記第2磁性配線の他端部に設けられるス

ピン波検出部とを備える。

(もっと読む)

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

スピントランジスタおよびメモリ

【課題】IDP/IDAP比を高めることのできるスピントランジスタおよびメモリを提供する。

【解決手段】本実施形態によるスピントランジスタは、基板上に形成されたソース/ドレインの一方となる第1磁性層と、前記第1磁性層上に設けられチャネルとなる絶縁膜と、前記絶縁膜上に設けられ前記ソース/ドレインの他方となる第2磁性層と、前記絶縁膜の側面に設けられたゲート電極と、前記ゲート電極と前記絶縁膜の前記側面との間に設けられたゲート絶縁膜と、備えている。

(もっと読む)

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路

【課題】 本発明の実施形態によれば、単方向電流で書き込みが可能であり、微細化が可能な磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路を提供することができる。

【解決手段】 磁気メモリ素子は、磁化が可変の第1の強磁性層と、第1のバンド及び第2のバンドを有する第2の強磁性層と、前記第1の強磁性層と前記第2の強磁性層との間に設けられた非磁性層と、を備える。

(もっと読む)

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

スピン伝導素子

【課題】外部磁場が半導体チャンネルに侵入することに起因するノイズやエラーを抑制することが可能なスピン伝導素子を提供すること。

【解決手段】磁気抵抗を利用したスピン伝導素子1は、スピンを半導体チャンネルに注入するための第一強磁性体12Aと、スピンを半導体チャンネルから抽出するための第二強磁性体12Bと、第一強磁性体12Aから第二強磁性体12Bまで延びる半導体チャンネル7と、第二強磁性体12B、及びあるいは、半導体チャンネル7を覆う磁気シールドS1と、第二強磁性体12B、及びあるいは、半導体チャンネル7と磁気シールドS1との間に設けられた絶縁膜と、を備えることを特徴とする。

(もっと読む)

磁気メモリ

【課題】磁気記録層の強磁性体膜が強い垂直磁気異方性を有する磁気メモリを提供する。

【解決手段】磁気メモリは、強磁性体の下地層51と、下地層51上にの第1非磁性52と、第1非磁性52上の垂直磁気異方性を有する強磁性体のデータ記憶層53と、第2非磁性層20を介してデータ記憶層53に接続された参照層30と、下地層51の下側に接した第1、第2磁化固定層41a、41bとを具備する。データ記憶層53は、反転可能な磁化を有し参照層30とオーバーラップする磁化自由領域13と、磁化自由領域13の端に接続され、第1磁化固定層41aに+z方向に磁化固定された第1磁化固定領域11aと、磁化自由領域13の他の端に接続され、第2磁化固定層41bに−z方向に磁化固定された第2磁化固定領域11bとを備える。磁化自由領域13下の第1非磁性52は、第1、第2磁化固定領域11a、11b下の第1非磁性52よりも厚い。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

磁気メモリ

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気メモリは、第1領域内の第1の磁気抵抗効果素子1Aと、第2の領域の磁気抵抗効果素子1Xとを含む。第1の磁気抵抗効果素子1Aは、磁化の向きが可変な第1の記憶層10と、磁化の向きが不変な第1の参照層12と、非磁性層11と、第1のシフト調整層13と、を含む。第2の磁気抵抗効果素子1Xは、磁化の向きが可変な第2の記憶層10と、磁化の向きが不変な第2の参照層12と、第2の非磁性層11と、第2のシフト調整層13Xと、を含む。第2のシフト調整層13Xの膜厚t2は、第1のシフト調整層13の膜厚t1以下である。

(もっと読む)

不揮発性抵抗変化素子を含む半導体集積回路とその動作方法

【課題】出力値を変化させる不揮発性抵抗変化素子の状態を、出力動作を止めることなく変化させることができる集積回路を提供する。

【解決手段】不揮発性抵抗変化素子(10)の抵抗を変化させるための書き込み端子(11)と、該抵抗を読み出すための読み出し端子(12)とを別々に有し、電気的にカップリングしていない該書き込み端子と読み出し端子とを用いて書き込み動作と読み出し動作を同時にできる不揮発性抵抗変化素子を有する回路を含む集積回路(50)である。該回路には該不揮発性抵抗変化素子の抵抗値に応じた出力値を出力する出力端子(22)と、該抵抗値を変化させる入力端子(11)を少なくとも有する。該出力端子からの出力の一部を、該入力端子に帰還させることができる。

(もっと読む)

不揮発性記憶装置

【課題】安定した動作が可能な不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、磁気記憶素子と制御部とを備えた不揮発性記憶装置が提供される。磁気記憶素子は積層体を含む。積層体は第1積層部と第2積層部とを含む。第1積層部は、磁化が固定された第1強磁性層と、磁化の方向が可変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、通電される電流によって磁化が回転して発振が生じる第3強磁性層と、磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。制御部は、第2強磁性層の磁化の向きに応じた第3強磁性層の発振の周波数の変化を検出することで、第2強磁性層の磁化の向きを読み出す読み出し部を含む。

(もっと読む)

磁気記憶素子及び不揮発性記憶装置

【課題】安定した動作が可能な磁気記憶素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1、第2積層部を含む磁気記憶素子が提供される。第1積層部は、第1強磁性層/第1非磁性層/第2強磁性層を含む。第1強磁性層の磁化は面直に固定され、第2強磁性層の磁化方向は面直に可変である。第2積層部は、第3強磁性層/第2非磁性層/第4強磁性層を含む。第3強磁性層の磁化方向は面内方向に可変であり、第4強磁性層の磁化は面直に固定されている。第3強磁性層の位置での第1、第2、第4強磁性層からの漏れ磁界Hs、第3強磁性層の磁気異方性Ku、ダンピング定数α、磁化Ms及び反磁界係数Nzは、Ku≦αMs(8πNzMs−Hs)を満たす。電流によりスピン偏極した電子と、第3強磁性層で発生する回転磁界と、を第2強磁性層に作用させ、第2強磁性層の磁化方向を決定できる。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

21 - 40 / 781

[ Back to top ]