Fターム[5B018MA01]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | 主記憶 (273)

Fターム[5B018MA01]に分類される特許

101 - 120 / 273

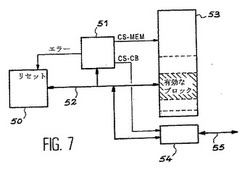

過渡エラー制約を受ける電子システムのためのメモリアクセス監視装置

【課題】過渡エラー制約を受ける電子システム用の処理手法を提案し、過渡エラーの様相を検出し、それらを修正することである。

【解決手段】本発明は、過渡エラー制約を受ける電子システムの処理手順に関し、単一物理チャネルにある二つの仮想チャネルが所定のリアルタイムサイクルでタイミングよく多重化され(使用の前に票決できるように、仮想チャネルの各実行から生じるデータは記憶されている)、エラーが検出された場合には、処理中のリアルタイムサイクルは禁止され、再ロードされたコンテキスト始まる次のサイクルの仮実行からなる再開始を行うように異常のないコンテキストが再ロードされる。本発明は、また、メモリアクセスの監視装置にも関する。

(もっと読む)

売上データ処理装置及びプログラム

【課題】売上データ処理装置において、主電源遮断時のデータのバックアップに使用される補助電源の消耗を低減させる。

【解決手段】本発明に係るECRによれば、CPU10は、他に実行すべき処理のない空き時間にハイバネーション用メモリ14に記憶されているデータの消去処理を実行し、AC電源31からの電源供給が遮断された際に、補助電源からの給電によりハイバネーション用メモリ14に記憶されている未消去の残存データの消去処理を実行しメインメモリ13に記憶されているデータをハイバネーション用メモリ14に退避させる。

(もっと読む)

情報処理システム、システムコントローラ及びメモリ制御方法

【課題】XDR DRAMを用いた情報処理システムにおけるSTR処理の所要時間を短縮する。

【解決手段】XDR DRAM13はRST(リセット)信号入力に応じてデータリセットを行うDRAMである。システムコントローラ11は、システムの初回の電源投入の際に、メモリコントローラ12からレベルシフタ24を介して入力されるRST信号に応じて、XDR DRAM13に対してリセット信号を出力し、XDR DRAM13をリセットする。XDR DRAMに格納されたデータを保持したままシステムの電源を切る場合、システムコントローラ11は、メモリコントローラ12からレベルシフタ24を介して入力されるRST信号に応じて、XDR DRAM13の電源投入を維持しながら、メモリコントローラ12の電源を切る。

(もっと読む)

情報処理装置

【課題】拡張カードを有する情報処理装置において、拡張カードにデータを読み書きする際にエラーが発生した場合、エラーの原因を特定して、復旧不可能な重大な傷害に発展する前に処置できる、高い信頼性と可用性を保障する。

【解決手段】情報処理装置は、外部で検出されたエラー情報が書き込まれるエラー格納領域、および内部で検出されたエラー情報が書き込まれるエラーレジスタを備えた拡張カードと、前記拡張カードにデータを読み書きする際にエラーを検出すると、前記拡張カードのエラー格納領域にエラー情報を書き込み、該エラーを外部に通知するプロセッサと、前記プロセッサからエラーが通知されると、前記拡張カードのエラー格納領域に書き込まれたエラー情報、および前記拡張カードのエラーレジスタに書き込まれたエラー情報を採取して記録する保守プロセッサを有する。

(もっと読む)

誤り判定回路及び共有メモリシステム

【課題】誤り判定回路及び共有メモリシステムにおいて、システムのコストを増加させることなく主記憶メモリの領域の利用効率を向上してデータ保証を行う。

【解決手段】P(x)をガロア体GF(2)上のm次の原始多項式とし、(k,k−3)リード・ソロモン符号を用いたSmEC−DmEDにおいて、mビットブロック単位のデータに対し、誤りから保護するべき対象である元符号の多項式表現I(x)に対し、1ブロックの誤り、2ブロックの誤り、或いは、誤りがないことを検出すると共に、ブロック誤りの位置pを前記ガロア拡大体GF(2m)上でS0αp=S1から検出する誤り検出回路部を備えるように構成する。

(もっと読む)

電子機器、及び印刷装置

【課題】クロックに同期してデータを読み書きするRAMを備えるメモリを備え、このメモリとの相性を客観的に判断することが可能な電子機器、及び印刷装置を提供する。

【解決手段】クロックに同期して出力される信号により所定のデータを読み書きするRAMと、信号の出力タイミングを変更させつつ出力して、RAMに対するアクセスを制御するメモリ制御部と、信号の出力タイミングを所定周期で変化させることで、出力タイミングの変化毎に前記信号が前記RAMに対して正常に機能するか否かを判断する判断部と、判断結果を用いて、RAMとの相性を視覚可能に出力する出力部とを有する。

(もっと読む)

不揮発性メモリを主記憶に用いた装置

【課題】主記憶が全て不揮発性メモリで構成された場合において、突発的な電源の遮断が発生すると電源再投入時にシステムが正常に動作を再開できない。

【解決手段】装置は、電源異常遮断判定部と、電源異常終了通知レジスタとを備え、電源異常遮断判定部は、装置の電源投入時に、電源異常終了通知レジスタを参照し、電源異常終了通知レジスタが装置の電源が異常に遮断されたことを示す情報を格納しており、プロセッサが不揮発性のプロセッサでない場合、装置の電源が遮断される前に実行されていたプロセスを再起動し、デバイスドライバを確認し、電源異常終了通知レジスタが装置の電源が異常に遮断されたことを示す情報を格納しており、プロセッサが不揮発性のプロセッサである場合、装置の電源が遮断される前に実行されていたプロセスを、プロセスが中断された処理から再開し、デバイスドライバを確認することを特徴とする。

(もっと読む)

コンピュータ装置、プロセッサ診断方法、及びプロセッサ診断制御プログラム

【課題】プロセッサの不良機能を確実に特定して、各種の診断テストの正常な実行を担保すること。

【解決手段】第1のプロセッサと、第2のプロセッサと、メインメモリとを有するコンピュータ装置であって、第2のプロセッサによりメモリ診断プログラムを実行させることにより、メインメモリを診断し、メインメモリ内の不良領域を特定するメモリ診断手段と、メインメモリのうち、メモリ診断手段により特定された不良領域を除く領域に、第1のプロセッサの有する複数の機能を診断するためのプロセッサ診断プログラムを展開する診断プログラム展開手段と、展開されたプロセッサ診断プログラムを第2のプロセッサにより実行させることにより、第1のプロセッサの有する複数の機能のうち、実行不能な機能である不良機能を特定する不良機能特定手段と、を有する。

(もっと読む)

メモリの誤り訂正方法,誤り検出方法、及びそれを用いたコントローラ

【課題】

メモリとの接続故障の誤り訂正,検出方法が必要になってきた。

【解決手段】

プロセッサと、メモリ制御装置と、メモリ装置とを備えたコントローラにおいて、アドレスに対して任意のデータをライトアクセスするとき、アドレスと任意のデータから決定される誤り検出符号CRCと、誤り検出符号CRCと任意のデータから決定される誤り訂正符合ECCを生成し、任意のデータと伴に誤り検出符号CRCと誤り訂正符号ECCをメモリ装置に書き込み、プロセッサが任意のアドレスに対してリードアクセスするとき、メモリ装置に書き込まれている誤り訂正符号ECCと、誤り検出符号CRCとデータを読み出し、読み出した誤り訂正符号ECCに基づき読み出した誤り検出符号CRCと読み出したデータの誤りを訂正し、訂正された誤り検出符号CRCと読み出したデータに誤りが有るか検出する。

(もっと読む)

セキュアメモリインターフェース

【課題】セキュアメモリインターフェースを提供すること。

【解決手段】セキュアメモリインターフェースは、セキュアモードが活性化された場合に、メモリ装置に対する欠陥注入を探知するように読出部、書込部、及びモード選択部を含む。モード選択部は、データプロセッシング部から生成されたメモリアクセス情報を使用してセキュアモードを活性化または非活性化する。従って、データプロセッシング部はメモリ装置に保存されたセキュアデータの量と位置を柔軟に指定することができる。

(もっと読む)

半導体装置

【課題】メモリへの書き込みにエラーが発生しても、書き込もうとしたデータが消失することを防ぐことのできる半導体装置を提供する。

【解決手段】キャッシュメモリ1が、キャッシュロック機能と主メモリへの書き込み時にそのデータを有するキャッシュラインをロックする機能を有し、書き込み履歴バッファ2が、キャッシュメモリ1から主メモリ200への書き込みが行われたキャッシュラインの情報を記憶し、メモリコントローラ3が、キャッシュメモリ1から主メモリ200への書き込み時のエラー発生有無を検証して書き込み検証信号を出力し、キャッシュロック制御部4が、書き込み検証信号が主メモリ200への書き込みが正常であることを示すときは、書き込み履歴バッファ2に記憶されているライン情報を検索して、書き込みを行おうとしたデータが格納されているキャッシュラインを特定し、そのキャッシュラインのロック解除をキャッシュメモリ1へ要求する。

(もっと読む)

デュプレックスプロセッサシステム及びプロセッサ二重化方法

【課題】開示のシステムは、復旧に要する時間を短縮することを目的とする。

【解決手段】現用系プロセッサと予備系プロセッサそれぞれにCPUと主メモリを有し、現用系プロセッサで障害が発生すると再開起動手段を起動して障害要因に応じた再開方法を選択し再開起動を行うデュプレックスプロセッサシステムにおいて、再開起動手段は、現用系プロセッサの主メモリから読み出したデータのエラー訂正及び検出符号で訂正不能な誤りの検出時に、当該データを予備系プロセッサの主メモリから読み出して現用系プロセッサの主メモリに書き込んで修復するメモリ修復手段を有し、メモリ修復手段で現用系プロセッサの主メモリのデータを修復したのち障害要因に応じた再開方法を選択して再開起動を行う。

(もっと読む)

メモリパトロール障害検出システム、メモリパトロール検出障害報告抑止方法、BMC、及び集積回路

【課題】 OSが切り離したページにおけるメモリパトロールで検出された障害による障害通報/通知を抑止する。

【解決手段】 訂正可能障害が発生したページに対するアクセスが、通常アクセスであるか否かを検出する検出手段と、該ページが、OSにより切り離されたものであるか否かの判定を、検出手段による検出結果にもとづいて行う切り離し判定手段と、障害が発生したことを保守部門における情報処理装置へ通報し、及び/又は、OSへ通知する報知手段とを有し、切り離し判定手段が、該障害が発生したときに、該ページがOSにより既に切り離されたページであるか否かの第一の判定を行い、該障害がメモリパトロールにより検出された障害であるか否かの第二の判定を行い、該ページがOSにより既に切り離されたページであり、かつ、該障害がメモリパトロールにより検出された障害の場合、報知手段が、障害が発生したことの通報及び通知を抑止する。

(もっと読む)

ファイルサーバシステム及びファイルサーバシステム起動方法

【課題】ファイルサービス提供に必要なメモリ容量のみをシステムブート時のメモリテスト対象とすることによって、メモリテスト時間を最少化し、ファイルサーバのシステムブート時間を短縮する。

【解決手段】ホスト計算機にファイルサービスを提供するファイルサーバであって、前記ファイルサービスを提供するために必要な前記メモリの記憶領域の容量を計算し、前記計算された容量の記憶領域をテストする第1メモリチェックを実行し、前記第1メモリチェックが完了した後、前記メモリの残りの記憶領域をテストする第2メモリチェックを実行し、前記第1メモリチェックが完了した後、前記第2メモリチェックが完了する前に、前記ファイルサービスの提供を開始する。

(もっと読む)

情報処理装置

【課題】情報処理装置においてエラーが生じた場合に、充分なエラー対応を行なうことができるようにする。

【解決手段】メモリ16においてエラーが生じた際に、複数のプロセッサ10のうちの一のプロセッサ10aが一のメモリ16aに格納されたエラー対処プログラム20aを実行し、一のプロセッサ10aがエラー対処プログラム20aを正常に動作させることができない場合に、他のプロセッサ10bが一のメモリ16aとは異なる他のメモリ16bに格納されたエラー対処プログラム20bを実行する。

(もっと読む)

メモリテスト回路及びメモリテスト方法

【課題】メモリテスト専用領域を設けずに、かつ、コンピュータシステム稼働中にメモリテストを実行することが可能なメモリテスト回路を提供する。

【解決手段】メモリテストの対象であるテスト対象メモリ領域11cを有し、アレイテスト回路20から出力される第1のテストパターンをテスト対象メモリ領域11cに書き込むメモリアレイ部11と、テスト対象メモリ領域11cに記録されているデータの退避先となるリダンダントアレイ部12と、退避領域アドレス情報及び、第1のテストパターンをメモリアレイ部11に出力し、メモリアレイ部11に書き込まれた後、メモリアレイ部11から出力される第2のテストパターンとを比較するアレイテスト回路20と、メモリテスト開始信号をアレイテスト回路20に出力する演算回路30からなることを特徴とする。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されたエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するシステム、方法および装置を提供する。

【解決手段】メモリ・システムは、ホストとメモリ・デバイスとの間でデータを転送するためにデータ・フレームを使用する。システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

多重化処理を行う制御装置

【課題】記憶装置のエラーの潜在、比較装置の故障の潜在を防止でき、ソフトエラー発生の際は動作継続が可能となり、システムとして、稼働率を向上する。

【解決手段】プロセッサの多重化構成により実現されている高信頼性制御装置において、記憶装置のソフトエラー、又は固定エラーによる記憶装置のエラーの潜在を防止すると共に、ソフトエラーによる1ビットエラー発生時はデータを訂正し動作を継続し、稼働率向上を行う。

(もっと読む)

情報処理装置およびデータ整合性検査方法

【課題】 サスペンド時に主記憶に格納されていたデータのレジューム時における整合性の検査を効率的に行うことを実現した情報処理装置を提供する。

【解決手段】 CPU101は、サスペンド・レジューム機能が有効な状態で電源オフされた場合、RAM103に配置されたページ内のデータへのアクセス時にページフォルト割り込みを発生させるための設定処理を行う。そして、電源オン後、RAM103に配置されたページ内のデータへのアクセス時にページフォルト割り込みが発生した場合に、当該ページ内のデータの整合性を検査し、整合性を有する場合、当該ページ内のデータへのアクセス時にページフォルト割り込みを発生させないための解除処理を行う。

(もっと読む)

データ処理装置、メモリコントローラ及びそのアクセス制御方法

【課題】従来のデータ処理装置では、部分データの書き込み動作において動作速度を十分に高速化することができなかった。

【解決手段】本発明にかかるデータ処理装置は、所定のデータ幅のデータで入出力を行うメモリ20と、リード命令又はライト命令を出力してメモリ20に対してアクセスを行う演算回路10と、演算回路10からライト命令とそのライト命令に関連付けられた部分データとを受けた場合に、メモリ20から読み出した第1のリードデータの一部を部分データに置き換えてメモリ20に対するライトデータを出力するアクセス制御回路30と、を有し、アクセス制御回路30は、ライト命令がそのライト命令よりも前に出力されたリード命令に対応して出力されたものである場合は、第1のリードデータに代えて以前に出力された前記リード命令に応じてすでに取得されている第2のリードデータの一部を部分データに置き換えてライトデータを出力する。

(もっと読む)

101 - 120 / 273

[ Back to top ]