Fターム[5B018MA01]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | 主記憶 (273)

Fターム[5B018MA01]に分類される特許

81 - 100 / 273

ソフトエラー検出回路を備える制御装置

【課題】スリープモード中にレジスタ等にソフトエラーが生じても、異常動作を回避する。

【解決手段】マイコン2の動作に重要な意味をもつ情報が格納される保持回路16と、保持回路17とは、多重化された格納回路を提供する。これら保持回路16、17には、同じ情報が書き込まれ、格納される。マイコン2がスリープモード中に、ソフトエラーなど何らかの理由により保持回路16、17に不一致が生じることがある。この場合、EXORゲート18、ANDゲート15、およびORゲート12を介して、ウェイクアップ信号がマイコン2に与えられる。マイコン2は、臨時的に通常モードに復帰し、保持回路16、17を再設定する。この結果、保持回路16、17のソフトエラーによるマイコン2の異常動作を回避することができる。

(もっと読む)

記憶制御装置及び画像形成装置

【課題】第1の記憶手段の動作状態が異常である場合に、入力されたデータを第1の記憶手段に代えて第2の記憶手段に記憶させるタイミングを、そのデータの重要度に応じて制御する。

【解決手段】CPUは、記憶部の動作状態に異常があると判定した場合、自装置の処理の履歴における処理の頻度に基づいて、入力されたデータをRAMの代替記憶領域に記憶させる処理の期間である代替期間を決定し、データに対して特定される各々の重要度について、決定された代替期間においてその重要度以上の重要度のデータを代替記憶領域に記憶させる処理を許可する代替許可期間を設定する。そして、記憶部の動作状態に異常があると判定した後に、新たなデータが入力されると、データの入力されたタイミングがそのデータの重要度に対応する代替許可期間内である場合には、入力されたデータをRAMの代替記憶領域に記憶させる。

(もっと読む)

半導体装置及び電子機器

【課題】動作時間を短縮しつつ、半導体記憶装置のデータを修正する半導体装置及び電子機器を提供すること。

【解決手段】選択回路8は、CPU2及び誤り訂正回路5と、第1及び第2メモリMe1,Me2との間に配置される。選択回路8は、アドレスデータDaに基づいて、CPU2に指定された一方の第1又は第2メモリMe1,Me2に対応するメモリ書き込みデータDwmを第1又は第2メモリ書き込みデータDwm1,Dwm2として出力し、CPU2に指定されていない他方の第1又は第2メモリMe1,Me2に対応する訂正メモリデータDmtを第1又は第2メモリ書き込みデータDwm1,Dwm2として出力する。

(もっと読む)

圧縮情報を利用した故障検出装置、その方法及びそのプログラム

【課題】圧縮情報を活用することで、分散メモリ・I/O構成及び共有メモリ・I/O構成で、高速かつ高信頼に故障を検出する。

【解決手段】複数の演算処理装置と、当該演算処理装置が情報の入出力を行うための分散メモリ・I/Oと、当該演算処理装置のそれぞれ及び当該分散メモリ・I/Oに接続されている複数の比較圧縮手段と、を備え、前記複数の比較圧縮手段が、前記演算処理装置と前記分散メモリ・I/Oがやり取りする情報を圧縮し、前記複数の比較圧縮手段相互間で当該圧縮した情報を交換及び比較し、比較結果が不一致の場合に、前記複数の演算処理装置の何れか或いは全てが故障していると判断する。

(もっと読む)

メッセージキュー制御プログラム、メッセージキューイングシステム及びメッセージキューイングシステムの制御方法

【課題】キューを揮発性の記憶領域上に確保して処理速度を上げ、任意の時点で待ち時間なくキューを停止できるメッセージキューイングシステムを提供する。

【解決手段】メッセージキューイングシステムは、メッセージの受信に応じて形成するキューを揮発性記憶装置31、不揮発性記憶装置33のいずれかを用いて管理するか判定を行い、当該判定によって、キューの管理に用いる記憶装置が揮発性記憶装置31であると判定された場合は、受信メッセージを揮発性記憶装置31を用いて管理し、キューの停止指示に応じて、揮発性記憶装置31のキューイングされたメッセージを不揮発性記憶装置33に退避させてから停止し、当該判定によって、キューの管理に用いる記憶装置31が不揮発性記憶装置33であると判定された場合は、キューの停止指示に応じて、揮発性記憶装置31のキューイングされたメッセージを不揮発性記憶装置33に退避させる処理を経ずに停止する。

(もっと読む)

情報処理装置

【課題】不揮発性メモリのアクセス速度や装置への過負荷等といった性能面への影響を低減可能とする。

【解決手段】ブート実行手段320は、各種制御プログラム101i〜103iをロードエリア210にロードし、かつ照合用エリア220に対して制御プログラム101iのイメージ1010iをコピーする。照合復旧・前処理プログラム102iは、制御プログラム101iのイメージと照合用エリア220上の同イメージ1010iを照合する。一致する場合に制御プログラム101iを実行させる。相違がある場合に不揮発性メモリ100上の制御プログラム101iのイメージをロードエリア210に再ロードし、照合用エリア220上にコピーし、制御プログラム101iを実行させる。その後、照合復旧・後処理プログラム103iは、再度照合処理を実行し、一致する場合に照合復旧・前処理プログラム102i+1を実行させる。

(もっと読む)

情報処理装置

【課題】セルフリフレッシュ機能を有するSDRAMを備える複合機において、消費電力の低減のためにプロセッサを停止させる省電力モードから、通常動作モードへの移行にかかる時間を短縮する。

【解決手段】プロセッサ32は、停止が解除された時及び電源投入時に初期動作プログラムを実行する。プロセッサ32は、初期動作プログラムに基づいて、SDRAM34のセルフリフレッシュモードを解除し、プロセッサ32による外部リフレッシュに切り替える。プロセッサ32は、初期動作プログラムに基づいて、SDRAM34内に通常動作プログラムが正しく保持されていることを確認する。SDRAM34内に通常動作プログラムが正しく保持されていない場合は、プロセッサ32は、初期動作プログラムに基づいて、フラッシュメモリ33内の初期動作プログラムをSDRAM34内に転送する。

(もっと読む)

メモリ制御装置及び制御方法

【課題】消費電力を低減させるとともに、信号品質を維持することが可能なメモリ制御装置及び制御方法を提供すること。

【解決手段】本発明の一態様に係るメモリ制御装置は、ODT(On Die Termination)機能を有する複数のメモリ素子に接続可能なメモリ制御装置であり、診断装置2、メモリ終端抵抗制御部7、ECC回路8を備える。メモリ終端抵抗制御部7は、複数のメモリ素子毎にODTを使用とするか未使用とするかを制御するためのODT制御信号を出力するECC回路8は、複数のメモリ素子から送出されるデータのエラーを検出する。診断装置2は、システム運用中において、ODT使用状況及びエラーの情報に基づいて、複数のメモリ素子のODT使用設定を切り換える。

(もっと読む)

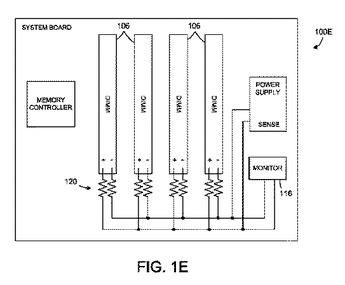

電圧センス監視インターフェースを備えたメモリモジュール

メモリデバイス及びシステムは、可変負荷にわたる電圧許容誤差に対処するための電圧センスラインを含む。該メモリデバイス及びシステムは、メモリモジュール上の回路構成に結合された第1の複数ピンと、該メモリモジュール上の電力レールに結合された第2の複数ピンとを有したメモリモジュールコネクタを備える。該第2の複数ピンは、外部から該メモリモジュールへの該電力レールの監視を可能にする。  (もっと読む)

(もっと読む)

計算機システム

【課題】マルチコアCPUモジュールを搭載し、メインCPU上で動作しているアプリケーション処理を中断することなく、サブCPUでメモリ診断を行う計算機システムを得る。

【解決手段】計算機システム1は、マルチコアCPUモジュール4を搭載し、メインCPU2とサブCPU3上で、それぞれ、OS1とOS2が動作し、OS1はアプリケーション11と障害対処処理を行う障害対処処理部14を動作させ、OS2は、定期的にメモリ5の診断を行うメモリ診断処理部13と、メモリ診断処理部13の診断結果を障害対処処理部14に通知する障害監視処理部12とを動作させ、障害対処処理部14は、メモリ障害の通知を受けると、計算機システム1を停止させるようにする。

(もっと読む)

半導体記憶装置及びその自己テスト方法

【課題】テストコストの低減に対して有利な半導体記憶装置及びその自己テスト方法を提供する。

【解決手段】半導体記憶装置は、不揮発性メモリ11と前記不揮発性メモリの入出力データを格納するバッファ13とを備える主記憶部1と、揮発性メモリを備える前記主記憶部のバッファ部2と、データ入出力ピンを有する自己テストインターフェイス50と、前記主記憶部と前記バッファ部とを制御する制御部30とを具備し、前記制御部は、前記データ入出力ピンを介して自己テストインターフェイスから前記バッファへデータを格納し(S1)、前記バッファの格納データを、前記揮発性メモリへ書き込み(S2)、前記揮発性メモリから読み出したデータを前記バッファへ格納し(S4)、前記バッファの格納データを前記自己テストインターフェイスから読み出し、判定させる(S5)。

(もっと読む)

データプロセッサ

【課題】データプロセッサにおいて複数のメモリに対して共通のメモリパトロール回路を用いることができるようにする。

【解決手段】読み出しデータに対して誤り訂正を行って出力するメモリ(2)をCPU(1)の制御に従って定期的にリードアクセスすることによって前記メモリが保持するデータに対するメンテナンスを支援するメモリパトロール回路(4)を有する。メモリパトロール回路はCPUが接続するバス(SBUS)を介してメモリに接続され、メモリに対して一対一対応の密結合とはされていない。メモリパトロール回路によるパトロール動作の範囲はCPUの設定によって決まり、前記メモリからエラーの通知を受取ったときは当該エラーに係るデータのアドレスをメモリパトロール回路の記憶回路(41)に保持すると共に、例えばエラーフラグ格納領域(44)にエラーフラグをセットし、或いはCPUに割り込みを要求する。

(もっと読む)

画像形成装置

【課題】エラー発生時のダウンタイム、サービスコール数、ユーザーの手間を低減しつつ、リブート後にリブート前の処理をスムーズに再開する。

【解決手段】CPU12もしくはDMAC11bは処理対象データーをRAM13に記憶させる際にRAM13に記憶された処理対象データーのスタートアドレスとサイズ情報を領域レジスタ11cに記憶させ、所定条件により自動リブートを行う際に、CPU12は上記スタートアドレスとサイズ情報に基づきRAM13の処理対象データーを記憶された領域についてRAMテストを行わずにリブートし、CPU12はリブート完了後に上記スタートアドレスとサイズ情報に基づき処理対象データーを特定して該処理対象データーの処理を行う。

(もっと読む)

コンピュータ装置、データ記憶方法、および、記憶処理プログラム

【課題】揮発性記憶部に、一定期間の間、データを一定に保持するために必要な処理が行われなくても、当該揮発性記憶部に記憶されたデータの消失を防止可能な技術を提供することを目的とする。

【解決手段】コンピュータ装置1は、DRAM4と、保持能力値取得部6と、個数決定部7と、制御部8とを備える。保持能力値取得部6は、DRAM4の保持能力値を決定する。個数決定部7は、保持能力値に基づいて、記憶対象のデータが、DRAM4に記憶されるべき個数を決定する。制御部8は、記憶対象のデータを、個数決定部7で決定した個数だけDRAM4に記憶する。

(もっと読む)

メモリ装置および計算機

【課題】プログラムとデフラグとを並行して実行した場合に、不揮発性メモリに格納されたデータに発生する不整合を未然に防止する。

【解決手段】メモリとデフラグ部とメモリ保護部とバッファメモリとCPUとMMUとが接続され、バッファメモリは、デフラグのコピー元とコピー先とのメモリのアドレスとコピー先フラグとを含み、デフラグ部は、デフラグ部の状態フラグを備え、メモリページ切り替えのタイミングで、デフラグのコピー元とコピー先とのメモリのアドレスをバッファメモリに格納しデフラグし、メモリ保護部は、CPUからメモリの参照または更新の命令と対象メモリのアドレスを受信し、状態フラグが非アイドル状態の場合、デフラグのコピー元とコピー先と、コピー先フラグと、命令と、命令の対象アドレスとに基づいて、参照または更新の命令の対象アドレスを再決定するか、CPUに失敗を通知する。

(もっと読む)

情報処理装置及びプロセッサ並びに情報処理方法

【課題】情報処理装置について、装置構成を複雑化させることなく、動作の高速化と高信頼性を実現する。

【解決手段】本発明の一例である情報処理装置1は、プロセッサ2と、プロセッサ2に使用される不揮発性メモリ3と、プロセッサ2から不揮発性メモリ3への書き込みが発生した場合に、書き込み位置の重複回数を抑えるために当該書き込み位置がずれるように書き込みアドレスを発生させるアドレス発生手段16と、書き込みの新しさを表わす順序情報19を発生させる順序発生手段17と、アドレス発生手段16によって発生された書き込みアドレスに対して、順序発生手段17によって発生された順序情報19を対応付けて、書き込み情報21を記憶する書き込み制御手段18とを具備する。

(もっと読む)

制御装置および制御方法

【課題】故障を即時かつ確実に検出して不安定な状態で処理し続けることを阻止する。

【解決手段】第一プロセッサが所定のプログラムを実行した結果として出力する第一情報から第一誤り検出符号を生成する。そして、第一プロセッサと同一の演算結果を出力するべく構成されている第二プロセッサがプログラムを実行した結果として出力する第二情報から第二誤り検出符号を生成する。そして、第一情報と第二情報が同一であるか否かを検出するとともに、第一誤り検出符号と第二誤り検出符号が同一であるか否かを検出し、検出の結果に基づいて第一情報あるいは第二情報のメインメモリへの書き込みを制御する。

(もっと読む)

メモリシステムを監視するシステムおよび方法

メモリボールトと関連した動作パラメータの第1群を監視するため、メモリボールトと関連した動作パラメータの第2群を調整するため、および、ホストデバイスへの警報および報告動作を実行するために作動する、システムおよび方法が本明細書において開示される。  (もっと読む)

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】本構成を有さない場合に比べ、メモリに対する異常データの書込みに対処することができるメモリ制御装置及びメモリ制御プログラムを提供する。

【解決手段】生成した識別子をIDレジスタ32に設定し、データバス30に出力された合成データに含まれる識別子とIDレジスタ32に設定されている識別子が一致する場合は、比較回路34により出力された、LレベルのWE信号によりNVM20に書込データが書込まれ、記憶される。

(もっと読む)

過渡エラー制約を受ける電子システムのためのメモリアクセス監視装置

【課題】過渡エラー制約を受ける電子システム用の処理手法を提案し、過渡エラーの様相を検出し、それらを修正することである。

【解決手段】本発明は、過渡エラー制約を受ける電子システムの処理手順に関し、単一物理チャネルにある二つの仮想チャネルが所定のリアルタイムサイクルでタイミングよく多重化され(使用の前に票決できるように、仮想チャネルの各実行から生じるデータは記憶されている)、エラーが検出された場合には、処理中のリアルタイムサイクルは禁止され、再ロードされたコンテキスト始まる次のサイクルの仮実行からなる再開始を行うように異常のないコンテキストが再ロードされる。本発明は、また、メモリアクセスの監視装置にも関する。

(もっと読む)

81 - 100 / 273

[ Back to top ]