Fターム[5B018NA02]の内容

記憶装置の信頼性向上技術 (13,264) | メモリの種類 (2,134) | RAM (515) | DRAM (160)

Fターム[5B018NA02]に分類される特許

41 - 60 / 160

システムの立ち上げ時間を早めるための方法、装置およびコンピュータ・プログラム

【課題】システムの立ち上げ時間を早めるための方法を提供する。

【解決手段】システム上にストアされたオペレーティング・システムの起動動作と並行しかつその後に、追加量のメモリを割り当てのためにスクラビングして利用することができるようにするステップとを含む。システムは、各々が最少ノード資源構成に関連付けられた1個もしくは複数個のノードを含むことができ、前記最少ノード資源構成は、前記ノードを活性化するために、活性化される必要のあるノードに含まれる最少数のプロセッサに対応する。システムは、各パーティションが少なくとも1個のノードを包含する1個もしくは複数個のパーティションを更に含むことができる。各パーティションには他のパーティションに対する優先度が割り当てられることができ、そのパーティションはその割り当てられた優先度に基づき活性化される。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】コントローラ側に特別な制御を要求することなく、正常な一部のコアチップだけに有効なチップ識別番号を割り当てて正常なコアチップのみを動作させる。

【解決手段】半導体装置10は、複数のコアチップCC0〜CC7及びインターフェースチップIFを備え、各コアチップCC0〜CC7は、第1のチップアドレスの値をインクリメントした第2のチップアドレスを生成する層アドレス発生回路46と、インターフェースチップIFから供給される第3のチップアドレスと第2のチップアドレスとを比較し、両者が一致した場合にチップ選択信号を活性化させる層アドレス比較回路47を備えている層アドレス発生回路は46、不使用チップ信号DEFが非活性状態である場合には、第2のチップアドレスを他のコアチップに供給し、不使用チップ信号DEFが活性状態である場合には、第1のチップアドレスをそのまま他のコアチップに供給する。

(もっと読む)

カメラシステム及びカメラシステムの制御方法

【課題】製品コストの増加及び大型化を抑えたMRAMを用いて、磁気メモリのプログラムが破壊されたとしても、その磁気が解消しさえすれば、再び正常に動作するカメラシステムを提供できるようにする。

【解決手段】強い磁場等の影響によりMRAM記憶部6bに記憶しているプログラムが破壊される可能性があることを検出する磁気破壊可能性判定部1aを配設して、MRAM記憶部6bが破壊される恐れがあると判定した場合には、MRAM記憶部6bに記憶しているプログラムをバックアップ記憶部7bへ退避させるとともに、その磁気が解消した場合には、前記バックアップ記憶部7bへ退避させたプログラムを前記MRAM記憶部6bへ復帰させるようにして、外界からの強い磁気によって磁気メモリのプログラムが破壊されたとしても、その磁気が解消しさえすれば、再び正常に動作することができるようにする。

(もっと読む)

ファームウェア保護装置、そのプログラム

【課題】二重化したファームウェアの両方が破損してしまった場合でもリカバリすることができる。

【解決手段】二重化したファームウェアそれぞれについて、そのプログラム本体であるプログラム部50を、複数のプログラムブロック1〜n(51)に分割して記憶する。また、ヘッダ部40には各プログラムブロック51毎に対応するSUM45を記憶し、このSUM45を用いて各プログラムブロック51毎に破損したか否かをチェックする。二重化したファームウェアの両方が破損してしまった場合でも、一方において破損したプログラムブロック51が、他方においては破損していない場合には、他方のプログラムブロック51を用いてリカバリすることができる。

(もっと読む)

誤り検出技術に基づくメモリ書き込みタイミングの調節

【解決手段】

誤り検出機能の結果に基づきメモリデバイスにおける書き込みタイミングを調節するための方法、システム及びコンピュータプログラム製品が提供される。例えば方法は、誤り検出機能の結果に基づきデータバス上の信号と書き込みクロック信号との間の書き込みタイミング窓を決定することを含むことができる。方法はまた、書き込みタイミング窓に基づきデータバス上の信号と書き込みクロック信号との間の位相差を調節することを含むことができる。メモリデバイスは、調節された位相差に基づきデータバス上の信号を回復することができる。

(もっと読む)

ミラーリング制御装置、ミラーリング制御回路、ミラーリング制御方法およびそのプログラム

【課題】より簡単な制御でミラーリングを行うことができる装置を提供する。

【解決手段】第1記憶部が、対象データの分割により生成された第1分割後データと第2分割後データのうちの第1分割後データと、第2分割後データのコピーデータとを所定の間隔の各アドレスに記憶し、第2記憶部が、第2分割後データと、第1分割後データのコピーデータとを所定の間隔の各アドレスに記憶する。そして、対象データの読み出し要求に基づいて、当該読み出し要求が示すアドレスとそのアドレスを基準とする所定の間隔の他のアドレスから第1分割後データと第2分割後データのコピーデータとを第1記憶部から読み出し、また、対象データの読み出し要求に基づいて、当該読み出し要求が示すアドレスとそのアドレスを基準とする所定の間隔の他のアドレスから第2分割後データと第1分割後データのコピーデータとを第2記憶部から読み出す。

(もっと読む)

メモリ初期化回路、メモリ初期化方法、及び情報処理装置

【課題】ソフトウエアのバグをハードウエアで検出することができるメモリ初期化回路を提供する。

【解決手段】メモリ初期化回路は、特定のデータパターンを持つ初期化データを生成する初期化データ生成手段と、メモリにECCとデータを書き込んで初期化するときにそのデータとして特定のデータパターンを持つ初期化データを書き込むようにメモリ初期化動作を制御するメモリ初期化制御手段と、初期化データの判別により、ソフトウエアのバグを検出する手段とを備える。

(もっと読む)

コンピュータメモリテスト構造

コンピュータメモリテスト構造のための方法及び装置が提供される。メモリボードをテストする方法の一実施形態は、メモリボードのメモリをテストすることを含み、このようなメモリのテストは、組込み自己テスト構造を使用して、メモリのための第1テストパターンを与えることを含む。更に、この方法は、ホストでメモリのIO(入力出力)インターフェイスをテストすることも含み、このようなIOインターフェイスのテストは、組込み自己テスト構造を使用して、IOインターフェイスの第2テストパターンを与えることを含む。 (もっと読む)

ダイナミックランダムアクセスメモリチャネル制御器のパラレルトレーニング

【解決手段】

コンピュータシステムにおけるトレーニング時間及びこれに伴うブート時間を短縮化するために、多重メモリチャネルが同時にトレーニングされる。トレーニング同期器は、多重メモリチャネル制御器に対するトレーニングデータ及びパラメータを受信し、通信インタフェースを介してメモリチャネル制御器と同時に通信する複数の通信インタフェースを含む。メモリチャネル制御器は、トレーニング同期器に応答して、メモリチャネル制御器のそれぞれに結合される複数のメモリチャネルを同時にトレーニングする。

(もっと読む)

セルフリフレッシュ・モードのためのメモリ・デバイス制御

【課題】セルフリフレッシュ・モードのためのメモリ・デバイス制御を提供する。

【解決手段】メモリ回路において、メモリ・コントローラがパワーダウンおよびパワーオフされている間、DDR3 RDIMMなどのメモリ・デバイスがセルフリフレッシュ・モードで安全に動作することを保証するために、メモリ・デバイスのクロック・イネーブル(CKE)入力が、(i)メモリ・コントローラによって印加されたCKE信号と、(ii)パワー・モジュールによって供給された終端電圧の両方に接続される。メモリ・コントローラをパワーダウンするために、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは終端電圧をローに駆動し、パワー・モジュールはメモリ・コントローラをパワーダウンする。通常の動作を再開するために、パワー・モジュールはメモリ・コントローラをパワーアップし、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは、終端電圧をパワーアップする。

(もっと読む)

メモリ制御装置、メモリモジュール及びメモリ制御方法

【課題】出荷後において記憶装置に不良領域が生じた場合でも継続して使用することができるメモリ制御装置、メモリモジュール及びメモリ制御方法の提供。

【解決手段】記憶領域を有する記憶装置へのアクセスを制御するメモリ制御装置であって、前記記憶領域に含まれる、データの格納が不可能な不良領域を検出し、検出された不良領域のアドレス情報を含んだ不良情報を所定の記憶領域に記憶し、前記不良領域への書込みが実行されたデータを、所定の記憶領域に記憶された不良情報に基づき、不良領域以外の記憶領域に書込む。

(もっと読む)

メモリをテストする方法及び装置

メモリ(14)をテストする方法は、テストアドレス(46)のような複数のアドレスを生成し(62、66)、複数のアドレス各々の中身にアクセスしてそれらをストレージ回路(32、34)に保存し(64、68)、複数のアドレスについてテストを実行し(70)、アクセスアドレスをスヌープ回路(36)に送ることでメモリテスト回路にアクセスし(84、86)、複数のアドレスの内の少なくとも1つにアクセスアドレスが合致しているか否かを判定し、それに応じて少なくとも1つのヒットインジケータ(52、54)を生成し(88)、スヌープミスインジケータ(27)を生成し(92)、それがミスを示しているか否かを判定し、ミスを示していた場合、アクセスアドレスに応じてメモリにアクセスし(96)、ミスを示していなかった場合、ストレージ回路の内の選択された部分に相互接続マスタ(12)のスヌープデータを格納する、或いは相互接続マスタに対するストレージ回路の選択された部分からスヌープデータを読み取る(98)。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】大容量の不揮発性メモリのアクセス時間とランダム・アクセス・メモリのアクセス時間との整合を図り、大容量不揮発のメモリを含む半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、フラッシュメモリと、クロック同期型DRAMと、前記フラッシュメモリ及び前記クロック同期型DRAMに結合され、前記クロック同期型DRAM及び前記フラッシュメモリに対するアクセスを制御するための制御回路と、前記制御回路に結合された複数の入出力端子とを含む。前記入出力端子を介した前記フラッシュメモリに対するアクセスは、前記クロック同期型DRAMを経由して行う。

(もっと読む)

半導体装置およびその試験方法

【課題】SIP型の半導体装置において、ロジックチップとメモリチップとの間の接続故障を特定して検出することができる半導体装置およびその試験方法を提供する。

【解決手段】複数のメモリ側パッドを有するメモリチップと、複数のメモリ側パッドのそれぞれに接続された、複数のコントローラ側パッドを有するメモリコントローラチップとからなる半導体装置において、コントローラチップに、コントローラ側パッドのそれぞれが入力に接続され、コントローラ側パッドから出力される信号のレベルに応じた試験信号を生成する複数の試験信号生成回路を設け、試験モードにおいて、信号を対応するコントローラ側パッドに出力した状態で、複数の試験信号生成回路のそれぞれが生成する試験信号を期待値と比較する。

(もっと読む)

半導体装置ソケット

【課題】 半導体モジュールの不具合によるシステム不起動が生じた場合でも、不具合の原因を検出できるようにする。

【解決手段】 半導体装置ソケットは、半導体記憶装置を備えた半導体モジュールの挿入部を受けるソケット部と、システムへの挿入部と、半導体記憶装置の代わりに使用可能な代替半導体記憶装置と、半導体モジュールの半導体記憶装置と代替半導体装置との間でシステムとの接続を切り替える切替スイッチと、を備える。

(もっと読む)

DRAMバッファ管理装置および方法

【課題】別途のデバイスを追加することなく、DRAMバッファにエラー訂正コードを適用することのできるDRAMバッファ管理装置および方法を提供すること。

【解決手段】DRAMバッファ管理装置およびDRAMバッファ管理方法が開示される。当該DRAMバッファ管理装置およびDRAMバッファ管理方法においては、DRAMバッファに記録されるデータに対するエラー訂正コードを生成し、前記データおよび前記ECCを前記DRAMバッファに記録する。  (もっと読む)

(もっと読む)

情報処理装置

【課題】セルフリフレッシュ機能を有するSDRAMを備える複合機において、消費電力の低減のためにプロセッサを停止させる省電力モードから、通常動作モードへの移行にかかる時間を短縮する。

【解決手段】プロセッサ32は、停止が解除された時及び電源投入時に初期動作プログラムを実行する。プロセッサ32は、初期動作プログラムに基づいて、SDRAM34のセルフリフレッシュモードを解除し、プロセッサ32による外部リフレッシュに切り替える。プロセッサ32は、初期動作プログラムに基づいて、SDRAM34内に通常動作プログラムが正しく保持されていることを確認する。SDRAM34内に通常動作プログラムが正しく保持されていない場合は、プロセッサ32は、初期動作プログラムに基づいて、フラッシュメモリ33内の初期動作プログラムをSDRAM34内に転送する。

(もっと読む)

メモリ装置

【目的】読出データに対する誤り検出及び誤り訂正機能を備えたメモリ装置において、その装置規模を小規模化させることが可能なメモリ装置を提供することを目的とする。

【構成】メモリアレイから読み出されたデータに対して誤り検出を行う誤り検出回路及びこの誤り検出結果に基づき上記読み出されたデータ中の誤りビットを訂正する誤り訂正回路の内の誤り検出回路を、上記メモリアレイが構築されているメモリチップに搭載し、誤り訂正回路は、このメモリチップに対するデータの読み出し制御を担うメモリ制御チップ側に搭載する。

(もっと読む)

メモリ制御装置及びその遅延量測定方法

【課題】 量産に適用されるような一般的なテスタでも遅延回路の遅延量の測定が可能なメモリ制御装置及びその遅延量測定方法を提供することを課題とする。

【解決手段】 本メモリ制御装置は、半導体記憶装置にデータを書き込むメモリ制御装置であって、入力信号を遅延させて出力する複数の遅延回路を有し、通常動作時に、前記複数の遅延回路は、互いに独立し、個々の遅延回路に入力される信号を個々に遅延して出力し、テスト動作時に、前記複数の遅延回路は、テスト用入力信号が全ての遅延回路を経由し、それぞれの遅延量の合計分だけ遅延するように接続され、遅延後の前記テスト用入力信号は、テスト用出力信号として、前記メモリ制御装置の外部に出力されていることを要件とする。

(もっと読む)

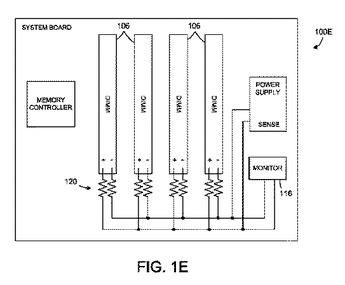

電圧センス監視インターフェースを備えたメモリモジュール

メモリデバイス及びシステムは、可変負荷にわたる電圧許容誤差に対処するための電圧センスラインを含む。該メモリデバイス及びシステムは、メモリモジュール上の回路構成に結合された第1の複数ピンと、該メモリモジュール上の電力レールに結合された第2の複数ピンとを有したメモリモジュールコネクタを備える。該第2の複数ピンは、外部から該メモリモジュールへの該電力レールの監視を可能にする。  (もっと読む)

(もっと読む)

41 - 60 / 160

[ Back to top ]