Fターム[5B018QA11]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 電源投入時 (199)

Fターム[5B018QA11]に分類される特許

21 - 40 / 199

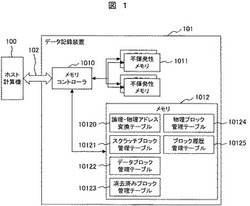

メモリコントローラ、及びデータ記録装置

【課題】管理テーブルを不揮発性メモリに保存する時の応答遅延時間を縮減し、データ記録装置の電源遮断後に、不揮発性メモリに保存した情報から管理テーブルを復元する機能を備えるメモリコントローラを提供する。

【解決手段】不揮発性メモリ1011は、管理テーブル格納ブロックと、データ書き込みのために割り当てたスクラッチブロックと、データを保持するデータブロックと、データを消去した消去済みブロックを持つ。メモリ1012は、データの格納場所を管理する論理・物理アドレス変換テーブル10120と、ブロック履歴管理テーブル10125を持つ。管理テーブル格納ブロックは、論理・物理アドレス変換テーブル10120とブロック履歴管理テーブル10125を保存する管理テーブルページを持つ。メモリコントローラ1010は、論理・物理アドレス変換テーブル10120の一部を不揮発性メモリ1011の管理テーブル格納ブロックに保存する。

(もっと読む)

情報処理装置及び情報処理装置におけるデータ管理方法

【課題】電源オン/オフの際に、ブロックを分割した複数のデータ領域のうち読出し元及び書込み先のデータ領域を比較的簡単に特定できる情報処理装置及情報処理装置におけるデータ管理方法を提供する。

【解決手段】フラッシュメモリー装置の2つのブロックA,Bは、それぞれ1つの管理領域と複数のデータ領域とに分割され、管理領域にはROM状態とブロック状態と選択領域の各情報が格納される。電源オン時のデータ読出し時には、まず各ブロックA,Bの管理領域を読み出す(S11,S12)。管理領域Aのブロック状態が「使用中」であれば選択領域の指すデータ領域からデータを読み出す。一方、「消去可」であればブロックAのデータ消去を行う(S15)。ブロックBも同様に処理される(S17〜S20)。なお、電源オフ時のデータ書込みの際は、ブロックの全てのデータ領域が使い終わると、ブロック状態が「使用中」から「消去可」に変更される。

(もっと読む)

不揮発性メモリの初期化装置および初期化方法

【課題】不揮発性メモリの初期化の手順の簡略化を図るとともに検査装置を検査に必要な最少限の構成とする。

【解決手段】予め不揮発性メモリの特定の値を書き換える信号を電子制御装置に入力し、電源投入により不揮発性メモリに対してイニシャル処理を行い、イニシャル処理で不揮発性メモリの初期化が必要と判断されたとき、前記書き換え信号により、不揮発性メモリに対して不揮発性メモリの特定の値を書き換える初期化処理を行う。

(もっと読む)

画像処理装置及び画像記録装置

【課題】 第1演算部と挿脱可能な外部メモリに接続される第2演算部とを備え、外部メモリの不具合を検出してユーザに通知することができる画像処理装置を提供する。

【解決手段】 プリンタ装置1の画像処理装置2は、メインCPU5と、サブCPU6と、外部メモリ11を挿脱可能なメモリスロット10とを備え、メモリスロット10は、外部メモリ11のSPD領域11bにアクセス可能な端子10bを有し、該端子10bはメインCPU5に接続されている。そして、メインCPU5は、サブCPU6の起動に先立ち、端子10bを介してSPD領域11bにアクセスし、外部メモリ11のエラーチェックを行うように構成されている。

(もっと読む)

メモリチェック方法および画像処理装置

【課題】システムプログラムの起動処理の完了までに掛かる時間を短縮し、画像処理装置を早く使用可能にすることができるメモリチェック方法および画像処理装置を提供する。

【解決手段】第1ステップS1として、メモリチェック回路により、ワーク領域についてメモリチェックを行うとともに、プロセッサにより、システムプログラムデータを第1バッファメモリに書き込む。第2ステップS2として、メモリチェック回路により、格納領域について、第1バッファメモリに書き込まれたシステムプログラムデータを用いてメモリチェックを行う。第3ステップS3として、メモリチェック回路により、イメージ領域についてメモリチェックを行うとともに、プロセッサにより、格納領域に書き込まれたシステムプログラムデータに基づいて、システムプログラムの起動処理を行う。

(もっと読む)

電子機器、及び、電子機器の制御方法

【課題】セクターが形成される不揮発性メモリーにおいて、セクターの使用効率を向上する。

【解決手段】フラッシュメモリー28の記憶領域に、複数のセクターを形成し、これら複数のセクターに、バンク単位で巡回的にデータを書き込み、複数のセクターうち1のセクターに対してバンクを書き込む際に、書き込みエラーが発生した場合、1のセクターに既に正常に書き込みが終了しているバンクを他のセクターにコピーし、新たなバンクの書き込みは、他のセクターに対して行うようにした。

(もっと読む)

半導体装置

【課題】フラッシュメモリ等の不揮発性メモリの誤書き込み、誤消去を防止する半導体装置を提供する。

【解決手段】内部リセット信号を正論理で保持するレジスタと負論理で保持するレジスタとを複数設け、これらの出力信号と、外部リセット信号とを入力し、これらの信号のいずれかがリセット状態である場合に活性化し、これらの信号のいずれもリセット状態でない場合に非活性化するメモリリセット信号を出力するメモリリセット信号を出力するメモリリセット信号生成回路と、メモリリセット信号を入力し、メモリリセット信号が活性化しているときにリードライトアクセス、消去動作が禁止される不揮発性メモリと、を備える。

(もっと読む)

不揮発性メモリからの装置ブートアップ中のエラーの取り扱い

【課題】不揮発性メモリ(NVM)からの装置ブートアップ中にエラーを取り扱うためのシステム及び方法を提供する。

【解決手段】電子装置のNVMインターフェイスは、装置がブートアップされている間にエラーを検出して揮発性メモリにエラーログを維持するように構成される。装置のブートアップが完了すると、電子装置のNVMドライバは、エラーログを使用して、検出されたエラーを修正するように構成される。例えば、電子装置は、より信頼性の高いブロックへデータを移動し、及び/又は欠陥に近いブロックを撤退させ、装置全体の信頼性を改善することができる。

(もっと読む)

画像処理装置、画像形成装置、およびメモリチェック方法

【課題】起動時間を短縮しながら、チェック対象メモリのチェックを効率的に行う画像処理装置を提供する。

【解決手段】画像処理装置10は、メモリのエラーをチェックする制御部8と、制御部8によりエラーがチェックされるチェック対象メモリ7とを備える。制御部8は、起動した後に、予め設定されたタイミングでチェック対象メモリ7のチェックを行い、チェック対象メモリ7の全領域がチェックされた場合は、次回起動時にチェック対象メモリ7のチェックを行わず、チェック対象メモリ7の全領域がチェックされていない場合は、次回起動時にチェック対象メモリ7の未チェックの領域をチェックする。

(もっと読む)

画像処理装置および画像形成装置

【課題】起動時間を短縮しながら、チェック対象メモリにチェックされない領域が生じることを抑制する画像処理装置を提供する。

【解決手段】画像処理装置10は、メモリのエラーをチェックする制御部8と、制御部8によりエラーがチェックされるチェック対象メモリ7とを備える。制御部8は、起動処理が実行されるときに、チェック対象メモリ7の一定領域をチェックし、起動処理が実行された後に予め設定された停止要因が発生した場合に、チェック対象メモリ7の一定領域以外の領域をチェックする。

(もっと読む)

メモリシステム

【課題】頻繁に書き換えを行うデータ領域と殆ど書き換えを行わないデータ領域とが混在するデータを格納している際にも最適なウェアー・レベリング制御が可能で、システムの書き換え回数の実効的な寿命を大幅に改善することが可能なメモリシステムを提供する。

【解決手段】制御部は、特定物理アドレスブロックに書き換えが集中しないウェアー・レベリング(Wear-leveling)制御を行う際、書き換えを行わない物理アドレスブロックは、そのまま放置しておくパッシブ・ウェアー・レベリング制御と、書き換えを行わない物理アドレスブロックも全ての物理アドレスブロックの書き換え回数が平均化されるように書き換えを行うアクティブ・ウェアー・レベリング制御とが可能であり、不揮発性メモリ部には、パッシブ・ウェアー・レベリング制御およびアクティブ・ウェアー・レベリング制御の方式選択、若しくは、両ウェアー・レベリングの条件設定値が格納されている。

(もっと読む)

制御装置、制御モジュールおよび制御方法

【課題】情報管理の信頼性を高めること。

【解決手段】記憶装置2は、データの書き込みが複数回可能な複数のブロックを有する第1の記憶領域2aと、データの書き込みが1回だけ可能な第2の記憶領域2bとを有する。フラグ管理情報作成部1bは、第1の記憶領域2aに記憶されているフラグに基づいて、記憶装置2のブロック毎にデータが記憶可能か否かを示す管理テーブル(フラグ管理情報)1b1を作成する。管理情報制御部1cは、フラグ管理情報作成部1bにより作成された管理テーブル1b1を第2の記憶領域2bに記憶させる。

(もっと読む)

メモリチェック方法および画像処理装置

【課題】 システムメモリのメモリチェックとシステムプログラムの起動処理とを並列に行うことができるメモリチェック方法および画像処理装置を提供する。

【解決手段】 第1ステップS1として、メモリチェック回路2により、格納領域41のメモリセルについてメモリチェックを行う。そして、第2ステップS2として、メモリチェック回路2により、ワーク領域42のメモリセルについてメモリチェックを行うとともに、プロセッサ1により、第2不揮発性メモリ6内のシステムプログラムデータの、格納領域41への転送を開始する。最後に、第3ステップS3として、メモリチェック回路2により、イメージ領域43のメモリセルについてメモリチェックを行うとともに、プロセッサ1により、格納領域41に転送、格納されたシステムプログラムデータに基づいて、システムプログラムの起動処理を行う。

(もっと読む)

メモリシステム

【課題】リード/ライトの高速化が図れるメモリシステムを提供する。

【解決手段】メモリシステムは、電気的にデータの消去、書き込みが可能なメモリセルを複数配設してなるフラッシュ型EEPROMからなる第1のメモリ13−1,…,13−nと、強誘電体メモリ,磁気抵抗メモリ,及び相変化メモリの何れかからなり、第1のメモリよりも小容量で書き込み速度の速い第2のメモリ14と、第1及び第2のメモリ13,14を制御するコントロール回路15と、外部との通信を行うインターフェース回路とを有する。第1のメモリ13にはデータを記憶し、第2のメモリ14にはデータを記憶するためのルート情報、ディレクトリ情報、データのファイル名称、データのファイルサイズ、データの記憶箇所を記憶するファイルアロケーションテーブル情報、及びデータの書き込み終了時間の少なくとも一つを記憶する。

(もっと読む)

画像形成装置、メモリチェック方法、および、メモリチェックプログラム

【課題】画像形成装置に搭載されるメモリのチェックについて、メモリの信頼性を確保しつつチェック時間を短縮すること。

【解決手段】画像形成装置1の不揮発性メモリ13には、RAM14をチェックする処理の強度を示すチェックモードが記憶され、RAMチェック処理部16はチェックモードに従ってRAM14をチェックする。RAMチェックモード設定部15は、メモリエラーが検出されたときには、不揮発性メモリ13内に現在記憶されているチェックモードよりも強度の高いチェックモードを、不揮発性メモリ13に書き出し、メモリエラーが検出されないときには、不揮発性メモリ13内に現在記憶されているチェックモードよりも強度の低いチェックモードを、不揮発性メモリ13に書き出す。

(もっと読む)

車両用ナビゲーション装置

【課題】NAND型フラッシュメモリをブートデバイス用として使用しながら、ソフトの起動が遅れてしまうことがない車両用ナビゲーション装置を提供する。

【解決手段】リセットシーケン3は、バックアップ電源からの給電により起動した場合は、電源スイッチ2をオンすることによりSDカード7に給電し、アクセサリオン信号を受信した場合はCPU5に給電して起動する。起動したCPU5は、リセットシーケンサ3のBUフラグ3bがオフしていたときはSDカード7にアクセスするのを待機する待機処理を実行してからBUフラグ3bをオンすると共にSDカード7からIPLを読取るブート処理を実行し、BUフラグ3bがオンしていたときは待機処理を実行することなくブート処理を実行する。

(もっと読む)

携帯可能電子装置及び携帯可能電子装置の制御方法

【課題】 ICカード処理装置からのコマンドに応じてICカードが不揮発性メモリ上のデータ格納領域へのデータの書き込みを行う処理に要する時間を短縮することができる。

【解決手段】 外部装置から受信したコマンドに基づいてデータを不揮発性メモリ上のデータ格納領域に書き込む必要がある場合、不揮発性メモリ上のバッファ領域に当該データを書き込み、上記バッファ領域へのデータの書き込みが終了した際にバッファ領域への書き込み完了を示す応答データを外部装置へ出力し、当該データをデータ格納領域に書き込むようにしたものである。

(もっと読む)

情報処理装置および監視機器システム

【課題】データ復旧の信頼性を保持しつつ、データ復旧時間の短縮を目的とする。

【解決手段】それぞれのROMに格納されているデータが一致しているか否かをアドレス毎に判定する一致検出部A101と、それぞれのROMに格納されているデータの値を加算して、第1チェックサム値を算出する加算部106と、第1チェックサム値と、予めROMに格納されている第2チェックサム値とを、それぞれのROMにおいて比較する一致検出部B105と、一致検出部A101でデータの不一致が検出されたアドレスを記憶するアドレスバッファ部103と、第2の一致検出部において、チェックサム値が不一致であると判定された場合、チェックサム値が一致しているROMから、チェックサム値が一致していないROMへ、アドレスバッファ部103に記憶されているアドレスに該当するデータをコピーするデータ復旧部104と、ことを特徴とする。

(もっと読む)

ミラーメモリ構成のコンピュータシステムにおけるダンプ方法、ダンプ制御機構、およびプログラム

【課題】ダンプ終了後、システムの再起動なしにメモリを再度二重化する

【解決手段】書込み制御部11は、ダンプフラグ16を参照しダンプの必要があることを確認し、初期化制御部14に対してマスターメモリ2のみ初期化するよう制御する。ダンプフラグが「1」の間は、書込み制御部11、読出し制御部12はマスターメモリ2のみにアクセスするよう制御する。マスターメモリ2の初期化が終了したら、初期化完了のステータスを返信し、OSを起動する。OSの動作中、スレーブメモリ3に対して、メモリダンプの書込み処理を行う。ダンプ書込み制御部17によりスレーブメモリ3のデータを読出し、ディスク4へ書き込む処理を行う。書込みが終了したら、書込み制御部11によりスレーブメモリ3の初期化を行う。また、初期化の終了によりミラー化制御部13によりマスターメモリ2とスレーブメモリ3をミラー化構成にする。

(もっと読む)

データ記憶装置及びデータ記憶方法

【課題】電源の瞬断が発生した場合であっても、データの消失又は破損等が生じることがないデータ記憶装置及びデータ記憶方法を提供する。

【解決手段】データがそれぞれ一括消去される複数の記憶ブロックに対してメモリ管理部21が順次的にデータを書き込み、データの書き込み先を変更する際には有効なデータを次のブロックへコピーするブロック更新処理を行う。最初に書き込みを行う第1記憶ブロック221には、記憶ブロック毎に更新開始ビット、更新終了ビット及び消去終了ビットの3つの情報を管理情報として記憶しておく。メモリ管理部21はブロック更新処理の開始前に更新開始ビットをデータ’0’に設定し、ブロック更新処理の終了後に更新終了ビットをデータ’0’に設定する。またメモリ管理部21は、更新終了ビットがデータ’0’に設定された記憶ブロックの消去処理を行い、消去処理の終了後に消去ビットをデータ’0’に設定する。

(もっと読む)

21 - 40 / 199

[ Back to top ]