Fターム[5B018QA11]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 電源投入時 (199)

Fターム[5B018QA11]に分類される特許

61 - 80 / 199

画像形成装置

【課題】エラー発生時のダウンタイム、サービスコール数、ユーザーの手間を低減しつつ、リブート後にリブート前の処理をスムーズに再開する。

【解決手段】CPU12もしくはDMAC11bは処理対象データーをRAM13に記憶させる際にRAM13に記憶された処理対象データーのスタートアドレスとサイズ情報を領域レジスタ11cに記憶させ、所定条件により自動リブートを行う際に、CPU12は上記スタートアドレスとサイズ情報に基づきRAM13の処理対象データーを記憶された領域についてRAMテストを行わずにリブートし、CPU12はリブート完了後に上記スタートアドレスとサイズ情報に基づき処理対象データーを特定して該処理対象データーの処理を行う。

(もっと読む)

メモリ制御システム、メモリ制御方法、メモリ制御プログラム及び記録媒体

【課題】メモリ動作を決定する複数のパラメータを適切な値に調整する。

【解決手段】複数のパラメータが取り得る値の複数の組み合わせを管理するパラメータ管理部11aと、パラメータ管理部11aによって管理されている複数の組み合わせを複数のパラメータに順次設定するパラメータ設定部11dと、パラメータ設定部11dによって複数の組み合わせが複数のパラメータに順次設定される都度、メモリ2とメモリコントローラ12との間のメモリ動作の試験を行い、その試験の判定結果を蓄積するパラメータ試験部11bと、パラメータ試験部11bに蓄積された試験の判定結果に基づいて、複数の組み合わせの中の1組を決定するパラメータ決定部11cと、を備え、パラメータ設定部11dは、パラメータ決定部11cによって決定された複数の組み合わせの中の1組を複数のパラメータに設定する。

(もっと読む)

メモリシステム

【課題】不正な電源断を簡便かつ確実に検出することが可能なメモリシステムを提供する。

【解決手段】システム起動後最初の差分ログがNANDログ203に記録される前に、システムが動作中であることを示すActiveログをNANDログ203に記録し、正常なシステム停止時に、システムが停止することを示すStandbyログを差分ログに続いてNANDログ203に追記記録し、システム起動時、NANDログ203内のActiveログおよびStandbyログの記録状態に基づき、前回正常なシステム停止が行われたか不正な電源断が行われたかを判断する。

(もっと読む)

不揮発性記憶デバイスを有する記憶装置

【課題】データ読み出しに破壊読み出しを伴う不揮発性記憶デバイスに記憶されているデータに、不意な電源遮断に起因するようなエラー部分が残されていても、特別のハードウェア構成を必要とすることなく、そのエラー部分を高速で復旧できるようにする。

【解決手段】FeRAM11の記憶領域には、ユーザーデータ領域111及びブロックアドレス領域112が確保される。ブロックアドレス領域112は、ユーザーデータ領域111からのデータ読み出しに際し、読み出されるべきデータが格納されているアドレスを示すアドレスデータを格納するのに用いられる。MPU16は、ブロックアドレス領域112に格納されているアドレスデータの示す、ユーザーデータ領域111の記憶位置に格納されているデータのエラーを検出し、エラーが検出された場合、当該エラーが検出されたデータを訂正して、当該訂正されたデータをユーザーデータ領域111に書き戻す。

(もっと読む)

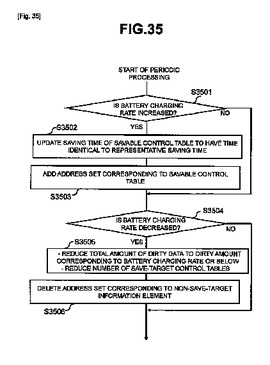

揮発性メモリと不揮発性メモリとを備えたストレージシステム

【課題】揮発性メモリにおける退避対象を確実に不揮発性メモリに退避できるようにする。退避処理に要する時間をなるべく短くする。

【解決手段】バッテリの充電状況が定期的又は不定期的に把握され、把握された充電状況に応じて、揮発性メモリに記憶されているどの情報要素を、電断発生時の退避対象とするかが制御される。揮発性メモリに記憶されている複数の情報要素のうち特定の情報要素が、その特定の情報要素に関する状況に応じて、退避処理の際の非退避対象とされる。

(図35)  (もっと読む)

(もっと読む)

半導体記録装置

【課題】書き込みエラーが多発した場合においても、連続して書き込みが可能な信頼性の高い半導体記録装置を提供する。

【解決手段】書き込むべきデータをECC符号として不揮発性メモリを構成する複数の物理ブロックに記録し、書き込みエラーが発生した場合は、直前に発生した書き込みエラーと現書き込みエラーとの時間間隔を検出する。そして、時間間隔が第1の基準時間以内であれば誤り位置管理手段に、書き込みエラー発生ブロック番号と、書き込みエラー発生ブロックとECCのグループになっているブロック番号とを登録する。そして、所定のタイミングで、誤り位置管理手段に登録された書き込みエラーを読み出し、ECC符号により誤り訂正することによって復元し、再書き込みを行う。これにより、ホスト機器のバッファメモリのオーバーフローを防止できるため、書き込みエラーが頻発した場合においても、映像信号のリアルタイム記録が可能である。

(もっと読む)

コンピュータ装置、メモリ診断方法、及びメモリ診断制御プログラム

【課題】複雑なメモリ診断プログラムであってもOS起動前にこれを正常に実行することができること。

【解決手段】メインメモリを有するコンピュータ装置であって、第1のメモリ診断プログラムを実行することにより、メインメモリの不良領域の特定を行う第1のメモリ診断手段と、再配置可能な第2のメモリ診断プログラムが記憶された記憶手段と、メインメモリのうち、第1のメモリ診断手段により特定された不良領域を除く領域に、記憶手段に記憶されている第2のメモリ診断プログラムを展開し、実行する第2のメモリ診断手段と、を有する。

(もっと読む)

コンピュータ装置、プロセッサ診断方法、及びプロセッサ診断制御プログラム

【課題】プロセッサの不良機能を確実に特定して、各種の診断テストの正常な実行を担保すること。

【解決手段】第1のプロセッサと、第2のプロセッサと、メインメモリとを有するコンピュータ装置であって、第2のプロセッサによりメモリ診断プログラムを実行させることにより、メインメモリを診断し、メインメモリ内の不良領域を特定するメモリ診断手段と、メインメモリのうち、メモリ診断手段により特定された不良領域を除く領域に、第1のプロセッサの有する複数の機能を診断するためのプロセッサ診断プログラムを展開する診断プログラム展開手段と、展開されたプロセッサ診断プログラムを第2のプロセッサにより実行させることにより、第1のプロセッサの有する複数の機能のうち、実行不能な機能である不良機能を特定する不良機能特定手段と、を有する。

(もっと読む)

補正回路、及び補正方法

【課題】不揮発性メモリにおいて生じたデータ化けを、迅速に修正する技術を提供する。

【解決手段】データを所定の多重度で複数のデータに多重化して予め記憶した記憶装置と、該記憶装置にアクセスする演算装置とに接続され、該データに生じたビット化けを補正する補正回路は、前記演算装置が前記データを読み出すための命令を実行している間に、前記記憶装置から前記複数のデータを、前記多重度と等しい数の複数のビットごとに読み出す読出手段と、前記読出手段により読み出された前記複数のビットのうち、いずれかのビットの値が予め想定されたビット化け前の値である場合、該ビット化け前の値のビットを前記演算装置に出力し、該複数のビットの全ての値がビット化け後の値である場合、該ビット化け後の値のビットを該演算装置に出力する補正手段と、を有する。

(もっと読む)

ファイルサーバシステム及びファイルサーバシステム起動方法

【課題】ファイルサービス提供に必要なメモリ容量のみをシステムブート時のメモリテスト対象とすることによって、メモリテスト時間を最少化し、ファイルサーバのシステムブート時間を短縮する。

【解決手段】ホスト計算機にファイルサービスを提供するファイルサーバであって、前記ファイルサービスを提供するために必要な前記メモリの記憶領域の容量を計算し、前記計算された容量の記憶領域をテストする第1メモリチェックを実行し、前記第1メモリチェックが完了した後、前記メモリの残りの記憶領域をテストする第2メモリチェックを実行し、前記第1メモリチェックが完了した後、前記第2メモリチェックが完了する前に、前記ファイルサービスの提供を開始する。

(もっと読む)

フラッシュメモリを用いた装置及びそのフラッシュメモリへのデータの書き込み方法

【課題】フラッシュメモリに保存しているデータの書き込みを行う場合の新しいデータの書き込み、古いデータの消去の一連の動作時に、停電などの事故があったときでも、フラッシュメモリに書き込み前のデータが保存されている状態または書き込み後の新しいデータが保存されている状態に復元できるフラッシュメモリを用いた装置及びそのフラッシュメモリへのデータの書き込み方法を提供する。

【解決手段】フラッシュメモリを用いた装置1において、フラッシュメモリ11は記憶領域として少なくとも3つのページ2a,2b,2c…を備え、各ページ2a,2b,2c…の記憶領域が、書き込まれる正データの2倍以上の容量を有し、現在のページ2aの記憶領域のみにデータDpが書き込まれている状態で、新しいデータを書き込むとき、次のページ2bの記憶領域に新しいデータDfを書き込んだ後、現在のページ2aのデータDpを消去するものである。

(もっと読む)

記憶装置

【課題】簡単な構成で高速化と小型化を実現した記憶装置を提供する。

【解決手段】半導体不揮発性メモリ、半導体揮発性メモリ、上記半導体不揮発性メモリ及び半導体揮発メモリに対してメモリアクセスを行うコントローラを有する。上記コントローラは、中央処理装置と、制御論理回路とを有する。上記制御論理回路は、上記半導体不揮発性メモリと上記半導体揮発性メモリとの間でのデータ転送動作を第1周波数に対応したメモリ制御を分担する。上記中央処理装置は、上記第1周波数よりも低い第2周波数に対応して上記制御論理回路が行うメモリ制御以外のメモリ制御動作を分担する。

(もっと読む)

フラッシュメモリ制御装置及びフラッシュメモリ制御方法

【課題】フラッシュメモリのエラー箇所の累積を回避するフラッシュメモリ制御装置を提供する。

【解決手段】フラッシュメモリ制御装置は、複数のブロックから構成される書き換え可能なNANDフラッシュメモリ210と、所定のタイミングで、NANDフラッシュメモリ210の複数のブロックのうち全ブロック数より少ない任意の数のブロックをリフレッシュし、所定のタイミングの度に、前回とは異なるブロックをリフレッシュするNANDフラッシュコントローラ110と、を備える。

(もっと読む)

記録装置、画像形成装置、及びオプション装置

【課題】プログラムの書き込み中に電源断が発生した場合であっても、電源復旧後に、既に書き込みが完了している記録位置から書き込みを再開する画像形成装置を提供する。

【解決手段】記録媒体に対するデータの記録及び消去を行う書換手段と、電源部の状態監視を行う電源監視手段とを備え、電源監視手段により電源電圧の低下が検知されると、フラグ設定手段が、記録媒体に対する記録処理が行われているかどうかを確認する。記録処理が行われている場合、記録中断を示すフラグ情報と、データの記録済み部分を示すメモリアドレス等の位置情報と、記録処理中データのファイル名等を含む識別情報とを、記録媒体に記録する。電源部の復旧により再起動が行われ、フラグ情報が記録されている場合、識別情報及び位置情報を記録媒体から読み出し、記録中断位置から記録再開する。

(もっと読む)

不揮発性メモリの劣化軽減方法

【課題】不揮発性メモリにおいて劣化を有効に軽減することができる方法を提供する。

【解決手段】揮発性メモリ(12)及び不揮発性メモリ(14)を有するICチップ(10)における不揮発性メモリの劣化軽減方法は、不揮発性メモリ(14)に存在するデータを揮発性メモリ(12)に展開するデータ展開工程と、揮発性メモリ(12)に展開されたデータに対して、コマンド処理を実行するコマンド処理実行工程と、揮発性メモリ(12)に存在するデータを不揮発性メモリ(14)に書き戻すデータ書戻工程と、を含む。

(もっと読む)

メモリ制御装置

【課題】本発明は、メモリ制御装置に関し、不揮発性メモリへのデータ書き込み中に生じる電源瞬断を、不揮発性メモリの記憶機能自体の異常や読み出し機能自体の異常と区別して判定することにある。

【解決手段】終了時、不揮発性メモリの有する複数のデータ記憶領域に同じデータをそれぞれ書き込むデータ書込手段を備えるメモリ制御装置において、データ書込手段による複数のデータ記憶領域への同じデータの書き込みが完了した場合、正常にデータの書き込みが行われた旨を示すフラグを不揮発性メモリの有するフラグ記憶領域に書き込む。また、起動時、フラグ記憶領域のフラグ状態に基づいて、前回終了時のデータ書込手段による複数のデータ記憶領域への同じデータの書き込み中に電源瞬断が生じたか否かを判別する。そして、前回終了時のデータ書き込み中に電源瞬断が生じたと判別された場合、複数のデータ記憶領域に書き込まれているデータを修復する。

(もっと読む)

電子制御装置

【課題】限られた記憶容量の記憶部に記憶されるデータ容量を削減すると共に、前記記憶部に記憶されたデータを他の記憶部へ書き込む際の処理負担を軽減することのできる電子制御装置を提供する。

【解決手段】被制御部2を制御する電子制御装置1であって、バッテリ3から断続的に給電される一の揮発性記憶部11と、バッテリ3から常時給電される他の揮発性記憶部12と、給電の有無に関わらずデータを保持する不揮発性記憶部13と、被制御部2に対する制御データ以外の他のデータを、当該他のデータを記憶する必要がある場合に、一の揮発性記憶部11及び不揮発性記憶部13に記憶し、他の揮発性記憶部12の記憶状態に基づいて、不揮発性記憶部13に記憶された他のデータを一の揮発性記憶部11に書き込む制御部14とを備えている。

(もっと読む)

不揮発性メモリシステムにおいて用いられる電力管理ブロック

【課題】不揮発性メモリの電源投入プロセスを効率的に行うことを可能にする。

【解決手段】本発明は、不揮発性メモリの電源投入プロセスを効率的に行うことを可能にするシステムおよび方法に関する。本発明のある局面によると、少なくとも1つの保留メモリ領域を含む不揮発性メモリを有するメモリシステムを利用する方法は、電力をメモリシステムに提供する工程と、不揮発性メモリを初期化する工程と、第1の署名を保留メモリ領域に書き込む工程とを含む。第1の署名はメモリシステムの初期化が成功したことを示すように構成される。ある実施形態において、この方法はまた、メモリシステムの電源切断プロセスを実行する工程と、電源切断プロセスが実行されたことを示す第2の署名を保留メモリ領域に書き込む工程とを含む。

(もっと読む)

情報処理装置、該装置用のROMイメージ生成装置、および転送装置

【課題】メインプログラムをNAND型フラッシュメモリに格納する情報処理装置において、ブートストラッププログラムをNOR型フラッシュメモリに格納すると、システムのコストが高くなる。

【解決手段】電源投入後、転送装置14は、第1の記憶装置11に格納された、第1の誤り検査符号114付きのブートストラッププログラム111を検出し、誤り検出/訂正処理を施して第2の記憶装置12に転送する。転送が正常に完了した場合、CPU10は、第2の記憶装置12上のブートストラッププログラム111を実行することにより、第2の誤り検査符号115付きのメインプログラム112に誤り検出/訂正処理を施して第3の記憶装置13に転送し、第3の記憶装置13上のメインプログラム112に分岐する。これにより、NOR型フラッシュメモリを使用せずに、システムブートを行える。

(もっと読む)

バックアップ装置及び半導体試験装置

【課題】電源供給が遮断された場合であっても記憶装置に記憶された必要なデータを効果的にバックアップすることができるバックアップ装置等を提供する。

【解決手段】バックアップ装置20は、メモリ11やレジスタ12のバックアップを行う必要がない非バックアップ部P11,P21に対して補助電源2bからの電源を供給する電源線L1,L2とは別途に設けられ、バックアップを行う必要があるバックアップ部P12,P22に対して補助電源2bからの電源を供給するバックアップ電源供給線L10と、バックアップ部P12,P22に記憶されたデータをバックアップするための保持用電源21と、バックアップ電源供給線L10を監視し、補助電源2bからの電源供給が遮断された場合にバックアップ部P12,P22に対する電源供給を保持用電源21からの電源供給に切り替える切替回路22とを備える。

(もっと読む)

61 - 80 / 199

[ Back to top ]