Fターム[5B018QA11]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 電源投入時 (199)

Fターム[5B018QA11]に分類される特許

121 - 140 / 199

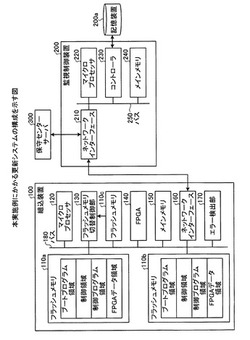

組込装置および制御方法

【課題】FPGAの障害対策を適切に実行すること。

【解決手段】組込装置100は、プログラミング可能なFPGA140に用いられる定義用データ、組込装置100の立ち上げ時に利用されるブートプログラム、制御プログラムをフラッシュメモリ110a、110bに記憶し、フラッシュメモリ110cに設定情報を記憶する。そして、フラッシュメモリ切替制御部130が設定情報を基にしてフラッシュメモリを選択(図1に示す例では、フラッシュメモリ110aあるいはフラッシュメモリ110bのいずれか一方を選択)し、選択したフラッシュメモリに記憶された定義用データをFPGA140に組み込むと共に、かかるフラッシュメモリに記憶されたブートプログラムおよび制御プログラムを読み出して組込装置100を立ち上げる。

(もっと読む)

電子機器

【課題】 低コストのフラッシュメモリの使用によるコスト低減を可能にし、更には、処理の高速化や、フラッシュメモリの寿命延長を図ることもできる電子機器を提供すること。

【解決手段】 アプリケーション処理で使う運用データ3は、データサイズがフラッシュメモリ5上の記憶ブロックサイズ以下となるn個のデータブロックに分割して、各設定値データ21,23,25の先頭に、マップ番号及びフラッシュ更新カウンタ値Fiを割り付けた構成にし、電源投入時には、フラッシュメモリ5の運用データ3をRAM6にコピーして、以後の運用データ3へのアクセスはRAM6上の各設定値データ21,23,25に対して行い、RAM6上の更新されたデータブロックを適時フラッシュメモリ5に書き込むこむことで、フラッシュメモリ5へのアクセス頻度を低減する。

(もっと読む)

情報記憶装置、情報記憶方法及びプログラム

【課題】記憶されたデータの信頼性を容易に向上する。

【解決手段】複数のバンクに分割されたフラッシュメモリ103に、バンクが使用可能かどうかを示す情報とバンクに予め付与されたバンク番号との対応付け情報が記憶され、CPU102によって、バンクに当該バンクに記憶するデータに対するECCが記憶され、ECCによりデータに訂正可能エラーがあると判断された場合、当該データが訂正され、使用可能な別のバンクに訂正されたデータがフラッシュメモリ103に書き込まれる。

(もっと読む)

メモリ制御装置

【課題】DRAMを用いたシステムにおいて、意図しないシステムリセットや電源切断などが発生した際に、すでにDRAM内にあるデータだけでなく、DRAMを用いたシステムにおいて設定されているレジスタ値も保持し、DRAMを用いたシステムを出来るだけ短い時間で元の状態に復旧させることが可能な、メモリ制御装置を提供すること。

【解決手段】リセット要因発生時にシステムリセットを生成するリセット生成部9と、レジスタ1とDRAM16との間で、レジスタ1に記憶されている設定値の転送を制御するレジスタ転送制御部5と、を備え、レジスタ転送制御部5は、リセット生成部9によりシステムリセットが生成されたことを通知されると、DRAM16にレジスタ1の設定値を転送し、システムリセットが行われた後に、レジスタ1の設定値を、DRAM16から再びレジスタ1に転送する。

(もっと読む)

不揮発性半導体記憶装置

【課題】寿命と信頼性改善を図った不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、電気的書き換え可能でかつ、nビット/セル(n≧2)の多値記憶を行うメモリチップと、前記メモリチップの読み出し及び書き込み制御を行うメモリコントローラとを備え、前記メモリチップは、後天的不良数が所定しきい値を超えたときに、nビット/セルからmビット/セル(m<n)へ動作モード切り換えが行われる。

(もっと読む)

半導体記憶装置への情報記録方法及び情報記録システム

【課題】従来の情報記録方法では、消去回数に制限のある携帯型メモリカードを効率的に利用することが困難であった。

【解決手段】本発明にかかる情報記録方法は、論理ブロック番号と論理ブロックに関連付けられた物理ブロックの物理ブロック番号とが関連付けて登録される論理物理変換テーブルと、論理ブロックに関連付けされていない物理ブロックの物理ブロック番号が登録される空き物理ブロックテーブルとを作成し、所定の論理ブロック番号に対して情報の書き込みが指定された場合に、空き物理ブロックテーブルに登録された物理ブロックのうち前記消去回数が最も少ない物理ブロックを検索し、当該最も消去回数が少ない物理ブロックに情報を記録し、空き物理ブロックテーブルに登録され情報が記録された物理ブロックの物理ブロック番号と情報の書き込みが指定された論理ブロック番号に関連付けられて登録された物理ブロック番号とを入れ替えるものである。

(もっと読む)

記憶媒体制御装置

【課題】NAND型フラッシュメモリなどのブロック単位で管理される不揮発性記憶媒体を用いるときに、利用効率を低下させることなく、適正なデータ読み出しを可能とする。

【解決手段】NAND型フラッシュメモリが接続されるメモリコントローラ20には、論理アドレスを、フラッシュメモリの物理ブロックアドレスに変換するアドレス変換部24を設けている。このアドレス変換部では、不良ブロックに対する代替ブロックを設定する代替ブロックテーブルを用いて、論理アドレス又は論理ブロックアドレスに対して、適正な物理ブロックアドレスに変換する。これにより、不良ブロックの発生を考慮して、同一のデータを複数のブロックに格納することなく、要求されるデータを適正に読み出すことができる。

(もっと読む)

半導体記憶装置

【課題】アンチヒューズによる救済方式の問題点を解決すること。

【解決手段】DRAM10、SPD(EEPROM)20が搭載されるとともに、SPD20にDRAM10の不良アドレス情報が格納されたメモリモジュール30と、不良アドレス情報をSPD20から読み出してDRAM10に不良アドレス情報を転送するメモリコントローラ40と、を備える。DRAM10は、メモリセルアレイ50と、不良アドレス情報を格納するための救済アドレスレジスタ12、14と、メモリセルアレイ50の欠陥があるメモリセルに対して代替される冗長メモリセル11と、を有する。DRAM10は、転送された不良アドレス情報を救済アドレスレジスタ12、14に格納した後、通常のアクセス動作時に、外部から入力された外部アドレス情報が、救済アドレスレジスタ12、14の不良アドレス情報と一致したときに冗長メモリセル11にアクセスする。

(もっと読む)

メモリコントローラ、不揮発性記憶装置、及び不揮発性記憶システム

【課題】従来よりも長寿命かつ処理速度の速い不揮発性記憶装置、不揮発性記憶システムを提供すること。

【解決手段】書き換え回数計数部107が各物理ブロックの書き換え回数を管理する。最多及び最小書き換え回数の物理ブロックを判別する。初期化処理に未使用ブロック検出部106が検出した未使用ブロック数が閾値以下になった場合、データ移動処理部108は最多書き換え回数ブロックと最少書き換え回数ブロック間でデータ移動する。こうすれば書き換え頻度の高いデータを特定の物理ブロックばかりにアロケートさせないようにできるので、結果として不揮発性記憶装置120の長寿命化を図ることができる。

(もっと読む)

システム環境復元方法

【課題】複数の情報処理装置を対象に、特別な環境を用意することなく容易にシステム環境の復元を行なうことができるシステム環境復元方法を提供する。

【解決手段】上記課題を解決するために、イメージファイル107を取得するイメージファイル取得手段101と、イメージファイル107を記憶装置109に書き込むイメージファイル書込み手段102と、自装置の装置特定情報を取得する装置特定情報取得手段103と、個別設定情報一覧108から個別設定情報を取得する個別設定情報取得手段104と、個別設定情報を復元したシステム環境に適用する個別設定情報設定手段105と、を備える。

(もっと読む)

NAND型フラッシュメモリデバイス及びこれを利用したコンピューティングシステムの起動方法

【課題】組み込み系コンピューティングシステムを構築するための、より改良されたNAND型フラッシュメモリデバイスの提供。及び該デバイスを用いたコンピューティングシステムの起動方法の提供。

【解決手段】NAND型フラッシュメモリからのブートローダの読み出しを、NAND型フラッシュメモリデバイスの内部機能により自律的に実行し、読み出したブートローダを、ホストCPUの内部メモリバスと直結するデバイス内のSRAMにロードする。ホストは、SRAMにロードされたブートローダの情報に基づきUSBインターフェースからOSをシステムメモリにロードし、システムを起動する。

(もっと読む)

プログラム起動制御装置

【課題】システム起動は、フラッシュメモリからランダムアクセス可能な外部メモリへの全プログラム転送完了後に制約されるので、多くの時間を要する。

【解決手段】電源投入時にフラッシュメモリ2から読み出して内部メモリ8に格納した初期化プログラムに従ってシステムの初期化を行い、外部メモリ3へのアクセスを可能とする。DMA制御部10はフラッシュメモリ2からシステム起動プログラムを読み出しダイレクトに外部メモリ3へ転送する。メモリ管理部9はCPU5が外部メモリ3からプログラムを読み出す際にプログラム転送完了を管理する。CPU5は、DMA制御部10によるシステム起動用のプログラムの転送が完了したときに、外部メモリ3から読み出したシステム起動用のプログラムに従ってシステムの起動を行う一方、同時並行的に、DMA制御部10は、フラッシュメモリ2からシステム制御用のプログラムを読み出し外部メモリ3へ転送する。

(もっと読む)

記憶装置

【課題】多ビットのメモリ故障であっても、効率よく、主記憶装置が使用不可になることを回避する。

【解決手段】主記憶装置2の初期化において、主記憶装置初期化/故障検出部6は、キャッシュメモリ5のキャッシュ有効フラグ4aに’0’を設定し、キャッシュメモリ5を無効とする。その後、主記憶装置2のSバイト領域に検査データWを記憶させた後に、主記憶装置2のSバイト領域を読み取った後、検査データWの反転データである検査データWWを主記憶装置2のSバイト領域に記憶させて、そのSバイト領域のデータを読み取る。検査データW,WWと読み取ったデータとが同じでない場合、主記憶装置2のSバイト領域が異常と見なし、そのSバイト領域をキャッシュメモリ5の任意のメモリ領域に割り付けて該Sバイト領域を救済する。

(もっと読む)

情報処理装置におけるメモリアクセス方法

【課題】 従来のシステムにおいては、複数のパラレルフラッシュICをバス接続してアクセスの高速化を行っているため、複数のパラレルフラッシュICをバス接続してアクセスの高速化を行っているため、バス配線が複雑になり、基板の小型化が出来ないとともに、ノイズの問題が大きかった。

【解決手段】 複数のシリアルフラッシュメモリと、前記シリアルフラッシュメモリにアクセス可能な複数のシリアルメモリインタフェースを有し、前記シリアルフラッシュメモリのセクタ消去を行う場合、セクタの消去情報およびセクタデータのバックアップを異なるシリアルフラッシュメモリのセクタに書き込む。

(もっと読む)

半導体装置およびICカード

【課題】強誘電体メモリはアクセス速度が速く、書き換え回数が多い反面、耐ストレス特性(耐熱ストレス特性や耐応力ストレス特性)は劣る。ヒューズメモリは耐ストレス特性が高くデータ保持能力は優れている反面、1回しか書き換えができない。不揮発性メモリを搭載する半導体装置、ICカードにおいて、不揮発性メモリに要求される基本性能を低下させることなく、初期データを確実に保持させることができるようにする。

【解決手段】第1の不揮発性メモリ1と、第1の不揮発性メモリ1よりも耐ストレス特性が高く初期データを格納している第2の不揮発性メモリ2と、第2の不揮発性メモリ2から初期データを読み出し、読み出された初期データを第1の不揮発性メモリ1にコピーして初期化する初期化制御部3とを備える。

(もっと読む)

半導体記憶装置

【課題】書き換え回数に制限のないDRAMを用いることにより長寿命を期待でき、電源断時でもデータの保護が可能な半導体記憶装置の提供を目的とする。

【解決手段】DRAM103と、フラッシュメモリ104と、これらをコントロールするメモリ制御回路105と、外部給電の電圧低下を検出して給電を内部バッテリー107に切替える電源制御回路106を備え、起動時にデータが格納されているフラッシュメモリ104内のデータをDRAM103にコピーし、稼動中はホスト処理装置110とのデータのアクセスはDRAM103上で行い、電源が切断された場合に、バッテリー107により自動でDRAM103のデータをフラッシュメモリ104にバックアップする。

(もっと読む)

メモリシステム

【課題】安価なNAND型フラッシュメモリを使用しつつも、読み出し命令に対するレイテンシをNOR型フラッシュメモリと同程度に抑制することが可能なメモリシステムを得る。

【解決手段】メモリモジュール1のPOR時に、ページP1〜Pnの第1部分P1a〜PnaがNAND型フラッシュメモリ3から読み出され、エラー訂正部7によって所定のエラー訂正処理が行われた後、バッファメモリ6に書き込まれる。コントローラ2がホストシステム8からページの読み出し命令を受けると、制御部4は、NAND型フラッシュメモリ3の比較的大きいレイテンシに起因してNAND型フラッシュメモリ3が待機状態となっている間に、バッファメモリ6からページP1〜Pnの第1部分P1a〜Pnaを読み出して、ホストシステム8へデータ転送する。

(もっと読む)

半導体メモリカードシステムの制御方法

【課題】半導体メモリカードを搭載したホスト機器を含むシステムにおいて、半導体メモリカードの寿命が近づいたことをホスト機器のユーザに警告するための情報を伝達する半導体メモリカードシステムの制御方法を提供する。

【解決手段】本発明の1態様による半導体メモリカードの制御方法は、ホスト機器から半導体メモリカードへのコマンドに応答して該半導体メモリカードの寿命指標データを作成する工程と、前記寿命指標データから寿命管理基準に基づいて前記半導体メモリカードの寿命警告ステータスを作成する工程と、前記コマンドに対する応答として前記寿命警告ステータスを組み込んだレスポンスを前記コマンドと同じ通信ラインを使用して前記ホスト機器に送る工程とを具備する。

(もっと読む)

不揮発性メモリのデータ書込失敗検出方法、およびデータ書込失敗検出システム

【課題】メモリ容量が節約でき、データの修復が可能な、不揮発性メモリのデータ書込失敗検出方法およびデータ書込失敗検出システムを提供する。

【解決手段】複数のバイト21、22から構成されるデータ系列をEEPROM20に書き込むにあたり、データ系列の上位バイト21から下位バイト22まで順に書き込んだ後、上位バイト21に書き込まれたデータと同じデータを、追加バイト23としてEEPROM20に書き込む。そして、データ書込失敗検出システムへの電源投入直後に、最上位バイト21に書き込まれているデータと追加バイト23に書き込まれているデータとが一致しているか否かを検出することでデータ書込失敗を検出する。そして、データ書込失敗を検出した場合に、追加バイト23に書き込まれているデータを上位バイト21に書き込むようにすれば、少なくとも上位バイト21は修復可能である。

(もっと読む)

画像入出力装置及び画像入出力方法

【課題】電源投入時でOSが起動する前のコントローラ内部診断(自己診断)字に、もれなくDRAM−I/Fの結線チェックが出来る画像入出力装置及び画像入出力方法を提供する。

【解決手段】機能限定されたメモリマップ領域内に、すべてのCS領域のメモリ空間をアサインすることにより、電源投入時でOSが起動する前のコントローラ内部診断(自己診断)時に、もれなくDRAM−I/Fの結線チェックが出来る画像入出力装置及び画像入出力方法の提供を実現することができる。

(もっと読む)

121 - 140 / 199

[ Back to top ]