Fターム[5B060CC01]の内容

メモリシステム (7,345) | アクセスタイミング制御 (460) | タイミング信号制御 (406)

Fターム[5B060CC01]の下位に属するFターム

サイクル長制御、ウェイトサイクル制御 (23)

クロック制御(クロック選択、クロック切替) (133)

Fターム[5B060CC01]に分類される特許

41 - 60 / 250

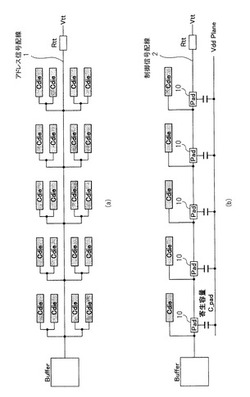

メモリモジュール及び半導体記憶装置

【課題】アドレス信号と制御信号のタイミングの不一致に起因する誤動作が防止できるメモリモジュールを提供する。

【解決手段】メモリモジュールに、データを入出力する単位である複数のランクに区分けされた複数の半導体記憶装置と、全ランクの半導体記憶装置が縦列接続される、外部から入力されたアドレス信号を該半導体記憶装置に供給するための配線であるアドレス信号配線と、ランク単位で半導体記憶装置が縦列接続される、外部から入力された制御信号を該半導体記憶装置に供給するための配線である制御信号配線と、制御信号配線と接続された各半導体記憶装置に対応して設けられた、半導体記憶装置の入力容量と(ランク数−1)との積に等しい容量を持つ容量部とを備える。

(もっと読む)

半導体装置

【課題】クロック信号に同期して動作するメモリにおけるクロック信号と制御信号との位相差を精度よく算出することが可能な半導体装置を提供すること。

【解決手段】SlaveDLL13は、制御信号を所定の範囲内で遅延して出力する。DQS出力位相調整回路12は、SlaveDLL13に制御信号の遅延量を変更させながら得られたDDR3 DIMM2内のサンプリング回路からのサンプリング結果に基づいて、サンプリング回路のセットアップ時間またはホールド時間を満足しないことによって生じるサンプリング結果の不定の範囲を抽出する。そして、抽出された不定の範囲に基づいてクロック信号と制御信号との位相差を求め、制御信号の遅延量を調整する。したがって、クロック信号と制御信号との位相差を精度よく算出することが可能となる。

(もっと読む)

データ記憶装置及びメモリ調整方法

【課題】複数チャネルのキャリブレーションの高速化を実現できるデータ記憶装置を提供することにある。

【解決手段】実施形態によれば、データ記憶装置は、インターフェースと制御モジュールとを具備する。インターフェースは、チャネル毎に、書き換え可能な不揮発性メモリの動作を制御する。制御モジュールは、キャリブレーションの実行時に、前記インターフェースを介して、指定したチャネルに対応する不揮発性メモリに対してキャリブレーション用データを同時に書き込むように制御する。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

メモリインタフェース回路

【課題】マスクタイミングを制御する回路規模を小さい構成で実現すること。

【解決手段】ドライブ制御コードに応じてドライブ特性が変化する第1素子と、I/Oバッファの特性と比例関係にあるドライブ特性の第2素子とを比較し、両素子の特性が一致するか否かを示す調整用モニタ信号を出力するドライブ調整用バッファ20と、調整用モニタ信号に応じて、I/Oバッファの特性と比例関係にあるドライブ制御コードを出力するドライブ能力制御回路14と、システムクロックに応じて、システムクロックの1クロックに相当する遅延値に対応する遅延制御コードを出力する遅延制御回路13と、ドライブ制御コードと遅延制御コードとに基づいて遅延データを計算する遅延計算回路16と、遅延データに基づいて、リード時のデータストローブ信号のマスクタイミングを制御するマスク制御回路17と、を備える。

(もっと読む)

半導体メモリ装置及び半導体メモリ装置を備える半導体システム並びにその動作方法

【課題】データの位相が変動しても、半導体メモリ装置コントローラと半導体メモリ装置との間で安定的にデータが入出力される回路および動作方法を提供すること。

【解決方法】半導体メモリ装置は、トレーニング入力コマンドに応答してノーマルトレーニングデータ(ソースクロックのエッジに基づいてデータウインドウがスキャンされる)の入力を受け、トレーニング出力コマンドに応答してソースクロックのエッジにデータウインドウのエッジが同期した状態で出力する第1データ入出力部と、トレーニング入力コマンドに応答して復旧情報トレーニングデータ(ソースクロックのエッジに基づいてデータウインドウがスキャンされる)の入力を受け、トレーニング出力コマンドに応答してソースクロックのエッジにデータウインドウのエッジが同期した状態で出力する第2データ入出力部(120)とを備える。

(もっと読む)

メモリシステム

【課題】平均消費電流を抑制することが可能なメモリシステムを提供する。

【解決手段】メモリシステムは、データ保持可能な不揮発性の第1のチップ11aと第2のチップ11aとを有するメモリ部11と、ホスト機器200から受信したデータを第1のチップ11aおよび第2のチップ11aに同時に転送するメモリコントローラ12と、予め設定されたずらし時間が経過したことを計測するタイマー22と、ずらし時間の経過直後に、第2のチップ11aへのデータの書き込みを開始させるタイマー制御部18aとを有する。

(もっと読む)

半導体システムのデータ送受信装置および方法

【課題】データの送受信中でも内部クロックをストロボ信号によりトラッキングしてすべてのデータをその有効ウィンドウの範囲内でサンプリングすることができ、よって、データ伝達の信頼性を高めることが可能な、高速で動作する半導体システムのデータ送受信装置および方法を提供すること。

【解決手段】本半導体メモリ装置はストロボ信号の入力を受けてトラッキングクロックを生成するストロボ信号受信部220と、クロックの入力を受けて内部クロックを生成するクロック受信部240と、内部クロックに応じて並列データの入力を受けて内部データを生成する複数のデータ受信部200_0と、データの送受信の間、内部クロックの位相が変動するのを補償するために、トラッキングクロックに応じて内部クロックをトラッキングして内部クロックの位相を調整する位相制御部260を備える。

(もっと読む)

アクセスタイミング調整装置

【課題】システムLSIとメモリ間のアクセスタイミング調整処理の処理時間の短縮を図る。

【解決手段】システムLSI2とメモリ3間の各ビットデータ信号およびデータストローブ信号の配線長情報から算出された遅延調整値の導入によって、アクセスタイミング調整処理をした1ビットデータ以外のビットデータに対しては、上記アクセスタイミング調整結果に、上記遅延調整値を加算した値をアクセスタイミング調整値として設定する。

(もっと読む)

パラメータ設定によるSDRAMコントローラ

【課題】本発明の課題は、パラメータを設定することにより各種SDRAMを共通にコントロールするSDRAMコントローラを提供することにある。

【解決手段】本発明は、FPGA13内の回路として構成され、所定のパラメータに基づいて回路生成を行ってSDRAM14の動作を制御するSDRAMコントローラ25と、前記SDRAMコントローラ25の回路生成を行うパラメータがSDRAM14の仕様に対応して設定されるパラメータ設定部26とを具備することを特徴とするものである。

(もっと読む)

アクセス管理装置、情報処理装置、アクセス管理方法

【課題】複数のプロセッサが共有リソースにアクセスする際の調停頻度を、キャッシュやバッファを抑制するアクセス管理装置、情報処理装置及びアクセス管理方法を提供すること。

【解決手段】複数のプロセッサ11から要求された共通のリソース16へのアクセス要求を制御するアクセス管理装置100であって、複数のプロセッサ11から受け付けたリードアクセスの複数のアドレスを比較するアドレス比較手段13と、複数のアドレスのうち一致したアドレスのデータをリソース16からリードするデータリード手段14と、データリード手段14がリードしたデータを、一致した複数のアドレスを出力した複数のプロセッサ11に同じタイミングで出力するデータ出力手段15と、を有することを特徴とする。

(もっと読む)

制御回路、画像形成装置および外部デバイスアクセス制御方法

【課題】複数のCPUによって外部デバイスに対するアクセスとアクセス設定値変更が同時に発生することによる不具合を効率的に抑制する制御回路を提供する。

【解決手段】制御回路31は、複数のCPUと、複数のCPUに共通に利用され、外部デバイス32,33,34へのアクセスに関する設定値を設定する外部デバイスアクセス設定レジスタ45と、設定値を設定レジスタ45から受け取り、設定値を、外部デバイスへのアクセス状況に応じて更新可能に保持する保持レジスタ62とを含む。アクセスタイミング制御回路63は、保持レジスタ62に保持された設定値に基づいて外部デバイスへのアクセスタイミングを制御する。

(もっと読む)

半導体装置及びシステム

【課題】データ及びデータストローブ信号の伝達経路に差異が発生しても、受信装置が安定的にデータストローブ信号に同期してデータを受信する半導体装置及びシステムを提供すること。

【解決手段】システムは、出力イネーブル信号に応じて第1のデータストローブ信号及び第2のデータストローブ信号を生成するデータストローブ信号生成部と、前記第1のデータストローブ信号に同期してデータを送信するデータ出力部とを備えるデータ送信装置と、前記第2のデータストローブに同期して、前記データを受信するデータ受信装置とを備えることを特徴とする。

(もっと読む)

メモリ制御装置及びマスクタイミング制御方法

【課題】リードデータの受信を確実に行うことができるメモリ制御装置とマスクタイミング制御方法を提供する。

【解決手段】ストローブ信号に同期してデータを受信する同期式のメモリ制御装置において、ストローブ信号をマスク信号を用いてマスクする回路と、ストローブ信号を複数の遅延単位で遅延させそのストローブ信号のデータをラッチするタイミング測定回路と、マスク信号を発生するマスク生成回路とを備え、タイミング測定回路は、ストローブ信号がマスクされた信号の最初の立ち上がりエッジで各遅延されたストローブ信号のデータをラッチし、マスク生成回路は、メモリ回路のコマンド制御回路からの信号に応じてマスク信号の生成を制御し、マスク生成回路は複数の遅延単位で構成した遅延回路を含み、内部クロックに同期してマスク信号の開始タイミングを調整し、遅延回路により選択した遅延単位の遅延量を経た信号をマスク信号として出力する。

(もっと読む)

オンダイ終端回路、オンダイ終端及びトレーニング回路、メモリ装置、終端インピーダンスを提供する方法、オンダイ終端及びトレーニング方法、メモリモジュール、並びにコンピューティングシステム

【課題】非同期的に制御されて電力消耗を削減でき、正確な時点に終端インピーダンスを提供できるオンダイ終端回路とそのトレーニング方法を提供する。

【解決手段】メモリ装置はメモリセルアレイを具備するメモリコア、これにに接続されたデータ入出力ピン、及びオンダイ終端回路を含み、オンダイ終端回路は、データ入出力ピンに終端インピーダンスを提供し、メモリ書き込みコマンドに基づいて生成される非同期制御信号に基づいて終端インピーダンスを入出力データピンに選択的に接続するスイッチング装置を具備する終端回路と、非同期制御信号の終端回路への信号経路を遅延させる非同期遅延部並びに非同期制御信号と基準信号の位相差を比較し、トレーニング結果として位相差を出力する位相検出器及び非同期制御信号の位相検出器への信号経路を遅延させる複製遅延部を具備する比較部を含むトレーニング回路とを含み得る。

(もっと読む)

内部クロックとコマンドとの間のタイミング調整方法、半導体メモリ装置及びメモリシステム

【課題】メモリ装置のギアダウンモード時に、内部クロックとコマンドとの間のタイミングを正確かつ効率的に調整する方法を提供する。

【解決手段】メモリ装置410において、内部クロックINTERNAL_CLKの立上がりエッジと立下がりエッジとでシンクパルスSYNC_PULSEを検出する第1のステップと、シンクパルスSYNC_PULSEの検出結果をメモリコントローラ460に伝達する第2のステップと、メモリコントローラ460がコマンドのタイミングをチューニングする第3のステップとが実行されることを特徴とする。

(もっと読む)

半導体集積回路及びそのタイミング調整方法

【課題】従来技術の半導体集積回路では、タイミング調整に工数がかかるという問題があった。

【解決手段】本発明にかかる半導体集積回路は、外部メモリと接続される複数の信号線に対応して個別に設けられ前記対応する信号線のタイミングを決定する回路ブロックをマクロ化した論理セル群11〜15と、論理セル群11〜15のそれぞれに対応して設けられたIOバッファ21〜26と、を有する。そして、論理セル群11〜15と対応するIOバッファ21〜26とを結合する配線のそれぞれが略同じ長さを有することを特徴とする。

(もっと読む)

DRAMの電力および性能を動的にスケーリングするための方法および回路

【課題】 電力および性能の動的スケーリングをサポートするメモリを提供すること。

【解決手段】 メモリシステムは、高性能モードおよび低電力モードをサポートする。このメモリシステムは、メモリコアおよびコアインターフェイスを含む。メモリコアは、どちらのモードでも同じままであるコア供給電圧を使用する。節電するために、コアインターフェイスの供給電圧および信号速度をスケールダウンすることができる。コアインターフェイスが異なるモードにおいて使用する信号電圧に対応するために、メモリコアとコアインターフェイスとの間のレベルシフタが信号を必要に応じてレベルシフトする。

(もっと読む)

メモリ制御装置

【課題】短時間で動作するメモリ制御装置を提供すること。

【解決手段】メモリ調整部の電源状態がオンからオフに切り替わる場合には、CPUはメモリアクセスI/F部を制御するためのパラメータを算出し、メモリ調整部に接続されたフラッシュメモリにその算出したパラメータを転送する一方、メモリ調整部の電源状態がオフからオンに切り替わる場合には、CPUはフラッシュメモリに転送されたパラメータを設定値格納部に記憶させ、メモリアクセス制御部は、アクセスタイミング設定部に記憶させたパラメータに基づき、メモリアクセスI/F部を制御する。

(もっと読む)

半導体装置及びそのハンドシェイク制御のタイミング設定方法

【課題】従来の半導体装置では、ハンドシェイク制御により動作する論理回路とマクロとの動作サイクルが長くなる問題があった。

【解決手段】本発明にかかる半導体装置の一態様は、論理回路10と、論理回路10が出力する制御信号に応じて論理回路10とのデータの送受信を行い、自マクロ内におけるデータ処理状況に応じて論理回路10に次命令の発行の許可を知らせる命令発行制御信号CCNT1、CCNTm、CCNTnを送信する複数のマクロ11、1m、1nと、を有し、複数のマクロ11、1m、1nは、それぞれ、論理回路10から自マクロへの制御信号の信号遅延時間に応じて命令発行制御信号CCNT1、CCNTm、CCNTnをデータ処理の完了前に出力し、論理回路10は、命令発行制御信号CCNT1、CCNTm、CCNTnに応じて次命令を指示する制御信号を出力する。

(もっと読む)

41 - 60 / 250

[ Back to top ]