Fターム[5B060CC01]の内容

メモリシステム (7,345) | アクセスタイミング制御 (460) | タイミング信号制御 (406)

Fターム[5B060CC01]の下位に属するFターム

サイクル長制御、ウェイトサイクル制御 (23)

クロック制御(クロック選択、クロック切替) (133)

Fターム[5B060CC01]に分類される特許

81 - 100 / 250

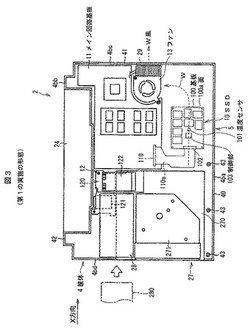

不揮発性半導体メモリドライブ

【課題】不揮発性半導体メモリとメモリコントローラとの間に位置する領域であって、基板の他の領域に比較して高温になる領域の温度を測定することができる不揮発性半導体メモリドライブを提供する。

【解決手段】不揮発性半導体メモリドライブ10は、基板100と、基板100上に設けられた複数の不揮発性半導体メモリと、基板100上に設けられて複数の不揮発性半導体メモリの動作を制御するメモリコントローラ103と、メモリコントローラ103と不揮発性半導体メモリとの間に設けられた温度センサ101とを備え、メモリコントローラ103は、温度センサ101により検出された温度が規定値を超えているとき、外部からの要求に対し、複数の不揮発性半導体メモリから読み出したデータを外部に転送する際の転送速度、又は自己と複数の不揮発性半導体メモリとの間でのデータの転送速度を低下させる。

(もっと読む)

半導体装置と信号伝送システムと信号伝送方法

【課題】レシーバの終端抵抗値やドライバのオン抵抗の決定の最適化を図り、且つ、該決定の工数を削減する半導体装置、システム、方法の提供。

【解決手段】、伝送信号のDC電圧レベルとAC電圧の振幅の一端のレベルを一致させるように、レシーバの終端抵抗値(RTT)やドライバのオン抵抗Ronを調整する。

(もっと読む)

タイミング調整回路及びタイミング調整方法

【課題】入力信号を取り込むタイミングのずれを補正すること。

【解決手段】DLL回路31は、データストローブ信号DQSに基づいて、その信号DQSを遅延させた遅延信号DQSdを生成する。遅延信号DQSdは、位相(タイミング)が互いに異なる複数の遅延信号S(−n)〜S(0)〜S(+n)を含む。ラッチ回路32は、複数の遅延信号S(−n)〜S(0)〜S(+n)によりデータDQをラッチした複数のラッチデータD(−n)〜D(+n)を出力する。位相調整回路33は、複数のラッチデータD(−n)〜D(+n)に基づいて、データDQの第1遷移と第2遷移とを判定し、第1遷移と第2遷移とに応じた期間の中心タイミングを、基準遅延信号S(0)のタイミングを近づけるように、DLL回路31の遅延時間を調整する。

(もっと読む)

メモリデバイスおよびメモリデバイス制御装置

【課題】従来のインタフェースの機器との接続互換性を保ちつつ、データ転送速度を向上できるメモリデバイスおよびメモリデバイス制御装置を提供する。

【解決手段】メモリデバイス103とホスト装置101の間に介在するメモリデバイス制御装置102は、クロック信号に同期してメモリデバイスとの間でデータを転送するデータ転送手段123を備える。データ転送手段123は、クロック信号の立ち上がりエッジ及び立下りエッジの一方に同期してデータを転送するシングルエッジ同期モード、または、立ち上がりエッジと立下りエッジとの双方に同期してデータを転送するダブルエッジ同期モードに対応する。メモリデバイス103がバスマスタとして動作してデータ転送を行う際、データ転送手段123はメモリデバイスに対してダブルエッジ同期モードでデータ転送を行う。

(もっと読む)

画像処理装置、メモリ制御方法、プログラム及び記録媒体

【課題】画像処理装置におけるメモリの動作を制御するためのメモリパラメータの設定を自動で行う際、パラメータの再設定が必要な状況で実施できるようにし、継続的に最適な動作状態を保証する。

【解決手段】メモリの動作に影響する環境の変化(メモリの周囲温度、メモリの作動回路への供給電圧、省エネ遷移など)を捉えるために画像処理装置の動作状態を監視し、監視結果をもとに、設定されたメモリパラメータの適応性の有無を判定し(S106)、この判定により適性が否定される場合に、再設定を実行する(S107)。本発明によると、予め定められた一定期間毎に再設定を行う従来法のように必要な状況で再設定を行わない場合が生じることがなく、最適な動作状態を保証することができる、

(もっと読む)

セルフリフレッシュ・モードのためのメモリ・デバイス制御

【課題】セルフリフレッシュ・モードのためのメモリ・デバイス制御を提供する。

【解決手段】メモリ回路において、メモリ・コントローラがパワーダウンおよびパワーオフされている間、DDR3 RDIMMなどのメモリ・デバイスがセルフリフレッシュ・モードで安全に動作することを保証するために、メモリ・デバイスのクロック・イネーブル(CKE)入力が、(i)メモリ・コントローラによって印加されたCKE信号と、(ii)パワー・モジュールによって供給された終端電圧の両方に接続される。メモリ・コントローラをパワーダウンするために、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは終端電圧をローに駆動し、パワー・モジュールはメモリ・コントローラをパワーダウンする。通常の動作を再開するために、パワー・モジュールはメモリ・コントローラをパワーアップし、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは、終端電圧をパワーアップする。

(もっと読む)

電子機器

【課題】制御部とデバイス部との間でデータを適切に送受可能にする。

【解決手段】電子機器1は、第1信号ADDRと、第1信号ADDRを認識するためのタイミングを規定する第1タイミング信号WRとを出力する制御部17と、第1信号ADDRが入力され、入力された第1信号ADDRを所定時間保持した後に出力する保持部41と、制御部17と保持部41とを接続し、第1信号ADDRを伝送する信号線21と、第1タイミング信号WRが入力され、第1タイミング信号WRのタイミングを調整する第1タイミング調整部42と、保持部41から出力される第1信号ADDRと、第1タイミング調整部42によりタイミングが調整された第1タイミング信号WR_DLYとが入力され、入力された第1タイミング信号WR_DLYに基づいて入力された第1信号ADDRを認識するデバイス部とを有する。

(もっと読む)

同期メモリの読出しデータ収集

【課題】単一の読出し動作でDQSイネーブル信号の最適なタイミングを決定するスナップショットデータトレーニングの方法を提供する。

【解決手段】先ずグレイコードカウントのシーケンスをメモリに書き込み、次いで単一のバーストでそれを読み出すことで実現する。コントローラは、コマンドが発行された時点から一定間隔で読出しバーストをサンプリングし、周回遅延を決定する。簡単な真理値表の検索により、通常読出しに対する最適のDQSイネーブルのタイミングを決定する。通常の読出し動作中、イネーブルされたDQS信号の第1のポジティブエッジを使用して、コマンドが発行されるたびにイネーブルされたカウンタをサンプリングすることが好ましい。カウンタサンプルが変化した場合、これはタイミングの変動が生じたことを示すが、DQSイネーブル信号を調整して変動を補正し、DQSプリアンブルの中央に合わせた位置に保つことができる。

(もっと読む)

メモリ制御システム、メモリ制御方法、メモリ制御手段およびメモリ制御手段における制御方法

【課題】 データストローブ信号に異常が生じた場合であっても、データ要求元がメモリからデータを読み出すことが可能であり、かつ、データ要求元がデータ受取時にデータストローブ信号の異常を認識可能なメモリ制御システム、メモリ制御方法、メモリ制御手段およびメモリ制御手段における制御方法を提供する。

【解決手段】 本発明のメモリ制御システムは、記憶手段とデータ要求元とメモリ制御手段とを備える。データ要求元は、記憶手段に対して読み出し要求を行う。メモリ制御手段は、記憶手段からのデータの読み出し完了を示す通常データストローブ信号を記憶手段から所定時間内に受信しない場合に、擬似的なデータストローブ信号である擬似データストローブ信号を生成し、擬似データストローブ信号に基づき記憶手段からの読み出しデータをデータ要求元に送信するとともに、通常データストローブ信号に異常が生じた旨を示すエラー情報をデータ要求元に送信する。

(もっと読む)

メモリモジュール

【課題】メモリバッファを用いることなく、各チャネルにかかる負荷が低減されたメモリモジュールを提供する。

【解決手段】モジュール基板180と、モジュール基板180に搭載されたメモリチップMC101〜MC172と、メモリチップMC101〜MC172にそれぞれ個別に接続され、リードデータ又はライトデータが伝送されるデータ入出力配線DQL1〜DQL72とを備える。メモリチップMC101〜MC172の数は、データ入出力配線DQL1〜DQL72を介して同時に伝送されるリードデータ又はライトデータのビット数と等しい。このように、複数のデータ入出力配線がそれぞれ個別のメモリチップに接続されていることから、メモリバッファを用いることなく、各チャネルにかかる負荷を低減することが可能となる。

(もっと読む)

同期型データ転送システムおよび同期型データ転送制御方法

【課題】システムが動作中であっても、さらには、小型化・高速化を要する環境下であっても、安定した同期型データ転送の実現が可能な同期型データ転送システムを提供する。

【解決手段】例えばメモリ2からデータ転送用クロック32に同期させてデータ・バス31aを介してデータを転送する際に、データ転送要求受付後最初のデータをメモリコア22から取り出すまでのデータ出力待ち時間を利用して、遅延時間測定データ格納部23に格納している遅延時間測定データ23a〜23cをデータ・バス31aに送信することにより、制御LSI10の遅延時間測定部12にてデータ・バス31aの遅延時間を測定し、遅延調整制御部17は、測定した遅延時間に基づいて、データ・バス31aを介して転送されてくるメモリコア22からのデータを取り込むためのデータ取り込みタイミングを調整して、メモリコントローラ11に供給する。

(もっと読む)

メモリ装置

【課題】数十年以上の単位で記録データを長期的に安定に保存でき、しかも保存データを確実に読み出し可能なメモリ装置を提供する。

【解決手段】第1回路200は、読み出し・書き込み信号が第1レベルのときアドレス信号で指定されたアドレスから記録データを読み出し、読み出し・書き込み信号が第2レベルのとき上記アドレス信号で指定されたアドレスにデータを書き込むデータ記録回路210と、第2回路からの読み出しまたは書き込み指示を受けて、アドレス信号に応じてデータ記録回路に対するデータの書き込みおよび読み出し制御を行い、所定のイベントの発生によりデータ記録回路への読み出し・書き込み信号を第1レベルに設定しデータ記録回路へのデータの書き込み禁止となるように制御する書き込み読み出し制御回路230と、を含む。

(もっと読む)

メモリ制御装置及び制御方法

【課題】消費電力を低減させるとともに、信号品質を維持することが可能なメモリ制御装置及び制御方法を提供すること。

【解決手段】本発明の一態様に係るメモリ制御装置は、ODT(On Die Termination)機能を有する複数のメモリ素子に接続可能なメモリ制御装置であり、診断装置2、メモリ終端抵抗制御部7、ECC回路8を備える。メモリ終端抵抗制御部7は、複数のメモリ素子毎にODTを使用とするか未使用とするかを制御するためのODT制御信号を出力するECC回路8は、複数のメモリ素子から送出されるデータのエラーを検出する。診断装置2は、システム運用中において、ODT使用状況及びエラーの情報に基づいて、複数のメモリ素子のODT使用設定を切り換える。

(もっと読む)

起動時にハードウェアの調整を行うシステムおよび調整方法

【課題】起動時にハードウェアの調整を行うシステムにおいて、調整の精度の向上と、システムの起動時間の短縮とを、併せて実現する。

【解決手段】システムの起動時にシステムが正しく動作するようにハードウェアを調整するキャリブレーション実行部142と、このキャリブレーション実行部142により調整されたハードウェアの設定を示す補正情報を、調整が行われたときの環境条件に対応付けて保持する補正データ保持部143とを備える。そして、キャリブレーション実行部142は、システムが起動されたときの環境条件に相当する環境条件に対応付けられた補正情報が補正データ保持部143に保持されている場合には、ハードウェアを調整する代わりに、保持されている補正情報に基づいてハードウェアの設定を行う。

(もっと読む)

メモリ制御装置、及びメモリ制御方法

【課題】アプリケーションにブランキング期間が無くても、メモリアクセスタイミングを調整することができるメモリ制御装置を提供することである。

【解決手段】本発明にかかるメモリ制御装置は、データストローブ信号を遅延させる遅延回路3と、遅延回路3により遅延された少なくとも2つのデータストローブ信号に基づき、メモリからのデータ信号のデータ値を各々格納する少なくとも2つのFIFOバッファ部7、8、9を有する。更に、少なくとも2つのFIFOバッファ部に格納されたデータ値を比較する比較器4と、比較器4の比較結果10に基づき、遅延回路3を用いてデータストローブ信号の遅延時間を制御する制御回路3を有する。そして、少なくとも2つのFIFOバッファ部に格納されたデータ値のうちの一つは通常動作にも使用される。

(もっと読む)

メモリ制御装置及びその制御信号出力タイミングの調整方法

【課題】メモリ制御信号とクロックとの関係を容易に把握することができ、メモリ制御信号とクロックとのセットアップホールドに対するマージンを拡大する。

【解決手段】メモリ制御装置は、半導体記憶装置にデータを書き込むメモリ制御装置であって、前記半導体記憶装置を制御する制御信号を遅延させて、前記半導体記憶装置に出力する位相調整回路と、前記制御信号に応答して前記半導体記憶装置から入力されるデータストローブ信号を監視し、前記制御信号が出力されてから前記データストローブ信号が入力されるまでの応答時間に対応する応答信号を出力するデータストローブ監視回路と、を有し、前記位相調整回路の遅延量は、前記半導体記憶装置に、前記遅延量を順次増加させながら前記制御信号を出力して前記応答信号が出力されるタイミングを監視したときに、前記タイミングが変化した遅延量に対して前又は後にずらした値に設定する。

(もっと読む)

スタックダイメモリシステムおよびスタックダイメモリシステムをトレーニングするための方法

一組のデータビットを1つまたは複数の送信レジスタにクロッキングするよう1つまたは複数のデータクロックと関連する一組の遅延を制御する、一組のデータビットを少なくとも1つの受信レジスタを伝達するよう1つまたは複数のデータストローブを制御する、および/またはスタックダイメモリボールトと関連するダイ上のメモリアレイにアクセスするよう一組のメモリアレイタイミング信号を制御するように動作させるもの等の、システムおよび方法を本明細書に開示する。本明細書のシステムおよび方法はまた、スタックダイメモリボールトと関連する、データアイトレーニング動作および/またはメモリアレイタイミングトレーニング動作を実施するものを含む。 (もっと読む)

パルス生成システムおよび方法

特定の一実施形態において、デバイス(102)は、制御電圧を生成するための基準電圧回路(110)を備える。デバイスは、プリセットされた周波数を有する周波数出力信号(328)を生成するように構成されている周波数回路(106)およびプリセットされた周波数に基づいてカウント信号(310)を生成するためのカウンタ(304)を備える。デバイスは、カウント信号を受信し、遅延デジタル出力信号(312)を生成するために結合されている遅延回路(306)およびパルス(130)を生成するためのラッチ(320)も備える。パルスは、書き込みコマンドに応答する最初のエッジ(132)と遅延デジタル出力信号に応答して形成される立ち下がりエッジ(134)とを有する。特定の一実施形態において、パルス幅は、メモリの素子にデータを書き込むことを可能にするように臨界電流を超えるが、所定の閾値を超えない印加電流レベルに対応する。  (もっと読む)

(もっと読む)

メモリ制御システム、メモリ制御方法、メモリ制御プログラム及び記録媒体

【課題】メモリ動作を決定する複数のパラメータを適切な値に調整する。

【解決手段】複数のパラメータが取り得る値の複数の組み合わせを管理するパラメータ管理部11aと、パラメータ管理部11aによって管理されている複数の組み合わせを複数のパラメータに順次設定するパラメータ設定部11dと、パラメータ設定部11dによって複数の組み合わせが複数のパラメータに順次設定される都度、メモリ2とメモリコントローラ12との間のメモリ動作の試験を行い、その試験の判定結果を蓄積するパラメータ試験部11bと、パラメータ試験部11bに蓄積された試験の判定結果に基づいて、複数の組み合わせの中の1組を決定するパラメータ決定部11cと、を備え、パラメータ設定部11dは、パラメータ決定部11cによって決定された複数の組み合わせの中の1組を複数のパラメータに設定する。

(もっと読む)

メモリ制御回路

【課題】メモリ動作時の消費電力を低減することができるメモリ制御回路を提供する。

【解決手段】メモリ制御回路は、メモリとして、例えばDDRメモリの動作を制御するものであり、DDRメモリのRASN端子,CASN端子,WEN端子,ADD端子およびBA端子に入力するそれぞれの信号を出力するスリーステートバッファと、DDRメモリが動作時に、該DDRメモリのCSN端子に入力されるCSN信号またはこれに対応する当該メモリ制御回路の内部信号に基づいて、スリーステートバッファに入力される出力イネーブル信号を生成する生成回路とを有する。ここで、スリーステートバッファは、出力イネーブル信号がアクティブ状態の期間、動作状態となり、出力イネーブル信号が非アクティブ状態の期間、出力がハイインピーダンス状態となることにより、上記課題を解決する。

(もっと読む)

81 - 100 / 250

[ Back to top ]