Fターム[5B060CC01]の内容

メモリシステム (7,345) | アクセスタイミング制御 (460) | タイミング信号制御 (406)

Fターム[5B060CC01]の下位に属するFターム

サイクル長制御、ウェイトサイクル制御 (23)

クロック制御(クロック選択、クロック切替) (133)

Fターム[5B060CC01]に分類される特許

21 - 40 / 250

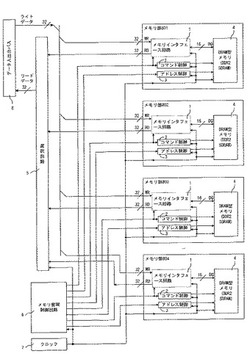

DRAM型メモリシステムおよびメモリ管理制御方法

【課題】DRAM型メモリを用いてデータの効率的な連続読み出しおよび書き込みをを実現し、FIFO形式でのデータの取り扱いを可能にするDRAM型メモリシステムおよびメモリ管理制御方法を提供する。

【解決手段】DRAM型メモリ(4)とインタフェース回路(1)とをそれぞれ含む複数のメモリ部(#01−#04)と、複数のメモリ部に対してライトデータを与えリードデータを取り出すデータ入出力部(5,8)と、複数のメモリ部の各々を同一の固定サイクル長で動作させライトデータの書き込みおよびリードデータの読み出しがそれぞれ連続実行されるようにメモリ部間で固定サイクル長の開始タイミングを設定するメモリ管理制御部(6)を有する。

(もっと読む)

システム、システムにおける調整装置、およびシステムの制御方法

【課題】半導体装置のタイミング調整を最適に行うシステム、システムにおける調整装置、システムの制御方法を提供する。

【解決手段】メモリチップを有する複数の半導体装置30と、複数の半導体装置のいずれかの半導体装置に、予め調整対象とされている被調整信号のタイミングと、被調整信号のハイレベルとローレベルとを判別するための参照電圧と、を段階的に変更させてシュム−データを取得するメモリコントローラ20と、メモリコントローラにより取得されたシュム−データに基づき被調整信号のタイミングと参照電圧との関係の最適ポイントを算出する演算部12と、を備え、メモリコントローラは、演算部が算出した最適ポイントを示す情報に基づき調整される信号のタイミング及び参照電圧を複数の半導体装置のそれぞれに対して調整する。

(もっと読む)

相互接続システム

【課題】コンピュータ又は遠隔通信システムの構成要素と共に使用する相互接続システムを提供する。

【解決手段】データメモリシステム、コンピュータシステム、又はデータ経路がシステムの電力消費及びデータスキュー特性を制御するように配置されて作動される通信システムとすることができる、ネットワークにおいて要素を配置するための相互接続システム、装置、及び方法。構成可能なスイッチング要素を使用して、ノードでの相互接続を形成することができ、制御信号及び他の情報を使用して、構成可能なスイッチング要素の他の態様の電力ステータスが管理される。ネットワークのノード間で送信されているデータの時間遅延スキューは、ネットワークの1つ又はそれよりも多くのノードでデータの論理的及び物理的ライン割当てを交換することによって変更することができる。また、トレース経路指定の複雑さを低減する相互接続マザーボードを配置する方法も開示する。

(もっと読む)

光トランシーバ

【課題】回路規模の増大を抑えつつ、Digital Diagnostic Monitorへのアクセスの待ち時間を低減させる。

【解決手段】光トランシーバ10では、セレクタ20が、不揮発性メモリへのアクセス時に第1のI2CバスB1を選択し、監視部へのアクセスの際には第2のI2CバスB2を選択する。この光トランシーバ10では、不揮発性メモリ12がアクセスされている間に監視部14へのアクセスが開始される時に、停止信号が第1の制御部16aに出力され第1の制御部16aによる不揮発性メモリ12のアクセスを中断させ、第2のI2CバスB2を選択させるための切替信号がセレクタ20に出力される。セレクタ20は、切替信号に応答して、第1のI2CバスB1に出力する信号の状態を直前の状態で維持して、第2のI2CバスB2を選択する。

(もっと読む)

メモリインタフェース回路

【課題】データストローブ信号に発生するグリッジを有効に除去し、正確なデータ転送を可能にするメモリインタフェース回路を提供する。

【解決手段】システムクロック信号CLKに同期したマスク制御信号RENをある遅延調整値αだけ遅延させた信号を用いてデータラッチに使用するようにデータストローブ信号DQSをマスクする第1のマスク回路103と、遅延調整値αに一定の余裕度tを持たせてマスク制御信号RENを遅延させた信号を用いてデータストローブ信号DQSをマスクする第2のマスク回路104と、第1のマスク回路103の出力におけるエッジ回数のカウント値と第2のマスク回路104の出力におけるエッジ回数のカウント値とを比較して、両カウント値の一致を確認しつつ遅延調整値αを変更し、不一致が起こった場合には遅延調整値αを戻すように動作する比較回路1112とを設ける。

(もっと読む)

半導体装置

【課題】レジュームモードからノーマルモードに復帰する際のラッシュカレント(突入電流)のピーク電流を低減することができる半導体装置を提供する。

【解決手段】半導体装置は、複数のディジーチェン接続されたメモリモジュールを備える。各メモリモジュール77−iは、メモリアレイ4と、レジュームモードにおいて、メモリモジュール内の構成要素への電源電圧の供給を制御するスイッチ16と、レジュームモードからノーマルモードへの移行を指示するレジューム制御信号を受けて、次段のメモリモジュールへ、入力されたレジューム制御信号よりもタイミングが遅延したレジューム制御信号を次段のメモリモジュールへ出力する遅延回路42とを含む。

(もっと読む)

メモリインターフェイスのタイミング調整回路および方法

【課題】入力されたデータストローブ信号の位相に応じて、そのゲートタイミングを調整することのできるメモリインターフェイスのタイミング調整回路および方法を提供する。

【解決手段】実施形態のタイミング調整回路は、サンプリング部11が、位相の制御されたサンプリングクロックによりデータストローブ信号DQSを所定回数サンプリングし、初期値設定部12が、プルダウン回路2が動作しているときのサンプリング結果より、原ゲート信号の移相量の初期値を設定し、補正部13が、プルダウン回路2が動作していないときのサンプリング結果より、設定された移相量の補正方向を決定する。初期値設定部12または補正部13からの出力にもとづいて移相量決定部14が決定した移相量に合わせて、遅延部15が、原ゲート信号を遅延させて、データストローブ信号DQSをゲーティングするためのゲート信号を出力する。

(もっと読む)

メモリインターフェース回路、メモリインターフェース方法、および電子機器

【課題】回路規模を抑え、複雑な制御を必要とせずに、データストローブ信号がハイインピーダンス状態にある場合に内部にリードデータ信号の誤取り込みを防止して、安定的にメモリからデータを読み出すことが可能なメモリインターフェース回路を提供すること。

【解決手段】DQS信号が伝播するDQS線DQSLをローレベルにクランプするクランプ回路11と、リードイネーブル信号RENに応じて、DQS線DQSLを介して入力されるDQS信号の論理レベルの検出を開始するアンド回路10とを備え、クランプ回路11を設けることにより、読み出し動作において、DQS線DQSLは接地電位にクランプされる。よって、DQS線DQSLがハイインピーダンス状態に維持されることはなく、ノイズ等によりDQS線DQSLに生じる不測のエッジを検出することはない。DQS信号を誤検出することはなく、誤ったDQ信号を取り込む恐れがない。

(もっと読む)

半導体記憶装置

【課題】セットアップ及びホールド時間のマージンを確保する。

【解決手段】半導体記憶装置1は、第1のクロックを受け、かつデータの入出力を行う第1のバッファ12を有する第1のメモリ10と、データの入出力を行う第2のバッファ22を有する第2のメモリ20とを含む。第1のメモリ10は、第1のクロックを用いて第2のメモリ20に第2のクロックを転送する。第1のバッファ12は、第1のクロックに応答して第2のメモリ20にデータを転送する。第2のバッファ22は、第2のクロックに応答してデータを受ける。

(もっと読む)

半導体システム、半導体メモリ装置及びこれを用いたデータ出力方法

【課題】データ入出力マージンを向上させ、低い電力消耗量でデータを安定的に出力できる半導体システム、半導体メモリ装置及びこれを用いたデータ出力方法を提供する。

【解決手段】半導体システム100は、クロック信号、データ出力命令語、アドレス信号及び第2ストローブ信号をメモリ装置へ伝送するコントローラ110及びコントローラ110から伝送されるクロック信号、データ出力命令語、アドレス信号及び第2ストローブ信号に応答して、第2ストローブ信号に同期されたデータをコントローラへ提供するメモリ装置120を含む。

(もっと読む)

メモリシステム

【課題】高いクロック周波数でデータを出力するメモリシステムを提供する。

【解決手段】データDout及び第1信号(切替信号)を保持可能なメモリセル10と、第2信号(VHF)と第3信号(RM)とを保持する保持部61と、前記データを出力する出力部とを備え、前記出力部は前記データを外部に出力する第1〜第3トランジスタを備えたバッファ部93とを具備し、周波数は、第1周波数(非同期、66、83MHz)及びこの第1周波数よりも大きな第2周波数(104MHz)を含み、前記周波数が、前記第2周波数である場合、前記第1制御信号(<A>、<B>、<C>)の値に関わらず、前記第1〜第3トランジスタをオン状態とすることができる。

(もっと読む)

メモリインターフェース回路及び半導体装置

【課題】通常のメモリアクセスを中断することなくストローブ信号とデータ信号との間のタイミング調整することができる、小型のメモリインターフェース回路を提供すること。

【解決手段】期待値取得用ラッチ12は、クロック信号CLKに同期してライトデータWDをラッチする。WDLL31は、ライトストローブ信号WDQSを出力する。RDLL32は、遅延ライトストローブ信号WDQS_dを出力する。リードデータラッチ11は、ループバックされたライトデータWDを遅延ライトストローブ信号WDQS_dに同期してラッチする。比較器41は、リードデータラッチ11及び期待値取得用ラッチ12の出力を比較する。レジスタ部43は、RDLL32に設定する遅延値が格納される。レジスタ制御部42は、比較結果に応じてレジスタ部43内の遅延値を更新する。遅延選択部44は、レジスタ部43から読み出した遅延値をRDLL32に設定する。

(もっと読む)

受信回路、システム装置及び半導体記憶装置

【課題】タイミングエラーの発生を抑制することのできる受信回路を提供する。

【解決手段】受信回路40は、データ列DQの先頭のデータをラッチするためのセットアップタイム及びホールドタイムを満たすタイミングでデータストローブ信号DQSの先頭の立ち上がりエッジが発生するように、データストローブ信号DQSに第1の遅延量を与える第1遅延回路42を含む。受信回路40は、データ列DQの3番目のデータをラッチするためのセットアップタイム及びホールドタイムを満たすタイミングでデータストローブ信号DQSの2番目の立ち上がりエッジが発生するように、データストローブ信号DQSに第2の遅延量を与える第2遅延回路43を含む。受信回路40は、第1遅延信号DQS1の先頭立ち上がりエッジでラッチした先頭データと、第2遅延信号DQS2の2番目の立ち上がりエッジでラッチした3番目のデータを選択する選択回路S1を含む。

(もっと読む)

不揮発性メモリの読み出し動作変更

【課題】不揮発性メモリが揮発性メモリに競争し得るように、不揮発性メモリデバイスのメモリアクセス時間を削減する。

【解決手段】読み出しアクセス100の特定部分が実行される順番を変更することによって、読み出しアクセスを変更する。プレアクティブコマンドは、ロウアドレス書き込み動作130から構成される。アクティベートコマンドは、読み出しコマンドを導出する多数の動作から構成される。矢印150は、ビット線プレチャージ及びカラム選択動作136が、アクティベートコマンドからプレアクティブコマンドに移動されることを示す。このような移動は、プレアクティブコマンドの持続期間を延長するが、アクティベートコマンドの持続期間を短縮する。実行されたアクティベートコマンドの数が実行されたプレアクティブコマンドの数よりも大きい場合、読み出しアクセスの持続期間を短縮する。

(もっと読む)

メモリコントローラ、これを備えたメモリシステム及びメモリデバイスの制御方法

【課題】データの信頼性を確保したままライト/リード動作の高速化を実現する。

【解決手段】本発明に係るメモリコントローラは、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、ライト動作においてデータ制御回路により生成される、ライトストローブ信号のタイミングをメモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作においてメモリデバイスにより生成される、リードストローブ信号のタイミングをメモリアクセス単位毎に調整し、データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有する。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

キャリブレーション装置、キャリブレーション方法

【課題】 キャリブレーションを定期的に行うシステムにおいて、キャリブレーション毎に、キャリブレーション開始時の遅延量を基準に所定の範囲で増減し、増減した各遅延量でのデータのラッチ、チェックパターンとの比較といった動作確認が必要であり、キャリブレーションに多くの時間を要している。

【解決手段】 キャリブレーション履歴から、遅延量が増加傾向にあれば遅延量を増加しての動作確認を、遅延量が減少傾向にあれば遅延量を減少しての動作確認を省略することで、キャリブレーションに要する時間を短縮することが可能になる。

(もっと読む)

インターフェース回路及びインターフェース回路を備えるメモリコントローラ

【課題】ロックアップ時間無しでDDRインターフェースを備えたメモリにアクセスすることのできるインターフェース回路及びインターフェース回路を備えるメモリコントローラを提供する

【解決手段】データストローブ信号(DQS)の周期が基本クロックの周期の4n倍(nは1以上の整数)になるようにする。このようにすることにより、データストローブ信号(DQS)がハイレベルの期間又はローレベルの期間は、基本クロックの2n周期分の期間と一致する。そして、データストローブ信号(DQS)の立ち上がりエッジ又は立ち下がりエッジから基本クロックのn周期分に対応する時間が経過した時点を中心として、半周期分未満の時間差で読み出しデータ(DQ)の信号がラッチする。

(もっと読む)

メモリシステム及びその制御方法

【課題】メモリデバイス間における遅延時間のばらつきを解消する。

【解決手段】データ端子20dがメモリコントローラ30に共通接続されたメモリデバイス21〜24を備える。メモリデバイス21〜24のそれぞれは、リードコマンドに応答してメモリセルアレイ100から読み出されたリードデータDataをデータ端子20dに出力するデータ出力回路120と、データ出力回路120によるリードデータDQの出力タイミングを調整する出力タイミング調整回路130とを備える。メモリコントローラ30は、メモリデバイス21〜24にそれぞれ設定コマンドを発行することにより、リードコマンドを発行してからリードデータDQを受信するまでの遅延時間がメモリデバイス21〜24間において一致するよう、出力タイミング調整回路130による調整量を設定する。

(もっと読む)

電子機器

【課題】アクセスを制御する半導体部品に負担をかけることなく当該半導体部品が出力する信号の高調波成分によって当該信号によるタイミングウインドウが不所望に狭められことを抑制する。

【解決手段】基板上でアクセスを制御する半導体部品が出力するクロック信号やコマンド及びアドレス信号の有効性を示すイネーブル制御信号を基板上でアクセスされる別の半導体部品に供給する信号伝送経路の所定ノードから分岐してグランドプレーンに至る特定伝送経路に容量素子を直列配置する。前記容量素子は、イネーブル制御信号の高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記イネーブル制御信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。

(もっと読む)

21 - 40 / 250

[ Back to top ]