Fターム[5C006BF37]の内容

液晶表示装置の制御 (150,375) | 機能素子(画素単位回路含まず) (24,965) | コンデンサ (726)

Fターム[5C006BF37]に分類される特許

1 - 20 / 726

データドライバ、表示パネル駆動装置及び表示装置

電気光学表示装置および電子機器

【課題】電気光学表示装置において負荷変動により発生する表示品位の低下を防止する。

【解決手段】表示装置は、1本の走査線135に選択電圧が印加されることに応じて該1本の走査線に対応する画素列に含まれる画素へのデータ線134を介した画素電圧の印加を可能とする複数の画素スイッチング素子136と、複数のデータ線に供給可能なサンプリング用電圧を1本の走査線に選択電圧が印加される期間において単調変化させる電圧生成部300と、順次選択した1本の走査線に選択電圧を印加する走査線駆動回路120およびデータ線へのサンプリング用電圧の供給をオン/オフするデータ線スイッチ133とを有する。同一の画素電圧がサンプリングされた画素の数である同一電圧サンプリング数を検出し、検出された同一電圧サンプリング数が所定数である場合にサンプリングを一時的に停止させ、かつ電圧生成部でのサンプリング用電圧の単調変化を停止させる。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、共通電圧の電位変動をキャンセルし、液晶表示パネルに表示する画面の画質が劣化するのを防止し、高品位の画像を提供する。

【解決手段】各画素が、画素電極と、対向電極とを有し、1表示ライン上の互いに隣接する2つの画素を画素Aと画素Bとするとき、映像電圧の書き込み時に、前記画素Aの前記画素電極に対して前記対向電極に供給される前記共通電圧よりも高電位の映像電圧を印加し、前記画素Bの前記画素電極に対して前記対向電極に供給される前記共通電圧よりも低電位の映像電圧を印加する液晶表示装置であって、前記対向電極の複数箇所の電位変動を検出し、前記共通電圧生成回路にフィードバックするフィードバック手段を有し、前記共通電圧生成回路は、前記フィードバック手段によりフィードバックされた電位変動に基づき、基準共通電圧に電位変動を相殺する逆補正電圧を重畳した共通電圧を前記対向電極に対して供給する。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

電気光学装置及び電子機器

【課題】極性反転駆動を行う際、極性反転に伴って、画素電極に導通する保持容量を切り換えることのできる電気光学装置、および電子機器を提供する。

【解決手段】電気光学装置において、画素電極9aの電位が共通電極21の電位より高い第1期間では、第1保持容量80aが画素電極9aに導通状態となるので、第1電極81、第1誘電体層86(第1絶縁材料/シリコン酸化膜/SiO2)、第2誘電体層87(第2絶縁材料/シリコン窒化膜/SiN)、および第2電極82に向けて電流が流れ、電荷が蓄積される。これに対して、画素電極9aの電位が共通電極21の電位より低い第2期間では、第2保持容量80bが画素電極9aに導通状態となるので、第4電極84、第4誘電体層89(第1絶縁材料/シリコン酸化膜/SiO2)、第3誘電体層88(第2絶縁材料/シリコン窒化膜/SiN)、および第3電極83に向けて電流が流れ、電荷が蓄積される。

(もっと読む)

半導体装置

【課題】単極性のTFTを用いて構成するデジタル型式の表示装置において、消費電流を低減することの出来る回路を提供する。

【解決手段】デジタル映像信号の保持を行うラッチ回路であって、TFT101の入力電極にデジタル映像信号が入力されると、TFT101の出力電極からは非反転出力信号が出力され、TFT102およびTFT103の出力電極からは反転出力信号が出力されるラッチ回路を提供する。出力を非反転、反転の2系統得られるため、後段のバッファを駆動する際に、電源間の直流パスが生ずる期間を短くすることが出来、消費電流の低減に寄与する。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

駆動回路及び表示装置

【課題】より多相のクロックを用いた場合であっても、安定した走査信号を出力し、表示品質の高い表示装置を提供する。

【解決手段】駆動回路は、一の出力回路は、走査信号線(Gn)と、該走査信号線とクロック信号線(Vn)との電気的接続を制御する第1トランジスタ(T5)と、第1トランジスタのゲートに接続され、走査信号線にアクティブ電位が出力される期間を含む期間である第1期間にアクティブ電位となる第1ノード(N1)と、トランジスタを導通させない電位である非アクティブ電位を保持する非アクティブ信号線(VGPL)と第1ノードとを、第1期間以外の期間である第2期間において電気的に接続するように制御する第2トランジスタ(T2)と、第2トランジスタのゲートに接続された第2ノード(N2)と、を有し、第2ノードは、アクティブ電位を保持するための2種類の充電されるタイミングを有している。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】非選択期間において、出力信号のノイズが小さく、且つトランジスタの特性劣化を抑制できる液晶表示装置の駆動回路を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを設け、第1のトランジスタにおいて、第1端子を第1の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第5の配線に接続し、第2のトランジスタにおいて第1端子を第3の配線に接続し、第2端子を第6の配線に接続し、第3のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第4の配線に接続し、第4のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第6の配線に接続し、ゲート端子を第4の配線に接続する。

(もっと読む)

表示装置

【課題】 電位変動の影響を受けた画素による表示品質の低下を抑制できる表示装置を提供する。

【解決手段】 複数の画素Pが複数のソースラインSLと複数のゲートラインGLの交差部の夫々に対応配置され、同じソースライングループGに属するソースラインSLの夫々がスイッチ素子SWを介して基幹ソースラインSOに接続し、ゲートラインGLの1つが選択されている1つの連続した選択期間内において、同じソースライングループGに属するソースラインSLを所定の選択順序で順次選択して、基幹ソースラインSOを介して駆動電圧を印加する電圧印加処理を実行する駆動処理を実行するように構成され、選択順序を変更するタイミングを規定したタイミングルールと、選択順序の変更方法を規定した順序ルールを含む変更ルールに基づいて、駆動処理におけるソースラインの選択順序を変更する。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

ディスプレイパネル及びその動作方法

【課題】グレーレベルの数を増やすよう動作するマルチビットメモリとしてのピクセル素子を有するディスプレイパネル等を提供する。

【解決手段】ディスプレイパネルは、画像データを保持する画像データ保持キャパシタと、サンプル制御信号を受け取る制御端子を有するサンプルユニットと、サンプルユニットを介して画像データ保持キャパシタの画素電極に結合される第1の端子を有する容量素子と、第1の端子に結合される制御端子を有する第1のリフレッシュユニットと、リフレッシュ制御信号を受け取る制御端子を有する第2のリフレッシュユニットと、画素電極に結合される制御端子、第1の端子に結合されるデータ端子、及びシャント制御信号を受け取る他のデータ端子を有するシャントユニットとを有する。第1及び第2のリフレッシュユニットは、データ信号を受け取るよう対応するソースラインと画像データ保持キャパシタとの間で互いに直列に結合される。

(もっと読む)

ピクセル素子、そのディスプレイパネル、及びその制御方法

【課題】電力消費が低減されるピクセル素子、ディスプレイパネル、及びその制御方法を提供する。

【解決手段】方法は複数のステップを有する。画像データはディスプレイパネルの画像データ保持キャパシタに保持される。サンプル動作が実行され、画像データを容量素子に記憶する。容量素子に記憶された画像データに基づき、リフレッシュ動作が実行され、画像データ保持キャパシタに記憶されている画像データをリフレッシュする。リフレッシュされた画像データは、サンプル動作において画像データ保持キャパシタに保持されている画像データの極性と同じ極性を有する。

(もっと読む)

表示装置駆動回路

【課題】表示装置駆動回路の回路面積の削減を図ることである。

【解決手段】本発明に係る表示装置駆動回路は、入力データに対応するデータ対応幅DWを生成するデータ対応幅発生回路101と、順次シフトされるイネーブル情報OEに応じて、データ対応幅DWを出力する幅伝達部103と、定電流源104を用いてデータ対応幅DWに応じて充電され、駆動電圧を保持するコンデンサ112、115とを備え、駆動電圧を出力するものである。

(もっと読む)

シフトレジスタ駆動方法並びにシフトレジスタ及びこれを備える液晶表示装置

【課題】大画面、高解像度のa−Si TFT LCDに適用可能にする。

【解決手段】複数のステージを含み、ステージの奇数番目及び偶数番目にそれぞれ第1及び第2クロック信号が入力されて、各ステージに対応するスキャンラインを駆動する駆動信号を出力するシフトレジスタの駆動方法において、第1電源電圧に相応する第1ハイレベルの第1又は第2クロック信号をステージに提供し、第1ハイレベルより大きな第2ハイレベルの第2電源電圧を生成してステージに提供し、第1又は第2クロック信号のデュティ期間に現ステージに接続されたスキャンラインをプルアップさせる駆動信号を生成し、直後ステージの駆動信号に応答して、現ステージの駆動信号をローレベルにダウンさせて現ステージに接続されたスキャンラインにローレベルにダウンされた駆動信号を提供し、現ステージの駆動信号をローレベルに所定時間維持することを含むシフトレジスタ駆動方法。

(もっと読む)

アレイ基板及び液晶表示装置

【課題】 N型のみのトランジスタで補助容量線駆動回路を形成することができ、補助容量線を安定して駆動することができるアレイ基板及び液晶表示装置を提供する。

【解決手段】 アレイ基板は、複数の画素と、複数本の補助容量線Csと、第1入力端子Tin1、第2入力端子Tin2及び出力端子Toutを有し、第1補助容量電圧又は第2補助容量電圧を出力端子から出力する複数の補助容量電圧選択回路7を含んだ補助容量線駆動回路と、を備えている。補助容量電圧選択回路7は、N型の第1乃至第6トランジスタTr1乃至Tr6と、電位制御機構と、を有している。電位制御機構は、第1トランジスタTr1のゲート電極に接続され、第3トランジスタTr3が導通状態から非導通状態に切替わってから第5トランジスタTr5が非導通状態から導通状態に切替わるまでの期間に、第1トランジスタのゲート電極の電位を制御し、第1トランジスタを導通状態に保持する。

(もっと読む)

電源回路およびそれを用いたディスプレイ装置

【課題】正常に起動可能な液晶パネル用の電源回路を提供する。

【解決手段】スイッチングレギュレータ制御部40は、スイッチングレギュレータ102のスイッチング動作を制御するとともに、そのスイッチングに応じたパルス信号LX_AVDDを、本電源回路100に外付けされる負電圧チャージポンプ回路24に出力する。ロジック部30は、(a)電源回路100の動作開始が指示されると、ハイサイドトランジスタM1およびローサイドトランジスタM2をともにオフとし、レベルシフタ22の出力端子をハイインピーダンス状態とし、(b)入力電圧VINが所定レベルに達すると、スイッチングレギュレータ制御部40にスイッチング動作の開始を指示し、(c)電源回路100の起動が完了するとレベルシフタ22のハイインピーダンス状態を解除する。

(もっと読む)

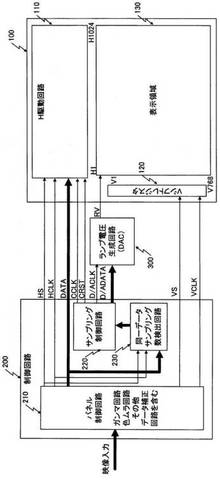

表示装置および表示素子の駆動制御方法

【課題】表示素子の実際の静電容量を、ダミー画素など余分な画素を設けること無しに検出して、検出結果に応じて最適な駆動条件を高速に自動調整する表示装置の実現。

【解決手段】駆動された後駆動が解除された後も表示状態を維持するメモリ性を有する表示素子10と、表示素子が呈する静電容量を検出する静電容量検出回路14と、表示素子を所定の駆動条件で駆動して表示状態を設定した後、静電容量検出回路が検出した表示状態を呈する表示素子の静電容量に基づいて、表示素子の駆動条件を自動調整する駆動条件調整回路23,24と、を有し、駆動条件調整回路は、検出した静電容量と、記憶された前記静電容量の差に応じて、調整シーケンスを変更する表示装置。

(もっと読む)

1 - 20 / 726

[ Back to top ]