Fターム[5C051DB06]の内容

ファクシミリ用ヘッド (33,712) | ヘッドの構成要素 (10,809) | 配線;電極 (315)

Fターム[5C051DB06]に分類される特許

61 - 80 / 315

画像読取装置及びそれを用いた画像形成装置

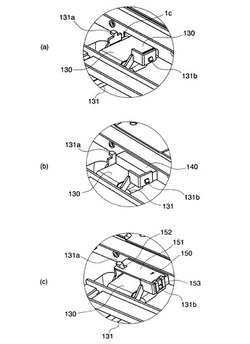

【課題】画像読取装置において、フレームに設けられている電気ケーブル用開口を介してそのフレーム内と画像形成装置本体内とを電気的に接続するための電気ケーブルを、その開口を閉塞しながら安全に固定することを目的とする。

【解決手段】電気ケーブル用開口1cを閉塞する弾性部材140と、その弾性部材140をフレームに対して固定するホルダ150とを備えている。

(もっと読む)

画像読取装置

【課題】下側ユニット及び上側ユニットを備える画像読取装置において、上側ユニット内部に配線される画像データ伝送用のケーブルにかかるストレスを軽減すること。

【解決手段】複合機1において、第二FFC52は、第二イメージセンサ12側の端部から連続する部分が、カバー部7の後方へと延び、カバー部7の後端に達したところで、カバー部7の後端に沿って右方へと延びている。そして、第一FFC51の後方へと延びる部分に重なる位置に達したところで、カバー部7の後方へと延びている。さらに、この後方へと延びた部分から連続する部分は、カバー部7の上下動を許容する形態に湾曲してから正面側へと延びて、メインユニット2の内部へと導入されている。そして、メインユニット2の内部へと導入された部分から連続する部分が、制御基板47へと至り、制御基板47に接続されている。

(もっと読む)

画像読取装置

【課題】所定の作業場所で読取手段の着脱作業を行う際に、作業者が作業場所へ重量物を持ち運ばなくても済み、作業時に必要となるスペースも低減でき、作業場所へ異物を持ち込む危険性も低減可能な画像読取装置を提供すること。

【解決手段】第二イメージセンサが組み込まれた第二支持体52は、ADFベース50及び第一支持体51側から分離可能な構造になっている。また、第二支持体52は、FFC54を介してADFベース50及び第一支持体51に繋がれた状態になっているが、蓋55を取り外せば、第二イメージセンサとFFC54との接続部分が露出するので、その接続を解除する作業や再接続する作業を容易に実施することができる。第二イメージセンサとFFC54との接続を解除すれば、第二イメージセンサが組み込まれた第二支持体52だけをクリーンブース内へ持ち込むことができる。

(もっと読む)

画像読取装置

【課題】原稿の画像データの乱れを抑制できる画像読取装置を提供する。

【解決手段】画像読取装置10は、開閉部11側の読取部24の出力信号を本体部20側の制御基板201に伝達するフレキシブルフラットケーブル7Aと、本体部側読取部25の出力信号を制御基板201に伝達する本体部側フレキシブルフラットケーブル7Bとが、本体部20の内部において、双方の厚さ方向に重なった状態で配線される重複区間L1〜L2を備える。本体部20には、重複区間L1〜L2においてフレキシブルフラットケーブル7Aと本体部側フレキシブルフラットケーブル7Bとの接触を防止する接触防止機構111、112、121、122が設けられている。

(もっと読む)

画像読取装置

【課題】原稿の画像データの乱れを抑制できる画像読取装置を提供する。

【解決手段】画像読取装置10は、開閉部11側の読取部24と本体部20側の処理部201とを電気的に接続するフレキシブルフラットケーブル7Aと、本体部20側に設けられ、フレキシブルフラットケーブル7Aが開閉部11の回動又は昇降に追従するように、フレキシブルフラットケーブル7Aを案内するガイド部300と、を備える。ガイド部300は、フレキシブルフラットケーブル7Aの所定箇所を位置固定するとともに、その位置固定された箇所と、開閉部11との間において、フレキシブルフラットケーブル7Aを、開閉部11の回動軸R1方向から見て略U字状に撓ませた状態で保持するためのリブ301を有する。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】発光サイリスタを駆動するための駆動回路の発振等を防止する。

【解決手段】オン/オフ指令信号DRVON−Nが“L”レベルの場合、CMOSインバータ42の出力側のデータ端子DAが“H”レベルとなる。この結果、プリントヘッド13側の共通端子INも“H”レベルとなり、各発光サイリスタ210のアノード・カソード間に電源電圧VDDが印加される。この際、発光サイリスタ210−1〜210−nの内、発光指令されている発光サイリスタ210のゲートのみを、シフトレジスタ110によって選択的に“L”レベルとすることで、発光指令されているサイリスタ210がターンオンする。PMOS43のソースにVDD電源が接続され、サブストレート端子に、VDD電源よりも高いVDD5電源が接続されているので、PMOS43の閾値電圧が増加し、駆動回路41の発振を防止できる。

(もっと読む)

露光装置、露光装置の駆動方法、プリントヘッドおよび画像形成装置

【課題】主走査方向においてドットのピッチより小さい距離でドットの位置を補正する。

【解決手段】発光チップC1(C)は、基板80上に列状に配列された発光サイリスタL1、L2、L3、…と、転送サイリスタT1、T2、T3、…と、記憶サイリスタM1、M2、M3、…とを備えている。奇数番目の転送サイリスタT1、T3、…のカソード端子は第1転送信号線72に接続され、偶数番目の転送サイリスタT2、T4、…のカソード端子は第2転送信号線73に接続され、奇数番目の記憶サイリスタM1、M3、…のカソード端子は第1書込信号線74aに接続され、偶数番目の記憶サイリスタM2、M4、…のカソード端子は第2書込信号線74bに接続されている。二つの発光サイリスタLを組にして1ドットに対応させる。

(もっと読む)

光プリントヘッドおよびそれを用いた画像形成装置

【課題】各発光素子による露光を所望の露光量で行うことができる光プリントヘッドを提供する。

【解決手段】基板と、該基板上に列状に配列された複数の発光素子からなる発光素子アレイと、基板上に設けられた発光素子アレイを駆動する駆動回路部とを有する光プリントヘッドである。駆動回路部は、複数の発光素子に対応して列状に配列された複数の駆動素子と、該複数の駆動素子の一端子に電位を供給する電位供給回路と、複数の前記一端子と電位供給回路の出力端子とを接続する信号配線とを有し、信号配線は、電位供給回路の出力端子に接続される共通信号配線と、該共通信号配線から分岐するように、各駆動素子に向かって延在する複数の個別信号配線とを有する。

(もっと読む)

発光装置、駆動回路及び電子機器

【課題】発光素子を駆動する駆動信号の点灯レベルを高い精度で補正する。

【解決手段】1レベル電圧V1が供給される第1端子T1と、1022レベル電圧V1022が供給される第2端子T2との間に抵抗群130を介挿して分圧を行い、低電位側の第3端子T3aに供給される0レベル電圧V0と、高電位側の第3端子T3bに供給される1023レベル電圧V1023を、1レベル電圧V1〜1022レベル電圧V1022から独立した電圧値にする。例えば、発光素子を駆動する駆動トランジスターがpチャネル型の場合は、駆動信号Xiの消灯レベルに対応する1023レベル電圧V1023以外の1レベル電圧V1〜1022レベル電圧V1022を、発光素子を目標輝度で発光させるために駆動信号Xiの点灯レベルを補正する必要がある範囲に集中的に割り当てる。

(もっと読む)

露光ヘッド、画像形成装置

【課題】遮光部材とボンディングワイヤとの接触を回避し、ゴーストを効率的に抑制する遮光部の配置を可能とする技術を提供する。

【解決手段】配線層を備えた基板と、配線層とボンディングワイヤを介して電気的に接続された第1の発光素子を有し基板に配設された第1の発光チップ、第1の発光素子から発光された光が通過する第1の孔を有する遮光部と、第1の発光素子から発光され第1の孔を通過した光を結像する第1の結像光学系と、を備え、次の関係、x1<Dap/2、L1>L2、x1:第1の結像光学系の光軸から第1の発光素子までの距離、Dap:第1の孔の寸法、L1:ボンディングワイヤが基板から最も離れる位置の基板からの距離、L2:遮光部と基板との距離、を有するように形成されている。

(もっと読む)

発光素子アレイ、光プリントヘッドおよび画像形成装置

【課題】 光プリントヘッド中の発光素子アレイ同士の間において生じる光量のずれを抑制できる発光素子アレイ、光プリントヘッドおよび画像形成装置を提供する。

【解決手段】 基板と、複数の発光素子と、複数の共通電極パッドと、複数の電極パッドと、を具備する発光素子アレイであって、前記複数の電極パッドは、

前記基板の長手方向における幅がそれぞれ等しい第1の電極パッドと、

前記第2の列の端に設けられ、前記基板の長手方向における幅が前記第1の電極パッドの幅よりも小さい第2の電極パッドと、を有する。

(もっと読む)

電気配線基板および光プリントヘッド

【課題】 ボンディングワイヤとボンディングパッドとの接着力の強い電気配線基板を提供する。

【解決手段】 第1の基板と、前記第1の基板上面に設けられた接着層と、前記接着層と下面とが接着され、上面に電極パッドを有する第2の基板と、を具備する電気配線基板であって、前記第1の基板上面または前記第2の基板下面に複数の凹凸が設けられ、前記凹凸の凸部の上方に前記電極パッドが位置する。

(もっと読む)

発光装置、プリントヘッド及び画像形成装置

【課題】光量ばらつきに起因する画層品質低下を抑制する発光装置、プリントヘッド及び画像形成装置を提供する。

【解決手段】複数の発光素子(発光サイリスタ)Lを複数の組(ブロック)#I、#II・・に分割し、組毎に一括して点灯制御する。組を構成する全ての素子を同時点灯すると、電流密度の高低により光量ばらつきが生じる。組の中央の発光サイリスタと端部の発光サイリスタを異なる給電線216a、216bで給電することで、光量ばらつきを低減する。

(もっと読む)

露光ヘッド、画像形成装置

【課題】発光素子を十分な光量で発光させて、良好な露光を実現可能とする技術を提供する。

【解決手段】第1の方向に第1のピッチで配設された発光素子と、発光素子に対して第1の方向に直交もしくは略直交する第2の方向の一方側で、第1のピッチより広い第2のピッチで第1の方向に配設されて、発光素子を発光させる駆動回路と、を備える。

(もっと読む)

露光ヘッド、画像形成装置

【課題】制御回路が実装されたFPCを発光素子が配設されたヘッド基板に接続した構成において、FPCとヘッド基板との接続部分の破損を抑制する。

【解決手段】発光素子が配設されたヘッド基板と、ヘッド基板を支持する支持部材と、ヘッド基板に接続されたフレキシブルプリント基板と、フレキシブルプリント基板に配設されて、発光素子の発光を制御する制御回路と、フレキシブルプリント基板を支持部材に固定する固定部材と、を備える。

(もっと読む)

光プリントヘッドおよび画像形成装置

【課題】パワーMOSトランジスタの搭載を不要とし、光プリントヘッドの小型化、低コスト化を図る発光素子アレイ、駆動装置、画像形成装置を提供する。

【解決手段】本発明の光プリントヘッドは、第1端子と、第2端子と、前記第1端子と前記第2端子との間の導通を制御するための制御端子とを各々有し、前記第1端子と前記第2端子との間に電流が流れることにより発光する複数の発光素子と、前記複数の発光素子の各々に対応して設けられ、前記発光素子の前記第1端子と前記第2端子との間に電流を流すことにより発光させる駆動回路と、前記複数の発光素子の各々に対応して設けられ、前記発光素子の前記制御端子と一端が接続され、双方向に電圧降下を発生させる双方向電圧降下発生回路と、複数の前記双方向電圧降下発生回路の他端を共通に接続する共通母線と、前記共通母線に対して、前記発光素子の制御端子に与える制御信号を出力するバッファ回路とを備えたことを特徴とするものである。

(もっと読む)

発光素子アレイ及びこれを用いた画像形成装置

【課題】発光素子間の発光光量のばらつきを低減することが可能な発光素子アレイ及びこれを用いた画像形成装置を提供する。

【解決手段】半導体基板と、前記半導体基板上に予め定められた間隔で設けられる複数の発光素子と、前記半導体基板上に前記発光素子に対応して複数設けられ、前記複数の発光素子の点滅を切り替える切替素子と、前記切替素子を第1の状態と第2の状態との間で切り替える切替用の信号線と、前記半導体基板上に前記切替用の信号線と層を異ならせて当該切替用の信号線よりも広い幅で設けられ、前記複数の発光素子に通電して発光させるための発光用信号線とを備えるように構成する。

(もっと読む)

ラインヘッド、画像形成装置及びラインヘッドの組み立て方法

【課題】レンズと発光素子との位置決めを行うためのアライメントマークの位置が、発光素子から離れることにより、レンズの位置決めが不正確になる恐れがある。

【解決手段】光を発光する発光素子74が複数配設された発光素子基板87と、発光素子基板87に配設された複数の発光素子74から発光された光を結像させる結像光学系と、発光素子基板87の複数の発光素子74が配設された発光素子配設領域71Aに形成されたアライメントマークAMと、を有する。

(もっと読む)

データ通信システムおよび液滴ジェット塗布装置

【課題】配線部材を削減して、コストを低減するとともにシステムの小型化を実現するデータ通信システムおよび当該データ通信システムを搭載した液滴ジェット塗布装置を提供する。

【解決手段】制御基板CB1〜CBnは、上位層デバイスからの制御を受ける下位層デバイスであるFPGA1〜FPGAmを搭載しており、下位層デバイスの1つのグループで構成され、何れも同じ構成を有している。制御基板CBは、シリーズに接続されたFPGA1〜FPGAmと、シリーズの先頭段に相当するFPGA1に各制御基板CBに固有のグループアドレスを設定するスイッチ手段SWとを有している。

(もっと読む)

画像読取装置

【課題】

画像読取装置の最大消費電流を抑え、高画質な画像読取装置を提供する。

【解決手段】

画像読取装置(100)は、列状に並べられた複数センサICチップ(122a〜122l)を備え、それらは2以上のブロックに区切られている。各センサICチップ(122a〜122l)には共通のクロックパルス信号(CLK)が入力され、各ブロック毎にアナログ出力信号(A1〜A6)が個別に出力される。スタートパルス信号(SP1〜SP6)は各ブロック毎に個別に入力され、スタートパルス信号(SP1〜SP6)は同じブロック内のセンサICチップに共通に入力される。スタートパルス信号(SP1)に対しスタートパルス信号(SP2)は遅れ入力される。以下同様の条件で各スタートパルス信号(SP2〜SP6)の間で遅れたスタートパルス信号が入力される。

(もっと読む)

61 - 80 / 315

[ Back to top ]