Fターム[5E034DC01]の内容

サーミスタ、バリスタ (5,260) | 電極端子(PTC、NTC、バリスタ) (667) | チップ型 (303)

Fターム[5E034DC01]に分類される特許

61 - 80 / 303

酸素遮蔽で包んだ表面実装部品

表面実装部品(100)の製造方法は、B段階の上層(300)と下層(315)と、開口部を有するC段階の中間層(310)とを含む複数の層を準備する工程を含む。コア部品(305)は、開口部に挿入され、それから、上層および下層は、それぞれ中間層の上下に配置される。これらの層はC段階になるまで硬化される。コア部品は、約0.4cm3・mm/m2・atm・dayよりも小さい酸素透過率を有する酸素遮蔽材料により実質的に囲まれる。  (もっと読む)

(もっと読む)

電子部品およびその製造方法

【課題】寸法精度、形状精度が高く、また緻密でボイド等がなく、かつ形成も容易な端子電極を備える電子部品およびその製造方法を提供する。

【解決手段】端子電極を形成すべき端面16a、16bを有する素子本体16を、該素子本体16が端面16a、16bに略垂直な方向に嵌入される保持孔42が複数個設けられた保持板40の各保持孔42に、素子本体16の端面16a、16bと保持板40の板面40a、40bが略面一になるように保持させるとともに、素子本体16の端面16a、16bに導電性接着シート26を積層して一体に接着させ、次いで、保持板40の各保持孔42の周縁部に沿って導電性接着シート26を切断し、各端面16a、16bに端子電極18を形成する。

(もっと読む)

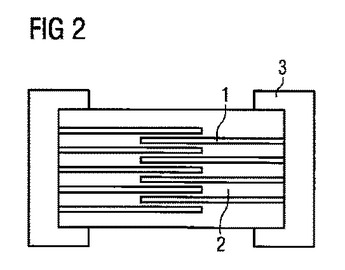

負の温度係数を有する電気デバイス

【課題】B値と抵抗値とを広い範囲にわたり変えることができるエレクトロセラミックTNCデバイスの提供

【解決手段】なる材料からなるそれぞれ少なくとも1つの第1の空間的に形成されたセラミック部分領域と少なくとも1つの第2の空間的に形成されたセラミック部分領域とを有する基体を有し、第1のセラミック部分領域の材料と第2のセラミック部分領域の材料とはそれぞれ負の温度係数を有する抵抗を有し、少なくとも1つの第1のコンタクト層と第2のコンタクト層とが基体の表面上に設けられていて、2つのセラミック部分領域は第1のコンタクト層と第2のコンタクト層との間に配置されていて、かつ基体中に間隔を置いて配置された複数の導電性電極層が存在し、この導電性電極層はそれぞれコンタクト層の一方と導電性に接続していて、2つの電極積層体を形成し、前記の電極積層体はそれぞれ一方のコンタクト層と接触している電気デバイス。

(もっと読む)

複合積層チップ素子

【課題】ノイズの除去、挿入損失などの周波数特性が向上した積層チップ素子を提供する。

【解決手段】積層チップ素子は、両対向端部の方向にそれぞれ離れた第1及び第2の導電体パターンが、各単位素子ごとにそれぞれ配置されるように連続的に複数形成された少なくとも1枚の第1のシートと、両対向端部の方向と交差する方向に第3の導電体パターンが複数の単位素子を跨いで形成された少なくとも1枚の第2のシートと、第1及び第2のシートの上に各単位素子ごとにそれぞれ形成された複数の抵抗体パターンと、を含み、第1のシート及び第2のシートは交互に積層され、第1の導電体パターンと第3の導電体パターンとが重なり合う領域の面積、及び第2の導電体パターンと第3の導電体パターンとが重なり合う領域の面積がそれぞれ異なる。

(もっと読む)

リニアサーミスタ

【課題】 リニアサーミスタにおいて、熱結合端子が高電圧回路に接合されていても高電圧回路と温度検出回路との高い絶縁性を確保すること。

【解決手段】 サーミスタ素子部1と該サーミスタ素子部1に接続された第1の抵抗2及び第2の抵抗3とが設けられた複合サーミスタチップ11と、該複合サーミスタチップ11に電気的に接続されたグランド端子GND、電源端子VCC、出力端子OUT、複合サーミスタチップ11に電気的に絶縁されている熱結合端子5を有したリードフレーム6と、複合サーミスタチップ11を封止した直方体形状の樹脂封止部7と、を備え、樹脂封止部7の一つの側面に、グランド端子GNDと電源端子VCCと出力端子OUTとが配されていると共に、この側面の反対側の側面に熱結合端子5が配されている。

(もっと読む)

電圧非直線抵抗体、電圧非直線抵抗体を搭載した避雷器及び電圧非直線抵抗体の製造方法

【課題】優れた電圧非直線性を有する電圧非直線抵抗体を低不良率で提供すること。

【解決手段】酸化亜鉛粒子と、亜鉛及びアンチモンを主成分とするスピネル粒子と、酸化ビスマス相とから主として構成される焼結体からなり、酸化ビスマス相中にカリウム及びナトリウムからなる群から選択される少なくとも1種のアルカリ金属が存在し且つ焼結体における正方晶Bi16CrO27の(123)面のX線回折ピーク強度(A)に対する立方晶Bi38CrO60の(321)面のX線回折ピーク強度(B)の比(B/A)が0以上0.24未満の範囲であることを特徴とする電圧非直線抵抗体である。

(もっと読む)

電気的多層コンポーネント

本発明は、少なくとも2個の外部電極(2,2´)を有する基体(1)を備える電気的多層コンポーネントに関する。電気的多層コンポーネントは、それぞれ1個の外部電極(2,2)に接続した、少なくとも第1および第2内部電極(3,4)を備える。本発明による電気的多層コンポーネントは、少なくとも第1内部電極(3)を包囲する、少なくとも1つのセラミックバリスタ層(5)を備える。本発明の電気的多層コンポーネントは、少なくとも1つの誘電体層(6)を備え、誘電体層(6)を、少なくとも1つのバリスタ層(5)と第2内部電極(4)との間に配置する。誘電体層(6)は、ガス状の媒体を充填する少なくとも1つの開口(8)を有する。 (もっと読む)

バリスタセラミック、バリスタセラミックを含む多層構成要素、バリスタセラミックの製造方法

本発明は、以下の材料:Znを主成分として、Prを0.1〜3原子%の割合で、Y,Ho,Er,Yb,Luから選択される金属Mを0.1〜5原子%の割合で含む、バリスタセラミックに関する。  (もっと読む)

(もっと読む)

電気的多層コンポーネント

電気的多層コンポーネントは、外部接点(2, 2´)および内部電極(3, 4)を設けた基体1、第1内部電極3を設けたセラミックバリスタ層5、ならびにバリスタ層5に隣接する誘電体層6を有する。誘電体層6には、少なくとも1つの開口8を設け、半導体材料または金属材料で充填する。 (もっと読む)

バリスタセラミック、バリスタセラミックを含む多層構成要素、バリスタセラミックの製造方法

本発明は、Znを主成分として、Prを0.1〜3原子%の割合で含む、バリスタセラミックに関する。  (もっと読む)

(もっと読む)

静電気対策素子

【課題】静電容量が小さく、且つ、放電特性に優れるのみならず、耐熱性及び耐候性が高められた、静電気対策素子等を提供すること。

【解決手段】絶縁性基板11上において相互に離間して対向配置された電極21,22の間に、絶縁性無機材料32のマトリックス中に導電性無機材料33が不連続に分散したコンポジットである機能層31を配設する。

(もっと読む)

リード線付き電子部品の製造方法

【課題】大規模な装置や複雑な方法を要することなく、リード線の先端部分の加工と金属線からの被覆除去を効率よく行うことができ、かつ電子部品がダメージを受けることもなく、接合強度や電気接続の信頼性を確保できるリード線付き電子部品を短時間で効率良く製造できるようにする。

【解決手段】第2のリード線6bを所定長さに切断すると同時に、第1のリード線6aの先端部両側面20、21及び第2のリード線6bの先端部外側面22の絶縁部材8a、8bを除去する。先端部を加圧して平坦状に形成すると共に、絶縁部材8bが除去された終端部分に対応する箇所に切込みを入れる。第1及び第2のリード線6a、6bの各先端部をはんだ槽に浸漬し、先端部の絶縁部材8a、8bを溶融除去すると共に、第1及び第2の金属線露出部にはんだを塗布した後、第1及び第2の金属線露出部とサーミスタとを加圧・加熱して接合する。

(もっと読む)

セラミック電子部品

【課題】導通不良の発生時期を遅らせることにより、長寿命化を図ることができるセラミック電子部品を提供すること。

【解決手段】積層チップバリスタ1では、外部電極51が、第2の内部電極33の引出部分33aが接続される第1の領域61を含む第1の面53と実装用の半田電極57が接続される第2の領域62を含む第2の面55とを有し、第1の領域61は、第1及び第2の面53,55に垂直な方向からみて、第2の領域62の輪郭の一部を跨ぐように位置する。このため、半田電極57の形成位置に対応してバリスタ素体11にクラックが発生するような場合であっても、内部電極33の引出部分33aにより、第1の領域61がクラック発生の起点となることが回避され、内部電極33から半田電極57に至る導通経路が維持される。

(もっと読む)

過電圧保護部品およびその製造方法

【課題】本発明は、ショート不良が発生しにくく、かつ初期抑制ピーク電圧も低く、さらには静電気等の過電圧の繰り返し印加に対する耐久性にも優れている過電圧保護部品を提供することを目的とするものである。

【解決手段】本発明の過電圧保護部品は、絶縁基板11の上面に形成され、かつギャップ15を隔てて対向する一対の下部電極13,14と、前記ギャップ15を覆うように形成された過電圧保護材料層とを備え、前記過電圧保護材料層をギャップ15を覆う第1の過電圧保護材料層16と、この第1の過電圧保護材料層16上に重なるように形成された第2の過電圧保護材料層17とにより構成し、かつ前記第1の過電圧保護材料層16に含まれる導電性粒子の濃度を第2の過電圧保護材料層17に含まれる導電性粒子の濃度よりも高くしたものである。

(もっと読む)

積層型セラミック電子部品

【課題】ESDに対する耐性が高く、しかも容易にショートしない積層型セラミック電子部品を提供する。

【解決手段】半導体セラミック層10と内部電極12a〜12c,14a〜14cとが交互に積層された素子本体4と、前記素子本体の端部に形成された複数の端子電極6と、を有する積層型セラミック電子部品2であって、前記端子電極6と、該端子電極の極性と異なる極性を有し、最外に配置された内部電極14aと、の最短距離をd(d1)とし、極性の異なる内部電極間の最短距離をt(t1)とすると、前記dおよびtが、d/t≦0.96である関係を満足する。

(もっと読む)

多層式電気部品及び多層式電気部品を備えた回路

【解決手段】多層式電気部品は、交互に積層された複数のセラミック層(2)と複数の電極層(3)とを有する単一の基体(1)を備える。基体(1)は、互いに対向する2つの端面(4,4’)と、互いに対向する2つの側面(5,5’)とを備える。多層式電気部品は、複数の外部電極(6,6’)と、電極層(3)に配置された複数の内部電極(7,8,9)とを備え、複数の内部電極(7,8,9)が、少なくとも部分的に重なり合って重複領域を形成している。内部電極(7,8,9)のそれぞれは、外部電極(6,6’)に割り振られている。端面(4,4’)の一方から延びる少なくとも1つの第1内部電極(7)は、端面(4,4’)の他方から延びる少なくとも1つの第2内部電極(8)と重なっている。側面(5,5’)の1つから延びる少なくとも1つの第3内部電極(9)が第1内部電極(7)及び第2内部電極(8)に重なっている。 (もっと読む)

チップ抵抗器

【課題】抵抗体の抵抗値をリニア正温度係数チップ抵抗器の特性を損なうことなく高くすることができるとともに、抵抗体のESD特性を向上させることができ、従来からリニア正温度係数チップ抵抗器の抵抗体に使用される抵抗体ペーストを変えることなく上記の各作用効果を得ることができるリニア正温度係数チップ抵抗器を提供する。

【解決手段】抵抗体30は、電極間方向と直角の方向に形成された4つの帯状部32a、32b、32c、32dと、隣接する帯状部間に設けられ隣接する帯状部間を接続する帯状部接続部36a、36b、36cとを有して、全体に蛇行状に形成され、帯状部接続部36bの幅S1が帯状部接続部36aの幅S2及び帯状部接続部36cの幅S3よりも大きく形成されている。なお、帯状部の数は4つ以上で、ターン部分が3つ以上であればよい。

(もっと読む)

複合電子部品及びその製造方法

【課題】静電容量が小さく且つ放電特性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品を提供する。

【解決手段】複合電子部品100は、第1及び第2の磁性基体11a、11bに挟まれたコモンモードフィルタ層12a及び静電気対策素子層12bによって構成されている。コモンモードフィルタ層12aは互いに磁気結合されたスパイラル導体17,18を備えている。静電気対策素子層12bは、下地絶縁層27の表面に形成されたギャップ電極28,29と、ギャップ電極28,29を覆う静電気吸収層30とを備えている。ギャップ電極28,29は、磁性基体11aの表面に下地絶縁層27を介して形成されている。静電気吸収層30は低電圧放電タイプの静電気保護材料として機能し、静電気などの過電圧が印加された際に、この静電気吸収層30を介して電極間で初期放電が確保される。

(もっと読む)

複合電子部品

【課題】静電容量が小さく且つ放電特性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品を提供する。

【解決手段】複合電子部品100は、第1及び第2の磁性基体11a、11bに挟まれたコモンモードフィルタ層12a及び静電気対策素子層12bによって構成されている。コモンモードフィルタ層12aは互いに磁気結合されたスパイラル導体17,18を備えている。静電気対策素子層12bは、下地絶縁層27の表面に形成されたギャップ電極28,29と、ギャップ電極を覆う静電気吸収層30とを備えている。ギャップ電極28,29のギャップはインダクタンス素子の導体パターンと重ならない位置に配置されている。静電気吸収層30は低電圧放電タイプの静電気保護材料として機能し、静電気などの過電圧が印加された際に、この静電気吸収層30を介して電極間で初期放電が確保される。

(もっと読む)

電流−電圧非直線抵抗体およびその製造方法

【課題】エネルギ耐量に優れた電流−電圧非直線抵抗体を提供することを目的とする。

【解決手段】電流−電圧非直線抵抗体10は、酸化亜鉛を主成分とし、副成分として少なくともビスマス(Bi)、アンチモン(Sb)を含んだ混合物の焼結体20を備える。また、電流−電圧非直線抵抗体10における焼結体20は、焼結体20の微細構造を主に構成する通電成分である酸化亜鉛粒子の粒子間の最大離隔距離Dと酸化亜鉛粒子の平均粒径Zとの比(D/Z)が0.5未満となるように構成されている。

(もっと読む)

61 - 80 / 303

[ Back to top ]