Fターム[5E336CC32]の内容

プリント板への電気部品等の実装構造 (16,219) | 電気部品等の構造 (4,114) | リードレス部品 (1,350) | 電極構造が特定されたもの (599)

Fターム[5E336CC32]の下位に属するFターム

電極の一部の構造が異なるもの (24)

電極数が4個以上のもの (193)

Fターム[5E336CC32]に分類される特許

1 - 20 / 382

半導体装置の製造方法、半導体装置、及び半導体素子

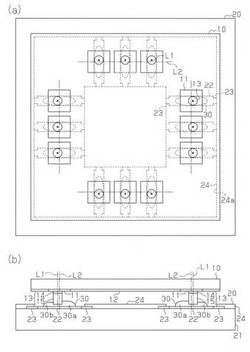

【課題】はんだによる短絡不良を低減すること。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。各々の電極端子13の中心軸L1は、電極パッド11の中心から、電極パッド11の配列方向と直交する方向に沿って半導体素子10の外側にずれた位置に形成されている。半導体素子10が実装される配線基板20には、半導体素子10の電極パッド11と対応する複数の接続パッド22が形成されている。各接続パッド22の中心L2は、半導体素子10の電極パッド11の中心と略一致する。また、各接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

(もっと読む)

ノイズ対策電子部品の回路基板への実装構造

【課題】 実装箇所に応じたノイズ対策電子部品を複数用意する必要が無くなり、ノイズ対策の検討を容易迅速に行うことが可能なノイズ対策電子部品の実装構造を提供する。

【解決手段】 インダクタ1の実装する部品側面を底面にして第1の接続状態にすることで、第2のコイル4の他端の引出電極4f1が第3の外部電極3cおよび短絡用配線パターン13aを介して他方の外部電極3bに接続される。このため、コイル4,5は、各一端が一方の外部電極3aに共通接続され、各他端が他方の外部電極3bに共通接続されて、並列接続される。従って、インダクタ1の抵抗成分は小さくなる。一方、インダクタ1の実装する部品側面を異ならせて天面にし、第2の接続状態にすることで、第3の外部電極3cは電気的に浮き、第2のコイル4の他端も浮いた状態になる。このため、インダクタ1のインピーダンスは第1のコイル5が有するものとなって高くなる。

(もっと読む)

プリント配線板

【課題】表面実装部品の電極とプリント配線板上の電極パッドとの間の接続特性の劣化を招くことなく、極性を有する表面実装部品の搭載方向を判別できるようにする。

【解決手段】極性を有する表面実装部品101が実装されるプリント配線板1は、互いに間隔をあけて配置され、部品101の1対の電極がそれぞれ電気的に接続される1対の電極パッド13,14と、1対の電極パッド13,14をそれぞれ部分的に露出させる開口12a,12bを有するカバー層12と、を備える。一方の電極パッド13におけるカバー層12により覆われた部分13bの形状が、他方の電極パッド14におけるカバー層12により覆われた部分14bの形状と異なる。

(もっと読む)

ダウンホール装置のためのマルチチップモジュール

【課題】ダウンホールモジュールで使用する接続信頼性の良好な電子アセンブリを提供する。

【解決手段】電子アセンブリ200は、多層セラミックアセンブリと、多層セラミックアセンブリ上に配置される電子部品240とを有し、多層セラミックアセンブリは、セラミック基板220と、セラミック基板220上に配置されるニッケルめっき層と、ニッケルめっき層上に配置される0.5ミクロン未満の厚さを有する金めっき層と、を含み、電子部品240と金めっき層とは、アルミニウムワイヤでワイヤボンドされる。

(もっと読む)

プリント回路基板及びその製造方法

【課題】ファインピッチ及び半田ボールの高さを、従来より高く形成することができるとともに、設計自由度が向上するプリント回路基板及びその製造方法を提供する。

【解決手段】本発明のプリント回路基板100は、接続パッド120を有するベース基板110と、接続パッド120上に第1開口部を有する半田レジスト層130と、前記第1開口部に形成される半田ボール160と、を含み、半田ボール160が雪だるま状であるものである。

(もっと読む)

実装構造

【課題】回路設計において高い自由度を得つつ、鳴きを低減することができる実装構造を提供することである。

【解決手段】電子部品10が回路基板50上に実装されている実装構造1。ランド54a,54bは、基板本体52上に設けられ、外部電極12a,12bのそれぞれとはんだ60a,60bにより接続されている。ランド電極54a,54bからはんだ60a,60bの頂上までの高さH1は、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2の1.27倍以下である。

(もっと読む)

電子機器の製造方法

【課題】半田付けによる回路基板への電子部品の実装において、半田付けの信頼性を高めると共に実装スペースを縮小する。

【解決手段】ランド11を有する回路基板3と、前記ランドに電気的に接続される板状のリード端子10を有する電子部品2と、を備え、前記リード端子が前記ランドにレーザー半田付けされてなる電子機器1の製造方法であって、前記ランドに前記リード端子を立設し、前記リード端子の一部に設けられる露出した照射面にレーザー光線を照射して、前記ランドに設けられたクリーム半田13を溶融する。

(もっと読む)

電子機器、電子部品、および基板アセンブリの製造方法

【課題】電子部品を回路基板により精度良く実装することが可能な電子機器、電子部品、および基板アセンブリの製造方法を得る。

【解決手段】実施形態にかかる電子機器では、接合部は、第一導体部と第二導体部との間に介在し、第一導体部と第二導体部とを電気的に接続した。封止部は、少なくとも第一面と第二面との間に介在し、酸化膜を還元する還元剤を含み、接合部を封止した。位置決め部は、第一面から突出し、その突出側の端部が第一面と第二面との間に位置され、第二面に封止部が塗布された電子部品が第一面に載せられる際に当該第一面に沿って移動しようとした場合にあっても封止部と接触することにより電子部品が第一導体部と第二導体部とが対向した位置から外れるのを抑制する。

(もっと読む)

はんだボールおよびはんだボールを用いた半導体装置

【課題】

銅パッド部とはんだボールとの間における銅と錫との反応が促進されるのを阻止して、銅パッド部に断線が発生するのを防止することを可能にするはんだボール及びそのはんだボールを用いた半導体装置を提供する

【解決手段】

はんだボールを、金属又は樹脂の表面に金属をコーティングしたコア材と、このコア材の表面に形成されたニッケル、チタンもしくクロムを主成分とする第一の金属膜層と、この第一の金属膜層の外周に形成された銅を主成分とする第二の金属膜層と、この第二の金属膜層の外周に錫を主成分とする第三の金属膜層とを有して構成し、半導体装置を、第一の部材上の第一の電極パッドと第二の部材上の第二の電極パッドとをこのはんだボールを用いて接合した構成とした。

(もっと読む)

電子部品

【課題】応力緩和機能を備える新規な構造の電子部品を提供する。

【解決手段】接続電極Eと、下側に空間が設けられた状態で接続電極Eに接続され、本体部40a(膨出部)と、本体部40aの上面に設けられた突出接続部40bとを備え、圧力によって弾性変形する可撓性電極端子40とを含む。可撓性電極端子40は、実装基板、インターポーザ、半導体チップ又はプローブ基板などの外部接続端子として設けられる。

(もっと読む)

基板実装構造

【課題】基板の両面に電子部品を実装するものにあって、一方側の電子部品が他方側の電子部品の実装位置を制限せず、しかも、良好なハンダ付けができる基板実装構造を提供する。

【解決手段】基板1の上面1a及び下面1bにハンダ付けで表面実装コネクタ10及びチップ部品20がそれぞれ実装される基板実装構造であって、基板1の上面1aには、下面1bに達しない深さのピン挿入溝2が設けられ、基板1の上面1aに実装される表面実装コネクタ10は、コネクタハウジング11とリードピン12を有し、リードピン12の先端がコネクタハウジング11の実装面11aより下方位置に位置され、リードピン12の先端がピン挿入溝2に挿入された状態でハンダ付けされた。

(もっと読む)

パッケージ基板及びその製造方法

【課題】本発明はパッケージ基板及びその製造方法に関する。

【解決手段】本発明のパッケージ基板は、少なくとも一つの導電性パッドを具備した基板と、前記基板上に形成され、前記導電性パッドを露出させる開口部を有する絶縁層と、前記開口部を介して露出された導電性パッドの上面及び前記絶縁層の側壁に沿って形成される剥離防止層と、少なくとも一つの合金材料からなって前記剥離防止層上に形成されるメタルポストと、前記メタルポスト上に形成される熱拡散防止膜と、を含む。

(もっと読む)

電子部品の実装構造体

【課題】配線基板に実装されたチップ部品の、耐熱応力性と耐振動性と放熱性との向上を図った、信頼性に優れるとともに高温環境でも使用可能な、電子部品の実装構造体を得ることである。

【解決手段】回路基板の回路パターンに実装されたチップ部品と、チップ部品の両端に設けられた電極と、電子部品に配設された伝熱材と、伝熱材に接触するとともに、回路パターンと平行に固定された覆体とを備え、電極が回路接合部と立脚部とを有し、電子部品の設置高さと伝熱材の厚みとの合計が、覆体を固定する前より、固定後の方が薄くなっている電子部品の実装構造体。

(もっと読む)

部品実装基板

【課題】基板表面に露出した端子パッドを介して電子部品が実装されてなる配線基板において、基板表面と電子部品との間に、ボイドを生じることなく十分な量の封止樹脂を注入及び充填させる。

【解決手段】配線基板の表面に、一対の端子パッドを構成する前記端子パッドが配列する第1配列方向と交差する交差方向に延びるとともに、中央部から端部に向けて前記第1配列方向の幅が狭小化された溝部を形成し、前記溝部の中央部は、前記部品の前記交差方向における中央と対応する位置に形成して、部品実装基板配線を構成する。

(もっと読む)

電子機器、電子部品、および基板アセンブリの製造方法

【課題】電子部品を回路基板により精度良く実装することが可能な電子機器、電子部品、および基板アセンブリの製造方法を得る。

【解決手段】実施形態にかかる電子機器は、筐体と、回路基板と、電子部品と、接合部と、封止部と、位置決め部と、を備える。回路基板は、筐体に設けられ、第一面と、この第一面に設けられた第一導体部と、を有する。電子部品は、回路基板の第一面上に位置され、第一面と対向した第二面と、この第二面に設けられた第二導体部と、を有する。接合部は、 第一導体部と第二導体部との間に介在し、第一導体部と第二導体部とを電気的に接続する。封止部は、少なくとも第一面と第二面との間に介在し、酸化膜を還元する還元剤を含み、接合部を封止する。位置決め部は、回路基板と電子部品とを位置決めする。

(もっと読む)

電子装置及びフレキシブル基板

【課題】電子装置の筐体内に実装する部品の実装密度や実装効率を高める。

【解決手段】筐体(4)に空間部(39)と、回路ユニット(フレキ基板38)を備える。この筐体は、表示部(30)を搭載する。空間部は、筐体内の端部側と表示部との間に形成されている。回路ユニットは、アンテナパターン(62)が形成されるとともにマイクロフォン(44)が実装され、表面側又は背面側のいずれか一方又は双方に1又は複数の実装部品(LED42等)が実装され、空間部に配置している。

(もっと読む)

電子部品及びその製造方法と、配線基板

【課題】θズレの許容範囲を広げることを可能とした電子部品及びその製造方法と、配線基板を提供する。

【解決手段】基板の第1の面に位置する第1のランドと、第1の面に位置し、第1の方向において第1のランドと離れた状態で隣り合う第2のランドと、第1の電極と第2の電極とを有し、第1の電極が第1のランドに接続されると共に、第2の電極が第2のランドに接続される素子と、を備え、第1のランドは第2のランドと向かい合う第1の辺を有し、第2のランドは第1のランドと向かい合う第2の辺を有し、第1の辺は第1の中央部と第1の端とを含み、第2の辺は第2の中央部と第2の端とを含み、第1の方向において、第1の中央部と第2の中央部とが向かい合いと共に、第1の端と第2の端とが向かい合い、第1の端と第2の端との間の第1の距離は、第1の中央部と第2の中央部との間の第2の距離よりも長い。

(もっと読む)

実装基板

【課題】ランド部に塗布されるクリーム半田の量を調整しなくても、プリント基板に対する電子部品の曲がり、ズレ、浮き等を抑制できる実装基板を提供すること。

【解決手段】発光素子基板12の長手方向の両端に設けられた電極30をプリント基板10の表面に形成された一対のランド部20,20にリフロー半田付けした実装基板1において、発光素子基板12は、平面視で略矩形状の基板本体31の4隅を切り欠いて形成された端面に端面電極を備え、ランド部20は、基板本体31の下面電極が載置される基部と、この基部に連なり、各端面電極に対応する位置から、発光素子基板12の長手方向の中心線Mから斜めに離れる方向へそれぞれ延出する延出部とを備えた。

(もっと読む)

実装方法

【課題】回路基板の実装面に設けられた実装用ランドの面積を大きくせずとも、十分な量のはんだペーストを供給して、電子部品と回路基板との間のはんだ不足による接続不良を低減することのできる技術を提供する。

【解決手段】電子部品の複数のバンプ接続用はんだボール電極にはんだペーストを転写により塗布すると共に、実装面1aの凹んでいる部分や、内部電極パターン5の積層方向における配線密度が小さく回路基板1の厚みが薄くなって窪みが生じるおそれのある部分、回路基板1または電子部品の反りにより回路基板1および電子部品間の間隔が大きい位置に設けられた実装用ランド2に、はんだペーストを塗布することにより、回路基板1の実装用ランド2の面積を大きくせずとも十分な量のはんだペーストを供給して、電子部品と回路基板1との間のはんだ不足による接続不良を低減することができる。

(もっと読む)

電子部品及び基板モジュール

【課題】低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【解決手段】積層体11は、コンデンサを形成している容量導体18,19及び内部導体32を内蔵している。外部電極12a,12bはそれぞれ、容量導体18,19に引き出し導体20,21を介して接続されている。内部導体32は、容量導体18,19に対向している。外部電極13,14は、引き出し導体22,23を介して容量導体18に接続されている。外部電極15,16は、引き出し導体24,25を介して容量導体19に接続されている。

(もっと読む)

1 - 20 / 382

[ Back to top ]