Fターム[5F003BE08]の内容

バイポーラトランジスタ (11,930) | エミッタ (1,226) | リード引出し (171)

Fターム[5F003BE08]に分類される特許

1 - 20 / 171

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

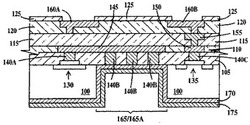

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置の製造方法

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、窒化シリコン(SiN)からなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲からベース電極111の上面にかけて(渡って)窒化シリコンからなる第2絶縁層109が形成されている。第2絶縁層109は、第1絶縁層108の側面、レッジ構造部105aとベース電極111との間のベース層104の上、およびベース電極111の上面を覆うように形成されている。基板101の平面方向において、レッジ構造部105aの外形は第1絶縁層108の外形と同じに形成されている。また、エミッタメサより離れる方向のベース電極111の外周部分が、第1絶縁層108の外周部分に重なって形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBT(ヘテロジャンクション・バイポーラトランジスタ)による段差を低減し、接合面積をより小さくできる製造方法を提供する。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層108と、第1半導体層102の上に接して形成され、エミッタ層103およびコレクタ層108に挟まれて配置された第2導電型のInGaAsからなるベース層105とを備える。また、半絶縁性のInPからなる第1分離層106aおよび第2分離層106bを備える。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTによる段差を低減し、接合面積をより小さくできるようにする。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成された第2導電型のInGaAsからなるベース層106と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層107とを少なくとも備える。加えて、エミッタ層103,ベース層106,およびコレクタ層107は、これらの順に第1半導体層102の平面上で配列して接続されている。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法、及びヘテロ接合バイポーラトランジスタを用いた電力増幅器

【課題】InGaPをエミッタ層として有し、熱的安定性と通電に対する信頼性を両立することの出来るHBTを用いた電力増幅器を提供する。

【解決手段】InGaPエミッタ層を有するHBTにおいて、InGaPエミッタ層5とAlGaAsバラスト抵抗層7の間にGaAs層6を挿入し、ベース層4から逆注入された正孔がAlGaAsバラスト抵抗層7まで拡散、到達することを抑制する。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

SiC結晶成長層の製造方法およびバイポーラ型半導体素子

【課題】層厚さが厚くてもSiC結晶中にある炭素空孔を低減できるSiC結晶成長層の製造方法を提供する。

【解決手段】SiC結晶成長層としてのドリフト層23を成長させる工程内に、シリコン原料ガスであるシランと炭素原料ガスであるプロパンのうちのプロパンのみを結晶成長表面に供給する第2の期間を設けている。このことで、結晶成長表面の炭素の過飽和度を上げ、成長途中の表面に過剰な格子間炭素を発生させる。これにより、成長後のSiC結晶成長層としてのドリフト層23の表面から離れている比較的深い箇所での炭素空孔を減少させることができる。

(もっと読む)

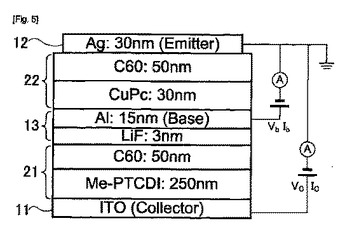

電流増幅型トランジスタ素子及び電流増幅型発光トランジスタ素子

電流増幅型トランジスタ素子には、エミッタ電極とコレクタ電極との間に、有機半導体層が2層とシート状のベース電極とが設けられている。一方の有機半導体層は、エミッタ電極とベース電極との間に設けられた、p型有機半導体層とn型有機半導体層とのダイオード構造を有する。前記電流増幅型トランジスタ素子と、その中に形成された有機EL発光素子部とを含む電流増幅型発光トランジスタ素子も開示されている。  (もっと読む)

(もっと読む)

1 - 20 / 171

[ Back to top ]