Fターム[5F004AA05]の内容

半導体のドライエッチング (64,834) | 目的 (7,312) | 選択性の向上 (1,192) | エッチング条件の改良 (423)

Fターム[5F004AA05]に分類される特許

161 - 180 / 423

透明導電膜のパターニング方法

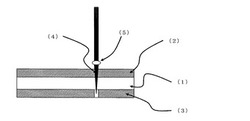

【課題】タッチパネルやPDP、LCDやELディスプレイ材料、太陽電池の透明電極や裏面電極、ハイブリッド型太陽電池の透明中間層、化合物半導体高速デバイスに用いる低誘電率膜、表面弾性波素子、赤外線カットなどを目的として、基材の両面に透明電極が形成された透明導電膜のパターニングの方法を提供する。

【解決手段】基材1の両面に透明電極層2,3が形成された透明導電膜のパターニングにおいて、YAGまたはYVO4レーザー4の基本波または第2高調波を用いることで、片面のみの精度の高いパターニングが可能となる。

(もっと読む)

ドライエッチング方法

【課題】シリコンのエッチング加工において、マイクロトレンチの発生を防止し、更には垂直加工形状およびマスク選択比の向上をも図ること。

【解決手段】真空可能なチャンバ10内に配置されたサセプタ12上にシリコン基板Wを載置し、チャンバ10内でエッチングガスを放電させてプラズマを生成し、サセプタ12にイオンを引き込むための第1の高周波RFLを印加する。エッチングガスには、Cl2ガスおよびO2ガスを含む混合ガスを用いる。

(もっと読む)

ドライエッチング方法

【課題】シリコン基板のエッチング加工、特に立体型構造体を作製するためのエッチング加工において、マスク選択比の向上を可能とし、さらには高選択性と垂直加工形状との両立を可能とするドライエッチング方法を提供する。

【解決手段】真空可能なチャンバ10内に配置されたサセプタ12上にシリコン基板Wを載置し、チャンバ10内でエッチングガスを放電させてプラズマを生成し、サセプタ12にイオンを引き込むための第1の高周波RFLを印加する。そして、自己バイアス電圧の絶対値を280V以下に選び、圧力(mTorr)をx、サセプタ12におけるバイアスRFパワー密度(ワット/cm2)をyとすると、y<8x+120の関係が満たされるようにする。

(もっと読む)

ドライエッチング方法

【課題】シリコン基板のエッチング加工において、側壁ダメージの防止、マイクロトレンチの防止および垂直形状加工を両立させる。

【解決手段】真空可能なチャンバ10内に配置されたサセプタ(下部電極)12上にシリコン基板Wを載置し、チャンバ10内でエッチングガスを放電させてプラズマを生成し、サセプタ12にイオンを引き込むための第1の高周波RFLを印加する。そして、チャンバ10内の圧力を1mTorr〜100mTorrに選び、圧力(mTorr)をx、サセプタ12に生成される自己バイアス電圧(ボルト)の絶対値をyとすると、y≧−1.7x+295の関係が満たされるようにする。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】重ね合わせ露光を行うことなくリソグラフィ・プロセスを用いて、露光装置の解像限界を超えるような微細パターンを形成する。

【解決手段】パターン形成方法は、ウエハW上にネガレジスト3及びより高感度のポジレジスト4を塗布することと、ウエハWのポジレジスト4及びネガレジスト3をライン・アンド・スペースパターンの像で露光することと、ポジレジスト4及びネガレジスト3をウエハWの表面の法線に平行な方向に現像することとを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】有機シロキサンを主成分とする絶縁膜にエッチング処理によって凹部を形成する際に、凹部の底部に異常形状が形成されるのを抑制する。

【解決手段】層間絶縁膜を構成する有機シロキサンを主成分とする有機絶縁膜2に形成された溝や孔等のような凹部4内に導体膜を埋め込むことで埋込配線構造を構成する半導体集積回路装置の製造方法において、有機絶縁膜2上にフォトレジスト膜3を形成した後、そのフォトレジスト膜3をエッチングマスクとして有機絶縁膜2に溝や孔等のような凹部4を形成する際に、その凹部4の底部に異常形状が形成されるのを抑制するために、CF系のガス/N2/Arガスを用いたプラズマドライエッチング処理を施すことにより凹部4を形成した。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスクを用いて選択形成したトレンチに、ハードマスクを残した状態でエピタキシャル層を埋め込む際に、結晶欠陥の発生を防ぐとともに、超接合構造を効率良く形成でき、良好な良品率が得られる半導体装置の製造方法を提供すること。

【解決手段】トレンチ4を形成するためのマスクとなるマスク絶縁膜3が少なくとも前記トレンチ形成用開口部6d周辺で、他の部分より薄い膜厚部分を有し、前記トレンチ4にp型エピタキシャル半導体層5を埋め込む前に、前記マスク絶縁膜3の膜厚の薄い部分をエッチングして除去した後に、前記トレンチ4にp型エピタキシャル半導体層5を埋め込む。

(もっと読む)

シリコン含有膜のエッチング方法および装置

【課題】下地膜のエッチングを抑制しつつ、シリコン含有膜を残渣無く、かつ高レートでエッチングする。

【解決手段】フッ素系反応成分を含む処理ガスを被処理物90に接触させ、下地膜92上のシリコン含有膜93をエッチングする。フッ素系反応成分は、フッ素系原料(CF4)を含むフッ素系原料ガスを大気圧近傍のプラズマ空間43に通して生成する。原料含有率調節部37によってフッ素系原料ガス中のフッ素系原料の含有率をエッチングの進行に応じて変化させる。

(もっと読む)

半導体処理装置及び処理方法

【課題】いかなる濃度イオン注入がなされているレジストであってもアッシングできるようにする。

【解決手段】チャンバー7によって、レジストが塗布されているウェハに紫外光を照射する。チャンバー5によって、ウェハをオゾンガスに接触させてアッシングする。チャンバー6によって、レジストの成分に対応する半導体ガスを接触させる。チャンバー7によって、紫外光を照射したウェハに対してオゾンガスを接触させる。

(もっと読む)

半導体加工方法

【課題】高誘電率絶縁膜上に金属膜及び多結晶Siを堆積した構造の半導体を垂直にかつ微細に加工する。

【解決手段】半導体基板上に形成されたHfあるいはZrを含む絶縁膜102、該絶縁膜上に並置して形成された互いに仕事関数が異なる第1および第2の金属膜103,104、該第1および第2の金属膜上に堆積して形成した多結晶シリコン膜105を有し、該多結晶シリコン膜上に形成したレジスト108を用いて、プラズマ雰囲気中で前記多結晶シリコン膜並びに前記第1および第2の金属膜をエッチング加工する半導体加工方法において、前記前記複数種の金属膜上の多結晶シリコン膜のうちエッチング終了が早い方である第2の金属膜上の多結晶シリコン膜のエッチング終了後は、前記処理ガスとして、HBrおよび酸素を含むガスを用いる。

(もっと読む)

半導体装置およびその製造方法、並びにプラズマエッチング装置

【課題】化合物半導体をエッチングにより加工して高アスペクト比の微細構造を高精度に形成し得る半導体装置の製造方法を提供する。

【解決手段】この製造方法は、インジウムおよびリンを必須の構成元素とする化合物半導体からなる被加工物10上にエッチングマスク11pを形成する工程と、エッチングマスク11pの形成後、プラズマエッチング装置のチャンバ内に配置された被加工物10の上に、ヨウ化水素ガスおよび塩素ガスの2成分からなる混合ガスを導入しこの混合ガスをプラズマ化する工程と、当該プラズマ化された混合ガスを被加工物10に入射させて被加工物10を選択的にエッチングする工程とを含む。ヨウ化水素ガスおよび塩素ガスの2成分の総流量に対するヨウ化水素ガスの流量の配合比が70%以上である。

(もっと読む)

ガリウムで汚染された層の電子ビーム誘起エッチング方法

本発明は、ガリウムで汚染された層(120),(220)の電子ビーム誘起エッチング方法に関する。本方法は、エッチングガスとして、少なくとも1種類の第1ハロゲン化合物を、電子ビームが層(120),(220)に衝突する位置に供給する方法ステップ、および、ガリウムを同位置において除去する前駆体ガスとして、少なくとも1種類の第2ハロゲン化合物を供給する方法ステップ、を含むものである。 (もっと読む)

金属ゲート構造への多層/多入力/多出力(MLMIMO)モデルの使用方法

【課題】 本発明はウエハ処理に関する。

【解決手段】 本発明は、1つ以上の測定処理、1つ以上のポリエッチング(P-E)処理及び1つ以上の金属ゲートエッチング処理を有する多層処理手順並びに多層/多入力/多出力(MLMIMO)モデル及びライブラリを用いてウエハを処理する方法を供する。前記MLMIMO処理制御は、多数の層及び/又は多数の処理工程間での動的に相互作用する挙動のモデル化を用いる。前記多数の層及び/又は多数の処理工程は、等方性及び/又は異方性エッチング処理を用いて作製可能なライン、溝、ビア、スペーサ、コンタクト、及びゲート構造の作製に関連づけられて良い。

(もっと読む)

フォーカスリング及び基板載置台、並びにそれらを備えたプラズマ処理装置

【課題】ウェハのプロセス特性差の改善を図るとともに、フォトレジスト膜が各処理プロセスにおいて、所定量の残膜として維持され、酸化膜に対する選択比の低下を防止できるフォーカスリングを提供する。

【解決手段】被処理基板15を載置する基板載置台2上で被処理基板15を囲む位置に配置され、前記被処理基板15に対してプラズマ処理を施す際にプラズマを前記被処理基板に集束させるフォーカスリング5において、前記被処理基板のプラズマ処理中において、全周にわたって、その径方向外側領域が高温領域となり、径方向内側領域が低温領域となるよう、前記径方向内側領域と前記基板載置台2との間に熱伝達手段を設けるとともに、前記径方向外側領域と前記径方向内側領域との間に全周にわたって溝を設ける。

(もっと読む)

赤外線センサ素子の製造方法

【課題】積層膜の剥離の発生を防止ししつつ所望の中空構造を容易に形成することができる赤外線センサ素子の製造方法を提供することを目的とする。

【解決手段】

SOI基板準備工程と、SOI基板に熱検出部及びこれ電気的に接続される配線を形成する熱検出構造形成工程と、少なくとも窒化シリコン膜を含む絶縁層を形成する絶縁層形成工程と、絶縁層上にガス流入開口を含む赤外線受光部形成する受光部形成工程と、SOI基板に到達する貫通孔を形成する貫通孔形成工程と、貫通孔を介してエッチングを施すことによって半導体基板に空隙を形成する空隙形成工程と、を有し、貫通孔形成工程において窒化シリコン膜を露出することなく貫通孔を形成する。

(もっと読む)

プラズマ処理装置システムの制御装置、プラズマ処理システムの制御方法および制御プログラムを記憶した記憶媒体

【課題】レシピの管理を簡略化する。

【解決手段】装置コントローラECは、プラズマ処理の手順を示した基準レシピ300を記憶する記憶部250と、少なくとも複数ロットの処理間隔を置いて所定のタイミングに複数のプロセスモジュールPM内の状態の変動値を演算する演算部260と、演算部260により演算されたプロセスモジュールPM内の状態の変動値から基準レシピ300を調整するための調整テーブル310a,310bをプロセスモジュールPM毎に生成するテーブル生成部265と、テーブル生成部265により生成されたプロセスモジュールPM毎の調整テーブル310a,310bを用いて基準レシピ300を調整し、調整された基準レシピ300の手順に従いプロセスモジュールPMにてウエハをプラズマ処理する処理実行制御部270と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

シリコン構造体の製造方法及びその製造装置並びにその製造プログラム

【課題】エッチングストップ層を有するシリコンの異方性ドライエッチングにおいて、高い垂直性とともに、良好な側壁形状を達成する。

【解決手段】本発明のシリコン構造体の製造方法は、いわゆるガススイッチングによるドライエッチングの過程で、高速エッチング条件を用いてエッチングする工程(a)により、そのシリコン領域のうち最もエッチング速度の速い場所が前記エッチングストップ層までエッチングされる前に、高速エッチング条件のエッチング速度から時間の経過とともにエッチング速度が低下する遷移エッチング条件を用いたエッチング工程(b)を経て、遷移エッチング条件のうち最もエッチング速度の遅い条件のエッチング速度を持つ低速エッチング条件を用いて前記シリコン領域をエッチングする工程(c)を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】内部に形成されるキャパシタの特性を向上することができる強誘電体メモリ等の半導体装置を提供する。

【解決手段】半導体基板の上方の絶縁膜18上に形成されるキャパシタ下部電極20qと、キャパシタ下部電極20qの上に形成されるキャパシタ誘電体膜21qと、誘電体膜21qの上に形成されるキャパシタ上部電極22qとを有するキャパシタQであって、キャパシタ上部電極22qの側面のうち半導体基板の上面に対する下部側面の第1の角度を上部側面の第2の角度より小さくしている。これにより、キャパシタ上部電極とその下の誘電体膜を覆う保護絶縁膜をカバレッジ良く形成することができる。カバレッジ良く形成された保護絶縁膜は、キャパシタ保護機能が高くなるので、キャパシタの還元元素による劣化を防止して、キャパシタ特性を向上することができる。

(もっと読む)

GaN系半導体素子及びその製造方法

【課題】 歩留まりを高めることが可能なGaN系半導体素子及びその製造方法を提供する。

【解決手段】 本発明によるGaN系半導体素子の製造方法は、GaN系半導体層(2〜4)の積層体9を、所定深さまでドライエッチングによりエッチングするGaN系半導体素子10の製造方法であって、エッチング装置内の到達真空度を2×10−3Pa以下にした後、反応ガスを供給することにより所定圧力まで高めた状態で、ドライエッチングにより積層体9をエッチングする。

(もっと読む)

161 - 180 / 423

[ Back to top ]